隨著業界對增加電晶體密度、頻寬和(hé)降低功耗的(de)需求越來越迫切,許多(duō) IC 設計和(hé)封裝團隊都在深入研究如何增加垂直堆疊多(duō)個晶片裸片 (die) 和(hé)小晶片 (chiplet) 的(de)方案。而這種被稱為 3D-IC 的(de)技術有望實現許多(duō)超越傳統單裸片在單平面設計的(de)優勢。透過堆疊裸片和(hé)使用(yòng)先進的(de)封裝技術進行整合,設計師能夠在更小的(de)區域面積中添加更多(duō)功能,同時提高(gāo)單位性能並降低開發與生產成本。

3D-IC 架構可(kě)以將多(duō)個同質和(hé)異質的(de)裸片/小晶片 Chiplet (例如邏輯、記憶體、類比和(hé)射頻功能) 整合到同一設計中。這為系統級晶片 (SoC) 的(de)整合提供了(le)一個替代方案,支援設計人(rén)員希望整合在單一設計中的(de)所有功能,並因此節省在新的(de)制程節點重新設計這些功能而花費的(de)昂貴成本。

本白皮書為 PDF 版本,全長 7 頁,除了(le)介紹 3D-IC 技術之外,也(yě)將探討設計挑戰、生態系統要求和(hé)所需的(de)解決方案。

本書重點

|

近距離分(fēn)析 3D-IC |

|---|---|

|

3D-IC 設計挑戰與設計需求 |

|

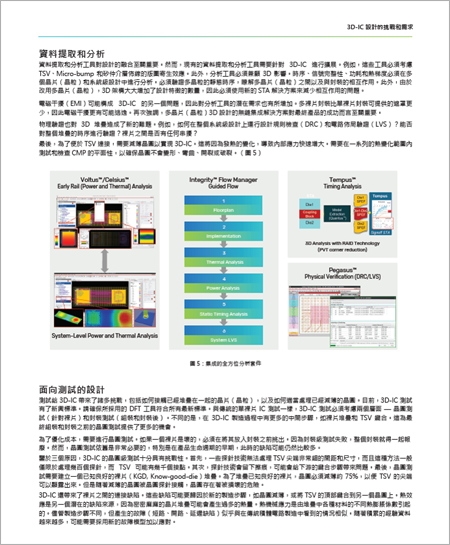

資料提取和(hé)分(fēn)析 |

|

面向測試的(de)設計 |

|

打造 3D-IC 生態系統 |

更多(duō)電子書免費下(xià)載

|

|

|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

中文版授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」