設計同步分(fēn)析 無縫銜接 PCB 設計與 SI / PI 分(fēn)析

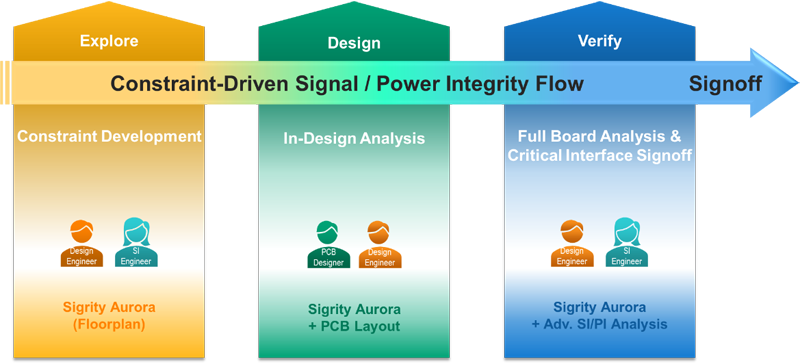

Cadence® Sigrity™ Aurora 爲布局前、設計中、以及布局後的(de) PCB 設計提供設計同步信号和(hé)電源完整性分(fēn)析。集成 Cadence Allegro® 的(de) PCB 編輯和(hé)布線技術,Sigrity Aurora 用(yòng)戶能夠在設計周期的(de)早期,通(tōng)過假設分(fēn)析,設置更精确的(de)設計約束、減少設計叠代。

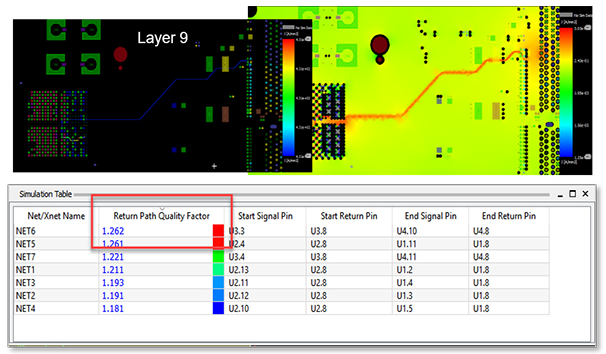

Sigrity Aurora 可(kě)直接在 Allegro PCB 數據庫中進行讀寫,從而快(kuài)速準确地集成設計與分(fēn)析結果。并提供基于 SPICE 的(de)仿真器和(hé) Sigrity 專利的(de)嵌入式混合場(chǎng)求解器,提取 2D 和(hé) 3D 結構。必要時(shí),可(kě)支持帶電源影(yǐng)響的(de) IBIS(行爲)模型,以及晶體管級模型。并行總線和(hé)串行通(tōng)道架構可(kě)以在布局前進行探索、比較備選方案;在布局後對(duì)所有相關信号進行全面分(fēn)析。

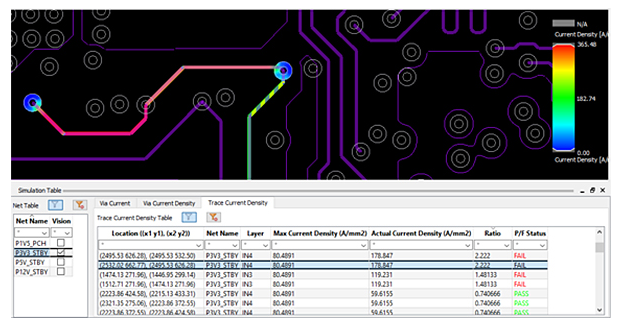

直流電源完整性分(fēn)析可(kě)測量電源和(hé)負載之間的(de)任一電壓降。其結果可(kě)在設計窗(chuāng)口中以電壓、壓降、或電流密度的(de)可(kě)視化(huà)方式呈現。設計人(rén)員(yuán)可(kě)任意更改設計,并快(kuài)速了(le)解設計變更造成的(de)影(yǐng)響;而無需離開 Allegro PCB 設計接口。

盡早發現設計錯誤,減少設計返工、提高(gāo)一次性設計成功率,加速設計成功的(de)同時(shí),降低産品成本!

主要特點

|

通(tōng)過軟件自帶工作流程,在約束驅動流程中引導用(yòng)戶設計同步進行包括:壓降、阻抗、耦合、串擾、回流路徑以及反射等分(fēn)析信号完整性 / 電源完整性,無縫銜接 PCB 設計與仿真分(fēn)析 |

|---|---|

|

|

|

不需信号完整性模型即可(kě)快(kuài)速篩查設計中的(de)信号完整性問題 |

|

實現在 Allegro system capture 接口中進行拓撲結構的(de)電路仿真假設分(fēn)析,在設計早期階段探索拓撲結構備選方案 |

|

通(tōng)過參數掃描探索分(fēn)析,提高(gāo)産品性能 |

|

用(yòng)戶可(kě)加入 Allegro PCB Symphony Team Design 多(duō)人(rén)實時(shí)上線協同設計時(shí),同步進行 SI / PI 分(fēn)析,而無需添加設計副本 |