射頻(pín) / 微波電路設計軟件

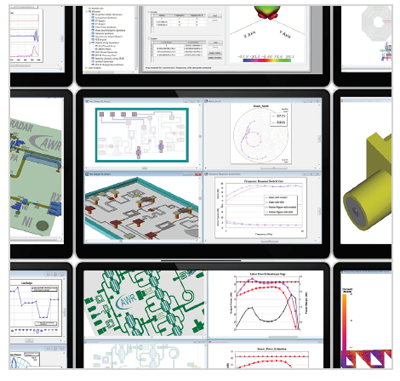

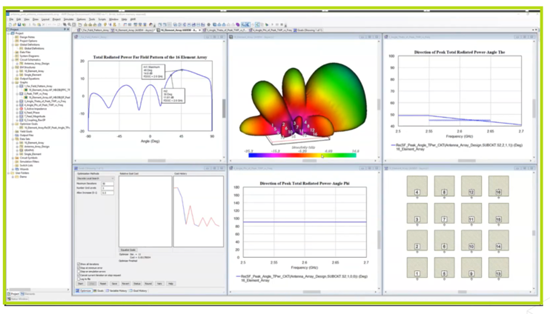

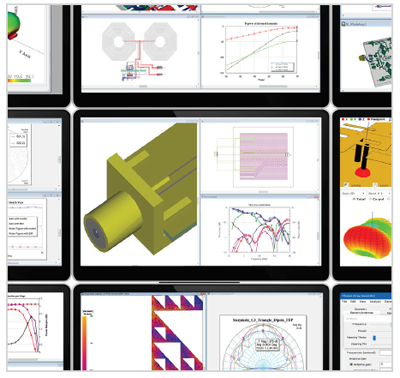

Cadence® AWR® Microwave Office® 廣泛被使用(yòng)于領先制造商,用(yòng)于加速高(gāo)頻(pín)電子産品的(de)開發。該軟件擁有直觀的(de)接口、創新的(de)設計自動化(huà)和(hé)強大(dà)的(de)諧波平衡 (harmonic-balance) 電路仿真功能,可(kě)提高(gāo)工程效率并加快(kuài)設計周期。AWR Microwave Office 的(de) Cadence AWR Design Environment® 平台将 Cadence AWR Visual System Simulator™ (VSS) 系統設計、Cadence AWR AXIEM® 以及 Cadence AWR Analyst™ 電磁 (EM) 仿真軟件工具無縫集成,提供完整的(de)射頻(pín)、微波電路、系統和(hé)電磁協同仿真環境。

AWR 專有的(de)統一數據庫直接鏈接原理(lǐ)圖和(hé)設計布局,以其可(kě)以同時(shí)進行物(wù)理(lǐ)設計與電氣仿真。強大(dà)的(de)設計自動化(huà)和(hé)輔助工具 (如濾波器、混頻(pín)器、無源器件、傳輸線和(hé)匹配網絡合成) 設計人(rén)員(yuán)還(hái)可(kě)進一步改進和(hé)優化(huà)合成濾波器、阻抗匹配、混頻(pín)器和(hé)被動組件電路,并進行電磁驗證和(hé)物(wù)理(lǐ)設計。加上用(yòng)于功率放大(dà)器設計的(de)業内領先負載拉移分(fēn)析,爲産品開發的(de)各個(gè)階段提供了(le)關鍵支持。

快(kuài)速準确的(de)仿真技術提供強大(dà)的(de)電路分(fēn)析功能和(hé)設計洞見,提供了(le)正确表征和(hé)優化(huà)高(gāo)頻(pín)電子設備所需的(de)線性 / 非線性時(shí)域和(hé)頻(pín)域量測。

AWR 綜合資源庫中包含來(lái)自領先 MMIC / RFIC 代工廠的(de)高(gāo)頻(pín)分(fēn)布式傳輸模型、表面貼裝供貨商的(de)組件和(hé)制程設計套件 (PDK),再加上強大(dà)的(de)合成模塊和(hé)設計輔助向導加快(kuài)設計啓動的(de)速度,可(kě)根據用(yòng)戶指定的(de)射頻(pín) / 微波性能标準,從供貨商提供的(de)資源庫和(hé)代工廠授權用(yòng)于 PCB 和(hé) MMIC 設計的(de) PDK 建立阻抗匹配網絡,有助于在制造之前對(duì)設計進行精确仿真,從而減少設計叠代并加快(kuài)設計速度。

主要特點

|

原理(lǐ)圖 / 布局 — 同步原理(lǐ)圖 / 布局設計輸入,并提供業内領先的(de)調諧功能 |

|---|---|

|

APLAC — 線性和(hé)非線性諧波平衡電路仿真 |

|

電磁分(fēn)析 — 利用(yòng) AWR AXIEM 和(hé) AWR Analyst 工具實現完全集成的(de)電磁 (EM) 分(fēn)析 |

|

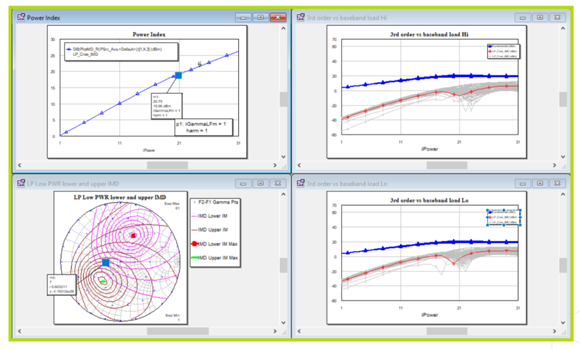

負載拉移 — 最先進的(de)負載拉移分(fēn)析,帶有諧波和(hé) video-band 調諧功能 |

|

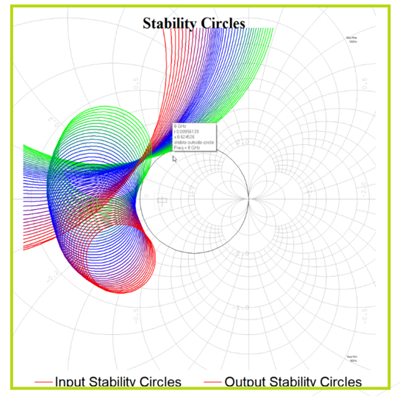

穩定性 — 快(kuài)速、嚴謹的(de)新型環路電路包絡分(fēn)析,可(kě)實現多(duō)級并平衡放大(dà)器的(de)穩定性 |

|

DRC / LVS — 設計規則檢查 / 布局與原理(lǐ)圖 |

設計輸入

直觀的(de)使用(yòng)者界面經過定制,可(kě)爲高(gāo)頻(pín)電路提供項目管理(lǐ)和(hé)設計輸入,使設計人(rén)員(yuán)能夠利用(yòng)完整的(de)組件庫快(kuài)速的(de)構建電路。藉由便利的(de)調諧 / 優化(huà)功能使電路、系統、EM 協同仿真能夠符合電路标準和(hé)用(yòng)戶自定義 RF / 微波測量規格。

自動化(huà)

強大(dà)的(de)自動化(huà)功能可(kě)加快(kuài)設計的(de)進度并電路和(hé)測量數據,其中包括便捷的(de)向導工具 (可(kě)從第三方工具導入 PCB 布局和(hé) / 或 OpenAccess 數據) 以及易于使用(yòng)的(de)強大(dà)的(de)應用(yòng)程序設計界面 (API) 和(hé)腳本功能,旨在支持自定義和(hé)用(yòng)戶定義的(de)自動化(huà)。

負載拉移分(fēn)析 (Load-Pull Analysis)

用(yòng)戶可(kě)以根據測量或仿真資料,使用(yòng)複雜(zá)的(de)掃頻(pín)負載拉移數據集輕松開發放大(dà)器的(de)輸入 / 輸出匹配電路。性能等高(gāo)線圖包括可(kě)用(yòng)的(de)輸出功率、增益、功率附加效率 (PAE)、雙音(yīn)互調失真和(hé)其他(tā)關鍵放大(dà)器性能指針。

仿真技術

穩健的(de) AWR APLAC® A 諧波平衡 (HB) 仿真器利用(yòng)強大(dà)的(de)多(duō)速率 HB、瞬時(shí)輔助 HB 和(hé)時(shí)變 (電路包絡) 分(fēn)析,并支持大(dà)規模和(hé)高(gāo)度非線性的(de)射頻(pín) / 微波電路,進而提供線性和(hé)非線性電路分(fēn)析。

AWR AXIEM

電磁仿真器可(kě)提供所需的(de)速度和(hé)精度,以便對(duì)無源結構、傳輸線、平面天線和(hé)大(dà)型 (超過 100K 個(gè)未知數) 貼片數組進行特性分(fēn)析和(hé)優化(huà)。

AWR Analyst

仿真器有助于加快(kuài)從早期物(wù)理(lǐ)設計表征到完整三維電磁驗證的(de)高(gāo)頻(pín)産品開發流程。其三維有限元求解器可(kě)以對(duì)打線接合 (bondwires)、過孔 / 過孔栅欄 (vias / via fencing) 和(hé)球栅數組封裝 (BGA) 等互連結構進行快(kuài)速、準确的(de)電磁分(fēn)析。

應用(yòng)和(hé)技術

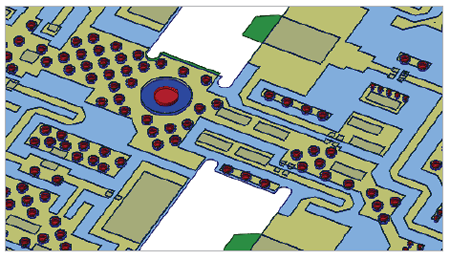

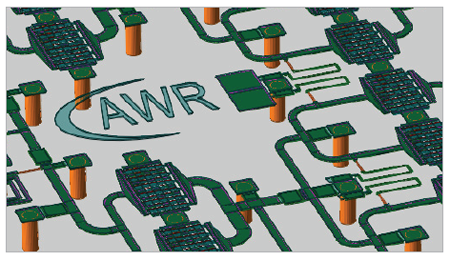

MMIC

AWR 提供微波集成電路 (MMIC) 完整前端到後端設計的(de)流程,擁有創新的(de)用(yòng)戶接口,并且完全集成了(le)設計輸入、仿真和(hé)物(wù)理(lǐ)設計工具,有效提高(gāo)工程效率,并确使用(yòng)各種制程,如砷化(huà)镓 (GaAs)、氮化(huà)镓 (GaN)、矽鍺 (SiGe) 制程以及 CMOS 的(de)代工廠夥伴的(de) PDK 進行産品開發時(shí)能夠一次就完成正确的(de)生産。而階層式的(de)框架也(yě)支持在多(duō)芯片射頻(pín)模塊中對(duì)多(duō)種 MMIC、RFIC 和(hé) PCB 制程工藝、多(duō)層互連、嵌入式被動組件以及微型表面貼裝器件進行仿真。

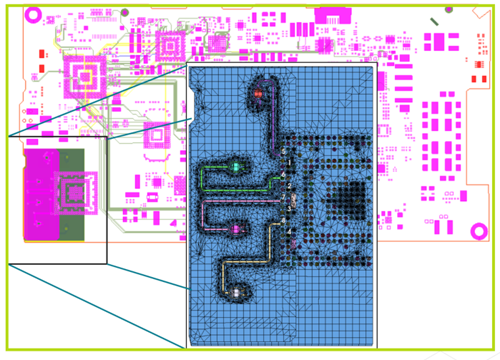

PCB

對(duì)射頻(pín)信号路徑到數字控制和(hé) DC 偏壓路徑在内的(de)傳輸介質進行精确建模,可(kě)以不斷增強 PCB 的(de)功能。電路 / 系統和(hé)電磁協同仿真可(kě)對(duì)表面貼裝器件、互連傳輸線以及嵌入式和(hé)分(fēn)布式被動組件進行完整的(de) PCB 分(fēn)析以及電磁驗證。集成平台支持并行的(de)電子 / 物(wù)理(lǐ)設計以及電路 / 系統 / 電磁協同仿真,實現真正一站式産品設計。藉助電磁協同仿真功能實現 PCB 射頻(pín)設計,提高(gāo)準确性,确保設計在更短時(shí)間内通(tōng)過驗證。

模塊

多(duō)技術集成功能可(kě)爲多(duō)種技術進行建模,且分(fēn)層框架支持在多(duō)芯片射頻(pín)模塊中對(duì)多(duō)種 MMIC、RFIC 和(hé) PCB 工藝、多(duō)層互連、嵌入式被動組件以及微型表面貼裝設備進行仿真。設計自動化(huà)可(kě)提供用(yòng)于模塊實現的(de)智能工作流程,從而加速産品開發。而電磁仿真和(hé)設計驗證可(kě)提高(gāo)準确性,确保設計在更短時(shí)間内通(tōng)過驗證。集成平台支持并行的(de)電子 / 物(wù)理(lǐ)設計以及電路、系統和(hé)電磁協同仿真,實現真正一站式産品設計。