全球最多(duō)人(rén)使用(yòng)的(de)設計輸入方案

Cadence® OrCAD™ X Capture 原理(lǐ)圖輸入系統具有快(kuài)捷、通(tōng)用(yòng)的(de)設計輸入能力,爲全球最廣受歡迎的(de)設計輸入工具。它針對(duì)設計一個(gè)新的(de)電子電路、修改現有的(de)一個(gè) PCB 的(de)原理(lǐ)圖或者繪制一個(gè) VHDL 模塊的(de)方框圖都提供了(le)所需要的(de)全部功能,并能迅速驗證您的(de)設計。

Cadence OrCAD X Capture 作爲設計輸入工具,運行在 PC 平台,用(yòng)于 FPGA 、 PCB 和(hé) Cadence® OrCAD™ PSpice® 設計應用(yòng)中,是業界第一個(gè)真正基于 Windows 環境的(de)原理(lǐ)圖輸入程序,易于使用(yòng)的(de)功能及特點已使其成爲原理(lǐ)圖輸入的(de)工業标準。

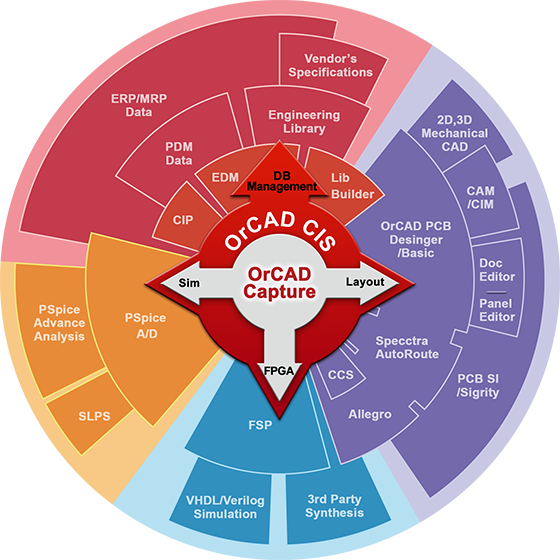

OrCAD 産品關系圖

1. 單一化(huà)的(de)設計窗(chuāng)口

OrCAD™ X Capture 的(de)電路設計可(kě)支持從最簡單到最複雜(zá)的(de)平面或分(fēn)層設計,并且可(kě)經由網絡表連接Cadence® OrCAD™ PCB Editor、Cadence® Allegro® 或其它的(de) Layout 軟件來(lái)完成 PCB 設計;也(yě)集成了(le) PSpice 與 VHDL (NC Verilog) 的(de)環境---提供您做(zuò)仿真與數字 (FPGA Design Flow) 前端設計平台。另外也(yě)可(kě)以配合 OrCAD PCB SI 與 Cadence® Allegro® SI 來(lái)解決高(gāo)頻(pín)問題。

2. 利用(yòng) Windows 操作接口可(kě)以更方便的(de)編輯與分(fēn)享彼此的(de)構想

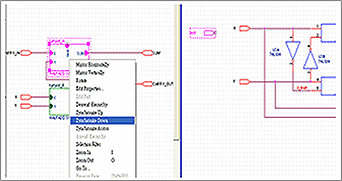

OrCAD X Capture 利用(yòng) Windows 簡易操作的(de)觀念,可(kě)用(yòng)剪下(xià)、複制、貼上等等的(de)特色來(lái)操作;也(yě)可(kě)以利用(yòng) Windows 的(de)多(duō)重編輯方式來(lái)編輯兩個(gè)以上的(de)原理(lǐ)圖或是由另外的(de)檔案複制數據過來(lái)使用(yòng)。

3. 支持廣大(dà)的(de) PCB 應用(yòng)

OrCAD X Capture 可(kě)以支持 30 種以上 PCB Layout 軟件的(de)網絡表格式,包含 OrCAD PCB Editor、Allegro、Pads、PCAD 200X、Protel、Mentor Graphics BoardStation…等等。

4. 集成了(le) Cadence 其他(tā)系統程序來(lái)處理(lǐ)不同的(de)需求

OrCAD X Capture 是 OrCAD PSpice、OrCAD PCB SI、OrCAD PCB Editor、Allegro 與 Allegro SI 的(de)設計前台。透過網絡表 (netlist) 的(de)連接,可(kě)利用(yòng)它同時(shí)标示出彼此的(de)關聯處 (cross-highlighting),也(yě)可(kě)直接作爲測試的(de)信号源 (cross-probing)。而利用(yòng) Back Annotate 的(de)功能,可(kě)将 Layout 序号或 Constraint Manager 的(de)變化(huà)回饋到 Capture 的(de)原理(lǐ)圖中。

5. 提供多(duō)重的(de) PLD 設計組件與方式

OrCAD X Capture 提供六種 PLD 使用(yòng)原理(lǐ)圖的(de)元件,包含 Xilinx、Altera、Actel、Lattice、Lucent 與 Atmel 六種 Vendor 的(de)元件,這(zhè)些元件允許您利用(yòng) OrCAD X Capture 來(lái)做(zuò)爲設計 PLD 的(de)前台。

6. 可(kě)以利用(yòng) OrCAD X Capture 來(lái)完成不同的(de)仿真并提供廣大(dà)的(de) PCB 網絡表格式

可(kě)以利用(yòng) OrCAD X Capture 集成的(de)環境,來(lái)完成 FPGA Design Flow 的(de)設計 - 仿真、合成、布局的(de)功能。并繪制完整的(de)原理(lǐ)圖來(lái)連接 PCB Layout 軟件,以完成一個(gè)項目設計。

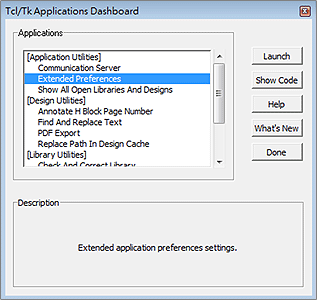

7. 可(kě)以利用(yòng) OrCAD X Capture Tcl/Tk 程序接口開發新的(de)操作功能

可(kě)以利用(yòng) OrCAD X Capture Tcl/Tk 程序,來(lái)開發或者外挂新的(de)軟件操作或檢查功能讓 OrCAD X Capture 更易于使用(yòng)。

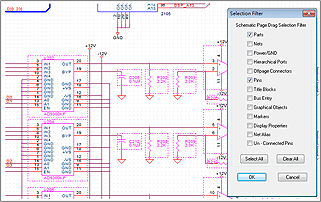

物(wù)件選擇功能,可(kě)篩選物(wù)件類型

在選擇物(wù)件時(shí),可(kě)利用(yòng)鼠标右鍵的(de) "Selection Filter" 設定可(kě)選擇的(de)物(wù)件類型,例如您隻想框選原理(lǐ)圖中的(de)元件與 Pin,就可(kě)以先全部清除隻留 Parts 和(hé) Pins 再用(yòng)鼠标框選後,就隻會選取範圍中的(de) Parts 和(hé) Pins,而不會選取到其他(tā)對(duì)象如 Nets 或其他(tā)物(wù)件。

階層式電路,同步産生 / 删除所對(duì)應的(de)連接符号

在繪制階層式電路時(shí),如果上層的(de)模塊圖有接點的(de)更新或是下(xià)階的(de)細部線路有任何外接接點的(de)增減。在以往您需設定好相對(duì)應的(de)名稱才會有其接續性,現在 Cadence® OrCAD™ 會自動依接點的(de)增減自動設定好階層式電路上下(xià)階之間的(de)對(duì)應關系,方便階層式電路的(de)實際應用(yòng)。

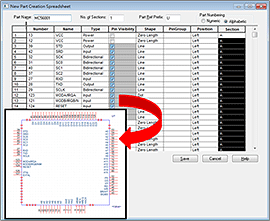

從空白表格中直接 建立零件

在建立零件時(shí)最大(dà)的(de)困難可(kě)能是要建入數百個(gè) PIN 的(de) Pin 腳号及名稱,現在可(kě)以從收到的(de)規格表中撷取所要的(de) Pin 腳号及名稱,貼入 OrCAD 中再定義其他(tā)的(de)相關訊息,如 Pin 腳所在的(de)位置等等,可(kě)快(kuài)速自動建立出此顆零件。

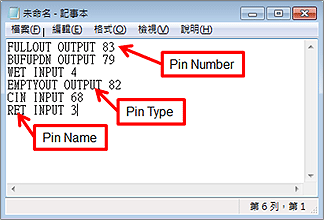

依照(zhào)原理(lǐ)圖頁面指定零件序号編排

如果可(kě)由 IC 廠商,如 Xilinx 得(de)到 零件的(de) Pin 腳數據文件,可(kě)稍做(zuò)整理(lǐ)後理(lǐ)出具有 Pin 腳名稱、Pin 腳種類、Pin 腳号的(de)文本文件,Generate Part 加載此文件後自動建立出 OrCAD 的(de)零件,不必再用(yòng)傳統方法逐一宣告,大(dà)量縮短建立零件的(de)時(shí)間。

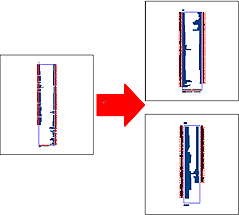

切割大(dà)顆零件

使用(yòng)表格方法或 Pin File 的(de)方式自動建立零件,要是輸入的(de) Pin 腳數太多(duō)可(kě)能會建出一顆超大(dà)的(de)零件,因爲大(dà)過圖框而不适合放到圖面上,如果想把大(dà)顆零件切割成幾顆小的(de)非同類零件,可(kě)用(yòng) Split Part 定義出切割後的(de)小零件數量及各 Pin 腳所在的(de)位置後自動生成各個(gè)非同類零件。

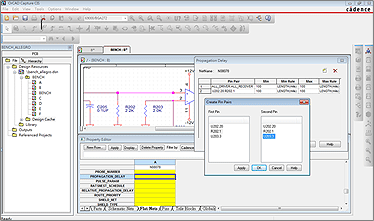

Cadence OrCAD 與 Cadence Allegro 集成

除了(le)可(kě)以在 OrCAD 原理(lǐ)圖上直接定義 Cadence® Allegro® 零件相關屬性,如 ROOM 、 Fixed 、 BOM ignore 、 …..,也(yě)可(kě)定義 Allegro 信号屬性,如 MIN_LINE_WIDTH 、 MAX_VIA_COUNT 、 …… ,現在甚至要定義 PIN PAIR 所指定的(de) U1.17 到 U2.5 的(de) PROPOGATION_DELAY 的(de)線長(cháng),都可(kě)在 OrCAD 原理(lǐ)圖中輕易實現。

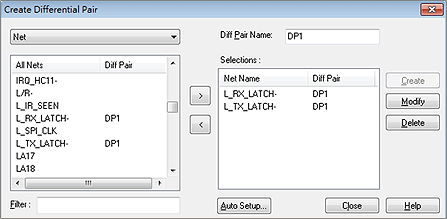

定義差分(fēn)信号

在繪圖時(shí)也(yě)可(kě)直接定義差分(fēn)信号名稱及其組成的(de)線對(duì)成員(yuán),或用(yòng) Auto Setup 定義信号名稱規則 (如後綴是+和(hé) - ) 即可(kě)由程序自動辨識定義出各個(gè)差分(fēn)信号對(duì)。

能将 OrCAD 原理(lǐ)圖上對(duì) Allegro 的(de)零件或信号宣告的(de)屬性 (properties) 以 PCB Editor 方式或用(yòng)傳統 OrCAD 轉 Allegro 的(de)方法以附帶 properties 的(de)方式轉到 Allegro 中

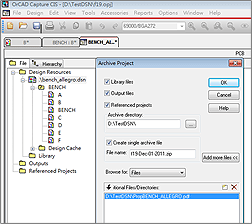

專案壓縮

在繪圖完成後,可(kě)利用(yòng) Archive Project 選擇要壓縮的(de)相關文件類型及其文件名和(hé)路徑,也(yě)可(kě)把外部的(de)文件,如零件規格、相關程序代碼等等一起壓縮成 .ZIP 文件,在項目的(de)管理(lǐ)和(hé)備份上更加便利。

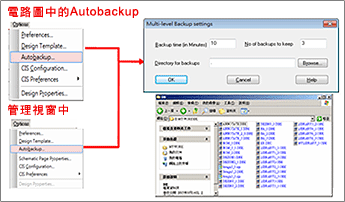

可(kě)以設定自動備份的(de)路徑、時(shí)間間隔及數量,程序會自動存成各個(gè) .DBK 的(de)備份文件

原理(lǐ)圖設定備份文件自動存盤,可(kě)協助工程師快(kuài)速地回複前一段時(shí)間所修改的(de)數據。

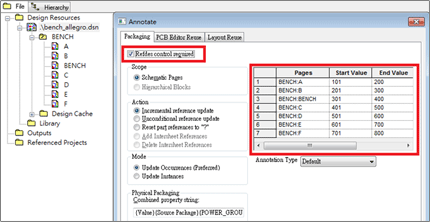

OrCAD 可(kě)依照(zhào)原理(lǐ)圖的(de)頁碼設定每頁起始的(de)零件序号及最大(dà)的(de)零件序号

原理(lǐ)圖零件序号可(kě)依照(zhào)原理(lǐ)圖的(de)頁面順序設定起始值及最大(dà)值,當零件序号要重新排列,将以設定好的(de)範圍做(zuò)零件序号的(de)編排!

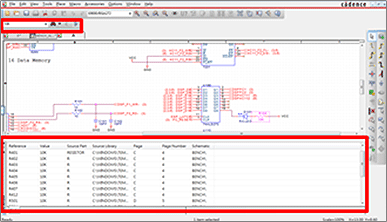

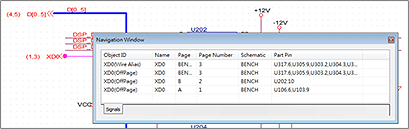

物(wù)件搜尋

更加方便的(de)物(wù)件搜尋功能,當物(wù)件搜尋後,将在畫(huà)面下(xià)方有 Find window,使用(yòng)者可(kě)透過搜尋結果點選物(wù)件,原理(lǐ)圖将直接切換并且高(gāo)亮顯示所指定物(wù)件。

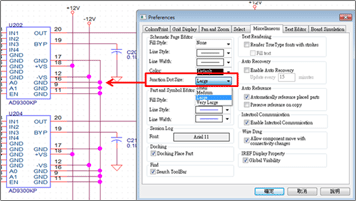

原理(lǐ)圖 Junction (節點)大(dà)小改變 - 可(kě)透過 Junction Dot Size change 的(de)功能更改原理(lǐ)圖節點的(de)大(dà)小

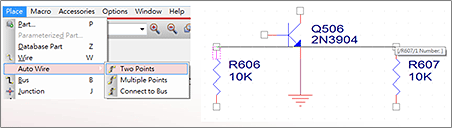

Auto wire 自動連線功能

原理(lǐ)圖 Net 自動連接功能,可(kě)讓使用(yòng)者快(kuài)速的(de)做(zuò)單點對(duì)單點 Net 的(de)連接,或單點對(duì)多(duō)點同時(shí)連接,或是針對(duì) BUS 線路的(de)連接!

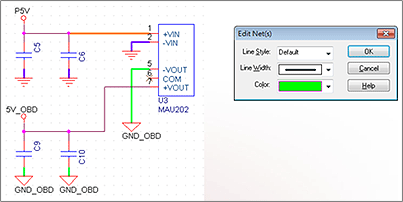

原理(lǐ)圖 Net 查找功能,可(kě)針對(duì)原理(lǐ)圖中所有與點選的(de) Net 相同的(de)線段全部列出,并透過點選的(de)方式可(kě)以跳轉到相對(duì)應的(de)頁面中

原理(lǐ)圖線段顔色及寬度的(de)改變,可(kě)針對(duì)原理(lǐ)圖重要的(de) Net 線改變其顔色、線寬、線型

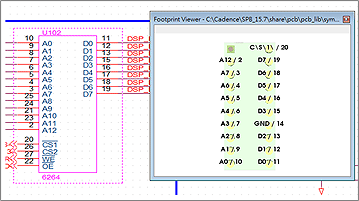

Footprint Viewer 可(kě)在原理(lǐ)圖或零件庫編輯畫(huà)面中,顯示所對(duì)應的(de) Allegro Footprint 形狀及引腳數量 (Pin number) 和(hé) 引腳名稱 (Pin Name) 的(de)位置

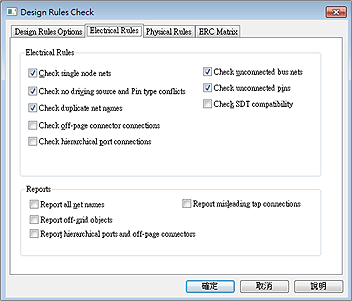

Design Rules Check 檢查的(de)更新

原理(lǐ)圖 Design Rule Check 檢查的(de)更新,現在分(fēn)成含有電氣屬性的(de)檢查及不含電氣屬性檢查兩大(dà)部分(fēn),并且在檢查項目中增加了(le)重複 Net name、Footprint missing、未擺放的(de)複合式零件 Package 等重點檢查或報告項目。

Tcl/Tk 程序支持

OrCAD X Capture/CIS 開始 Tcl/Tk 程序的(de)支持,可(kě)以自行開發程序或是到原廠 Markeplace 網站下(xià)載 OrCAD X Capture/CIS Utility 挂載到程序中使用(yòng)!

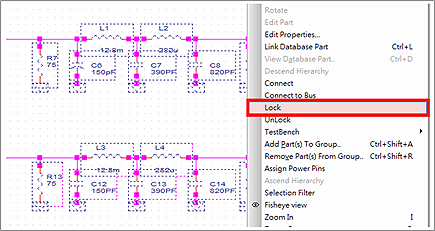

原理(lǐ)圖鎖定功能,原理(lǐ)圖可(kě)将部分(fēn)區(qū)塊或整頁原理(lǐ)圖物(wù)件鎖定 (Lock),鎖定的(de)物(wù)件将不可(kě)移動或删除