快(kuài)速完成複雜(zá)封裝設計

随著(zhe)市場(chǎng)對(duì)産品功能「集積化(huà)」的(de)需求,高(gāo) pin 數 / 多(duō)功能的(de)高(gāo)級零件封裝設計也(yě)更顯重要,爲了(le)有效地設計這(zhè)些複雜(zá)的(de)封裝,需要一個(gè)複雜(zá)的(de)設計工具來(lái)解決電氣和(hé)物(wù)理(lǐ)方面的(de)限制。Cadence® 封裝設計技術以其高(gāo)效、靈活和(hé)可(kě)靠的(de)技術來(lái)完成密集先進的(de)封裝而享譽全球。若再另外搭配集成的(de)信号和(hé)電源完整性分(fēn)析選項可(kě)确保在整個(gè)設計周期中共同解決電氣和(hé)物(wù)理(lǐ)難題。使用(yòng) Cadence 封裝設計技術,設計人(rén)員(yuán)有可(kě)能在最短的(de)時(shí)間完成項目甚至可(kě)以首次通(tōng)過符合規格以滿足壓縮時(shí)間表的(de)要求。

Cadence 封裝設計解決方案

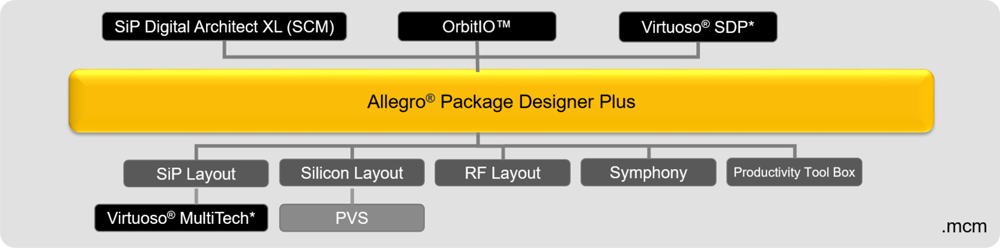

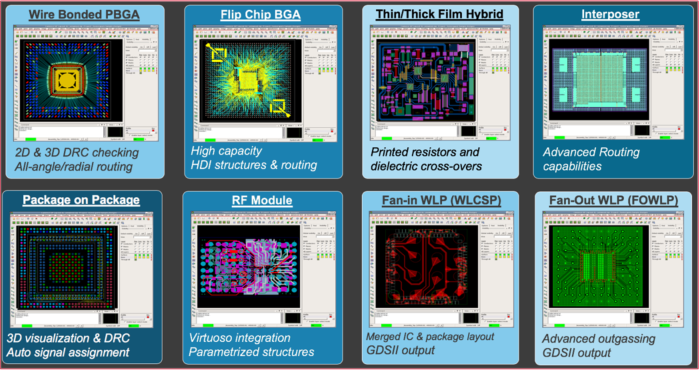

現在,Package 封裝設計已成爲 IC-Package-Board 設計流程中的(de)關鍵環節。 Cadence Allegro® 平台爲 PCB 和(hé)複雜(zá)封裝的(de)設計和(hé)實現提供了(le)完整且可(kě)擴展的(de)技術。不論您是 Lead Frame、WireBond、flip-chip 或 Interposer 等等的(de)封裝技術,您都可(kě)以利用(yòng) Allegro X Advanced Package Designer 專爲封裝設計所開發的(de)各項方便易用(yòng)的(de)功能優化(huà)複雜(zá)的(de)單芯片和(hé)多(duō)芯片的(de) Wirebond 和(hé) Flip Chip 設計,來(lái)達到快(kuài)速集成産品特性和(hé)功能優化(huà)之目的(de),以降低成本和(hé)性能,同時(shí)又能縮短項目時(shí)間。

Constraint-Driven 的(de)業界标準和(hé)技術可(kě)實現高(gāo)級 OSAT 和(hé)晶圓廠從單芯片到複雜(zá)的(de)系統規劃和(hé)封裝設計。

Cadence 封裝設計解決方案可(kě)實現高(gāo)效的(de)封裝設計技術,具有規範意識的(de)基闆布線設計。若另外需要布線模型萃取、模型建立和(hé)信号 SI/PI 分(fēn)析等功能有以下(xià)産品:

|

Allegro X Advanced Package Designer |

|---|---|

|

SiP Layout Option 選購(gòu) ⇒ 升級到标準 SiP 版 |

|

Silicon Layout Option 選購(gòu) ⇒ Wafer Level Package 專用(yòng) |

|

RF Layout Option 選購(gòu) ⇒ 繪制 RF 零件 / Layout |

|

Symphony™ Team Design Option 選購(gòu) ⇒ 多(duō)人(rén) (實時(shí)) 同步設計 |

|

System Connectivity Manager 另購(gòu) ⇒ 表格式的(de)線路圖工具 |

|

OrbitIO™ interconnect designer 另購(gòu) ⇒ 可(kě)做(zuò) IC / PKG / PCB 的(de)最佳接點優化(huà)規劃 |

效益

|

技術文件套用(yòng)架構~可(kě)簡化(huà)并自動化(huà)設計設置 |

|---|---|

|

從前到後有線路圖和(hé)無線路圖的(de)流程,爲邏輯管理(lǐ)提供了(le)業界最靈活的(de)模型 |

|

動态式組件庫建立可(kě)簡化(huà)數據輸入 |

|

wire-bond、flip-chip、stacked 和(hé) embedded die 等智能定義可(kě)确保布局時(shí)有按正确的(de)構造進行 |

|

先進的(de) Bond-shell 生成技術甚至可(kě)以使最複雜(zá)的(de)多(duō)芯片或堆棧式的(de) Wirebond 設計自動化(huà) |

|

放射狀、任意角度的(de)推擠式布線解決了(le) BGA / LGA 基闆布局的(de)獨特挑戰 |

|

專用(yòng)于 BGA / LGA 的(de) DRC / DFM / DFA 檢查,可(kě)确保在第一時(shí)間就能有正确設計以符合生産 |

|

3D 檢視和(hé) DRC 比傳統 2D 檢查更能準确地驗證設計 |

|

與 Cadence Innovus 和(hé) Virtuoso IC 設計工具的(de)集成流程,可(kě)簡化(huà) IC 和(hé)封裝之間的(de)協同設計 |

|

與 Cadence Clarity™ 和(hé) Celsius™ 的(de)緊密結合,可(kě)快(kuài)速準确地進行封裝設計中電氣和(hé)熱(rè)的(de)驗證 |

|

可(kě)搭配 Symphony Team Design 的(de)選項,讓多(duō)人(rén)可(kě)同時(shí)編輯封裝設計以縮短總體設計的(de)時(shí)間 |

|

可(kě)選購(gòu) Silicon Layout Option 來(lái)擴展功能,以處理(lǐ) IC 等級的(de)布局檢查和(hé) Mask 驗證 |

|

全球超過 400 多(duō)個(gè)客戶使用(yòng) |

功能特點

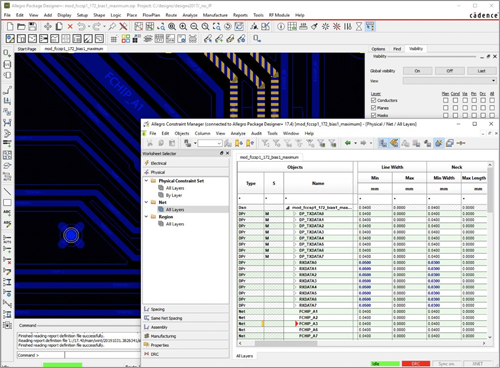

Constraint-Driven 的(de)封裝設計架構

Allegro X Advanced Package Designer 包含當今先進封裝設計所需的(de)所有功能。其完整的(de)實時(shí) DRC 設計規則檢查支持能對(duì)應到層壓、陶瓷和(hé)矽基基闆,或如多(duō)個(gè) cavities、複雜(zá)鋪銅及 Wirebond 等多(duō)種結構集成的(de)先進封裝集成需求。

其易于使用(yòng)的(de) Flow Manager 引導您完成每個(gè)任務,自動執行創建 IC 封裝的(de)基本組成部分(fēn)的(de)過程,便捷的(de)向導程序可(kě)自動快(kuài)速地建立出封裝設計中的(de)各項特定零件或需求,如 WireBond、Power/Ground Rings 和(hé) plating bars 等,更可(kě)用(yòng) die 和(hé) BGA Wizards 載入的(de)文本文件 (D.I.E.、Excel、AIF2) 以自定字段的(de)方式,自動建立其接點不一的(de)零件。現在您甚至可(kě)以由 GDSII 或 DXF 的(de)圖形辨識來(lái)自動建立所需的(de)零件。

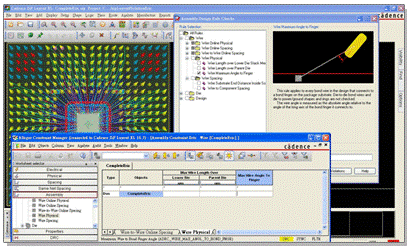

完備的(de)基闆建模和(hé)規則檢查

可(kě)藉由完備的(de)物(wù)理(lǐ)和(hé)電氣規則 (constraints) 對(duì)設計做(zuò)最準确的(de)驗證和(hé)查核,加載由使用(yòng)者定義的(de) Technology File,可(kě)做(zuò)爲 Physical 實體設計的(de)規範以确保其可(kě)制造性,而 Electrical 電氣規範可(kě)定義重要信号,如延遲和(hé)失真的(de)規格,可(kě)随時(shí)跟 constraints 比對(duì)以确保設計能符合制造和(hé)電氣的(de)種種要求,表格化(huà)的(de) Constraint Manager 可(kě)清楚的(de)管控所有的(de)規範。另外,實時(shí)的(de) drc 檢查可(kě)配合現今複雜(zá)且特殊的(de)各種載闆設計需求。

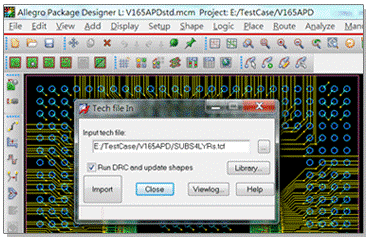

可(kě)重複套用(yòng)先前設計結構

Substrate 的(de)叠構和(hé) constraint 信息被記錄在 technology 中,當局部設計還(hái)是整個(gè)設計結構相似時(shí),我們可(kě)以套用(yòng)在設計上不需重新定義以縮短将來(lái)設計的(de)時(shí)程,制造商或供貨商也(yě)可(kě)以提供包含關鍵設計規則的(de) technology file 以幫助推動正确的(de)設計方法來(lái)确保輔助供貨商的(de)可(kě)制造性。

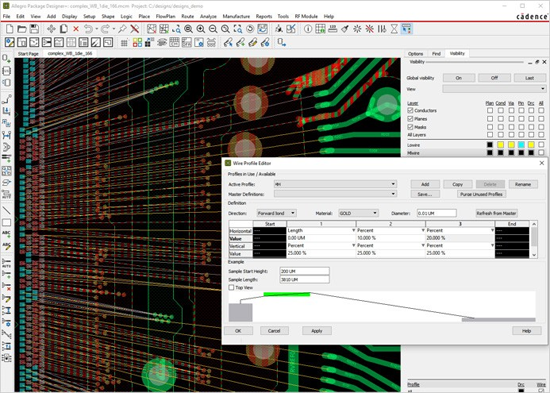

WIREBOND 和(hé) FLIP-CHIP 及 Copper Pillar 的(de)接出樣式

Allegro X Advanced Package Designer 提供快(kuài)速、強大(dà)且靈活的(de) Wirebond 建立和(hé)編輯功能,隻需要簡單幾個(gè)按鍵就可(kě)建立出 die flags 和(hé) Power/Ground Rings 及各式各樣的(de) bondfinger。Die flags 可(kě)以用(yòng)向導接口自動建立,或是以加載的(de) TXT/dxf 來(lái)建立,而強大(dà)的(de) Power Rings 可(kě)建立、切割及合并電源圈以配合現今多(duō)重電源的(de)需求。另外也(yě)有推擠及群組等功能,在數分(fēn)鐘(zhōng)之内即可(kě)建立出所要的(de)打線架構,而真實的(de) wire profile 可(kě)實現 DFM-driven 的(de)設計架構,防範于未然,并提供實時(shí)的(de)設計回饋,或可(kě)直接套用(yòng) Kulicke & Soffa 所驗證過的(de)定義檔,以确定所設計出的(de) wirebond 都能夠真正被生産實現。

對(duì)于 Bump (凸塊) 和(hé) pillar (支柱) 的(de)連接,設計人(rén)員(yuán)可(kě)用(yòng)自動和(hé)半自動工具來(lái)建立這(zhè)些經過驗證的(de)架構,快(kuài)速套用(yòng)在DIE上,以符合當今高(gāo)密度封裝設計需求。

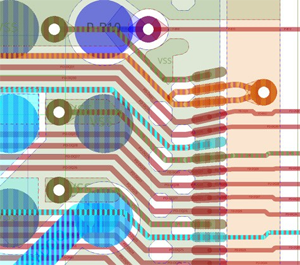

全自動的(de) BUMP-TO-PACKAGE 接點設定和(hé)布線完成率評估

除了(le)支持使用(yòng)傳統線路圖和(hé) netlist-based 的(de)邏輯定義之外,利用(yòng) OrbitIO 互連設計器進行前期跨架構的(de)系統規劃,或是利用(yòng) SiP Digital Architect 下(xià)的(de) System Connectivity Manager 的(de)獨特系統連接管理(lǐ)器,都可(kě)以很有效的(de)規劃及分(fēn)配總體的(de)聯機關系。邏輯關系也(yě)可(kě)手動直接定義,或者是套用(yòng)現有設計規範下(xià),以最好的(de)走線等的(de)不同模式架構下(xià)做(zuò)最适當的(de)自動布線考慮并定義出其聯機關系,如将各信号會依照(zhào)規範及空間做(zuò)信号的(de)指定,差動信号的(de) BUMP 也(yě)會照(zhào)封裝接點選擇最好的(de)位置選擇,而 net-per-layer 也(yě)可(kě)清楚的(de)看到所有信号的(de)分(fēn)布狀态。另外,route planning 的(de) flow 和(hé) bundles 對(duì)整組信号分(fēn)類和(hé)視覺上效果,對(duì)于高(gāo)速信号規劃會更有幫助。

手動 / 半自動和(hé)自動布線

Allegro X Advanced Package Designer 和(hé) SiP Layout Option 集成了(le)一套基于規則的(de)半自動和(hé)的(de)自動布線功能,讓我們面對(duì)無論是任意角度、單層、Wirebond 還(hái)是增層結構上多(duō)加的(de) silicon interposer 等任何類型的(de) IC 封裝設計,都在确保其可(kě)制造性之下(xià)能快(kuài)速準确地完成布線設計。

HDI 高(gāo)密度設計

HDI 高(gāo)密度或增層式的(de)設計也(yě)廣泛地應用(yòng)在封裝設計中,以求最有效的(de)層面利用(yòng)及配合細小間距的(de) flip chip 需求。Allegro X Advanced Package Designer 能搭配其完整的(de) HDI 規範以達到其自動輔助設計的(de)目的(de),而微導孔 (microvia) 的(de)充分(fēn)支持和(hé)自動設定,并可(kě)做(zuò)合并及分(fēn)離等編輯,讓層面的(de)利用(yòng)率最高(gāo)并符合生産需求,以達成設計和(hé)生産的(de)共同目标。

切圖設計

若欲執行完整功能,需加購(gòu) Symphony Team Design Option

Cadence 提供了(le)多(duō)個(gè)使用(yòng)者或同步的(de)設計環境,加速設計時(shí)效、加快(kuài)上市時(shí)程。

其中 Partition 可(kě)将整份設計依其區(qū)塊或層面切分(fēn)給多(duō)個(gè)使用(yòng)者,而使用(yòng)者可(kě)查看别區(qū)塊的(de)的(de)最後更新結果加以配合調整,進而壓縮整份設計的(de)總體設計時(shí)程。

還(hái)有同步的(de) Symphony,可(kě)讓多(duō)個(gè)設計人(rén)員(yuán)在同一時(shí)間同時(shí)操作同一個(gè)設計進行工作,而無需分(fēn)區(qū)設置。當加入的(de)布線工程師越多(duō),完成布線的(de)速度就可(kě)越快(kuài)。在布線的(de)同時(shí),可(kě)以引用(yòng) Allegro X Advanced Package Designer 和(hé) SiP Layout Option 内的(de)各項功能,如強大(dà)的(de)鋪銅編輯或 Allegro auto-interactive phase tune (AiPT),和(hé) auto-interactive delay tune (AiDT) 等自動 Tune 線的(de)功能加速設計完成 。

DesignTrue DFM 和(hé) ARC 檢查

( 僅包含基本檢查,完整檢查仍需加 SIP Layout Option )

Constraint Manager 中有全面的(de) design for manufacturing (DFM) 制造設計檢查功能,若有 SIP Layout Option,其中另外有的(de) assembly rule checker (ARC) 提供了(le)數百種檢查來(lái)滿足制造上的(de)要求 (非傳統 DRC 的(de)間距檢查)。其檢查項目可(kě)把這(zhè)些規則加以分(fēn)類或單獨指定或是自定義選擇來(lái)執行,最終的(de)檢查也(yě)會顯示在 Constraint Manager 的(de) DRC 頁面中及圖檔上。

多(duō)元的(de)生産制程資料準備

在生産制程的(de)準備方面,而從文件到生産的(de)各種數據都十分(fēn)完備。可(kě)以很快(kuài)速地建立出打線數據、尺寸标注、所需圖樣和(hé)封裝數據,或如鍍金棒 (plating bar)、蝕斷線 (etchback plating)、透氣孔 (metal pour degassing) 和(hé)銅箔平均化(huà) (metal layer balancing) 等等都有考慮。爲了(le)搭配後段的(de)生産檢查甚或 SI 分(fēn)析,所支持的(de)輸出格式包括有 Gerber、IPC2581、DXF、AIF2 及 GDSII 等。如果有 SIP Layout Option,還(hái)能利用(yòng) design variants 功能來(lái)定義出不同零件搭配組合的(de) BOM。另外,大(dà)多(duō)數的(de)封裝廠也(yě)都是使用(yòng) Cadence 的(de) PACKAGE 産品,所以若情況許可(kě)也(yě)可(kě)将設計圖檔直接給封裝廠,讓此數據在不破壞原始規範的(de)情況下(xià)做(zuò)更細的(de)生産參數微調,以提高(gāo)産出的(de)良率。

對(duì)于 PCB 系統階的(de)數據傳遞

Allegro X Advanced Package Designer 工具不隻能連結 silicon 與 package 設計,也(yě)能連結 package 與 PCB 設計。對(duì) PCB 所需的(de) floor planning 規劃跟 layout 的(de)相關數據,也(yě)能自動建立出所需的(de)實體零件、線路圖 symbol、跟 device 模型。您也(yě)能夠萃出 Die 或 BGA 的(de)數據到 Excel 格式的(de)電子表格中,以加速設定時(shí)間并提高(gāo)其準确率。

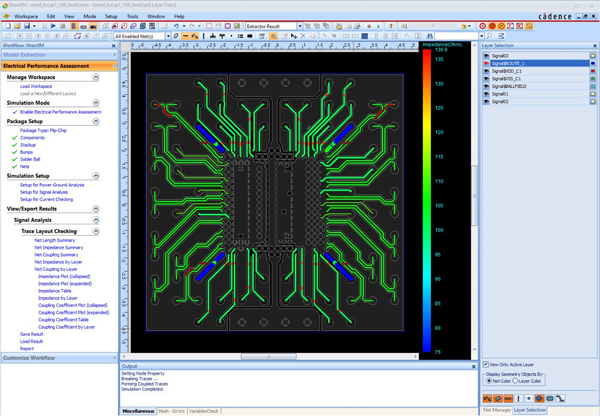

封裝設計的(de)信号和(hé)電源分(fēn)析

借助 Cadence 的(de) Clarity™ 和(hé) Celsius™ 技術,可(kě)以進行詳細的(de)布線萃取和(hé) 3D 封裝建模,以及具電源考慮的(de)信号完整性和(hé)熱(rè)的(de)分(fēn)析。這(zhè)些功能使封裝分(fēn)析和(hé)建模解決方案能夠在早期的(de)設計時(shí)間就能開始進行特性評估以及 DC/AC PDN 分(fēn)析,進而到最後使用(yòng) Hybrid EM 混合求解器來(lái)萃取完整封裝模型,或使用(yòng)全波 3D 求解器來(lái)萃取更詳細封裝模型。

您可(kě)以依需求做(zuò)以下(xià)檢查:

|

封裝設計特性評估,可(kě)快(kuài)速檢測有問題的(de)封裝設計數據,包括檢測封裝引腳是否有過多(duō)的(de)電感效應、不适當的(de)阻抗和(hé)耦合等 |

|---|---|

|

含電源考慮的(de)混合求解器萃取,可(kě)考慮 PDN 及信号的(de)耦合并進行 RLGC 和(hé) S 參數的(de)模型萃取 |

|

全波 3D 求解器 - 解析封裝設計内部詳細結構用(yòng)于高(gāo)頻(pín)布線模型萃取 |

|

IR-Drop 分(fēn)析 - 同時(shí)考慮布線和(hé)零件效應的(de)電 / 熱(rè)協同模拟,及不同區(qū)塊的(de)溫度分(fēn)布和(hé)鋪銅 / 貫孔 / 走線間的(de)電流密度計算(suàn) |

封裝性能評估可(kě)以在實際布線的(de)早期階段開始,而不需等到最後才可(kě)執行。利用(yòng)初始的(de)聯機關系進行可(kě)行性研究,例如考慮 DC 的(de) IR-Drop 和(hé)電流的(de)最佳叠構 / 規範以及信号的(de)拓撲架構,可(kě)幫助确定最終的(de)封裝類型并以最低的(de)成本達到最佳的(de)電氣性能。随著(zhe)封裝設計的(de)繼續,可(kě)以萃取信号和(hé) PDN 的(de)模型,以考慮 RLC 的(de)寄生效應和(hé)信号的(de)阻抗和(hé)串擾,或 insertion 和(hé) return losses 的(de)關鍵特性。

還(hái)可(kě)搭配現行大(dà)多(duō)數 OSAT 和(hé) Foundry 所使用(yòng)的(de) Cadence 封裝設計技術,來(lái)探索散熱(rè)方面的(de)考慮。利用(yòng)這(zhè)種互操作性,當設計達到最後階段時(shí)能夠互相搭配交換電熱(rè)分(fēn)析數據,以執行更完整的(de)封裝評估 (包括 IR-Drop) 和(hé)模型萃取,并生成最終的(de) HTML 報告,以确保實時(shí)發現重大(dà)問題并完整記錄設計。

若是會在高(gāo)頻(pín)下(xià)運行的(de)封裝設計,可(kě)以在關鍵封裝區(qū)域執行全波 3D 萃取以确保能滿足高(gāo)速信号的(de)性能規格。

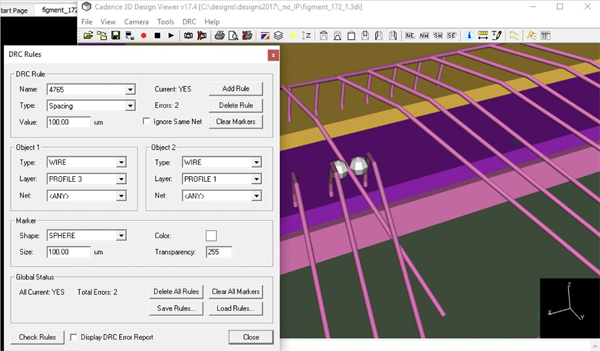

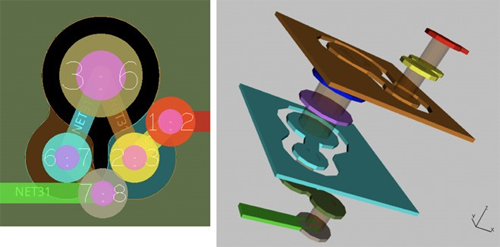

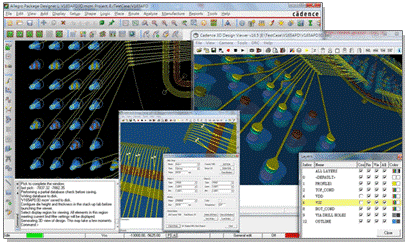

3D 設計視圖功能

Cadence 3D Design Viewer 用(yòng)于複雜(zá)的(de) IC 封裝設計檢查,是一個(gè)完整的(de)實體 3D 模型檢測器和(hé) 3D Wirebond DRC 解決方案,現已包含在 Allegro X Advanced Package Designer 中。它爲跨團隊設計的(de)審查提供了(le)共同的(de)平台讓用(yòng)戶可(kě)查看和(hé)研究整個(gè)設計,如在具有多(duō)重 Wirebond 結構的(de)封裝設計下(xià),選定的(de)最佳 Wirebond Profile 打線定義的(de)組合效果。

智慧 3D 設計視圖

盡管 2D 顯示非常适合于基闆布局、布線規劃和(hé)金屬鋪面等繪制,但 2D 的(de)效果并不适合用(yòng)于複雜(zá)芯片立體堆棧和(hé) 3D 集成的(de)設計 / 管理(lǐ)或驗證,封裝設計的(de)複雜(zá)性和(hé)密高(gāo)度的(de)要求更顯出 3D 的(de)重要性。 利用(yòng) Cadence 3D Design Viewer 使封裝設計人(rén)員(yuán)能夠以 3D 的(de)方式,查看其實際設計來(lái)滿足此需求。設計人(rén)員(yuán)可(kě)以交互式的(de)縮放 / 平移 / 旋轉 3D 視圖,或是從一組預定的(de)視角效果中進行選擇。

互動标記

在查看 3D 設計期間,工程師可(kě)以爲設計審查或設計資料建出 “Markup” 标記快(kuài)照(zhào),其中包括添加基本圖形、箭頭和(hé)文字的(de)功能,這(zhè)對(duì)于與設計夥伴間的(de)集成,以及測試和(hé)裝配制造部門進行溝通(tōng)時(shí),特别有用(yòng)。

3D Wirebond 間距檢查

在 Allegro X Advanced Package Designer 設計中,可(kě)定義和(hé)儲存其 3D 檢查規則。您可(kě)自行定義這(zhè)些規則來(lái)檢查設計中 Wire 導線,和(hé)零件之間的(de) 3D 間距。