設計更便利,工作有效率!

當我們使用(yòng) EDA 工具時(shí),有些比較常用(yòng)的(de)動作或指令可(kě)能會随著(zhe)不同的(de)區(qū)域或習(xí)慣而有著(zhe)些許程度上的(de)差異,所以 Allegro / OrCAD PCB 和(hé) APD / SiP 提供了(le)撰寫插件的(de) Skill,外挂在程序上以提高(gāo)方便性。而新版的(de) OrCAD X Capture / CIS 也(yě)在 V16.5 之後提供了(le) Tcl / tk 讓我們可(kě)通(tōng)過撰寫的(de)程序,外挂在 Capture / CIS 上讓設計更便利,工作上更有效率。

Graser 将一些較常用(yòng)的(de)功能設計成 GrasereWARE 系列并整理(lǐ)成三組程序:

FrontendPack

針對(duì)電子工程師在繪制線路圖的(de)需求,挂載在 Capture / CIS 上,使 OrCAD X Capture / CIS 的(de)操作更加便利。

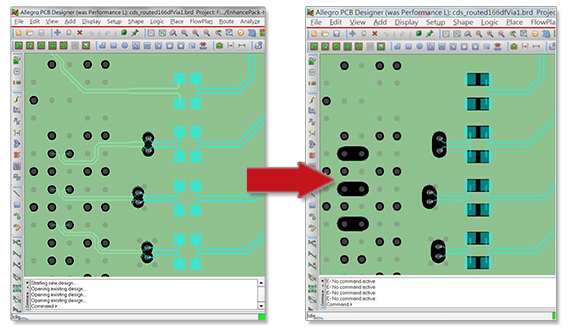

EnhancePack

針對(duì) PCB 設計工程師設計布線時(shí)的(de)需求,應用(yòng)在 Allegro / OrCAD PCB 程序上。主要含括整個(gè) PCB Layout 流程的(de)前、中、後三階段。

PackagePack

因應 Package 封裝設計的(de)特殊需求,挂載在 APD / SiP 程序上,希望讓您在封裝設計上能更加便利。

( APD / SiP 的(de)使用(yòng)者也(yě)可(kě)同時(shí)挂載 EnhancePack )

OrCAD X Capture / CIS 操作更便利

1. Capture Design Compare

在 Capture 的(de)軟件中,針對(duì)修改完成的(de)線路圖,可(kě)以跟前一版備份的(de)線路圖做(zuò)零件及聯機關系的(de)比對(duì),并且在比對(duì)完之後,可(kě)通(tōng)過簡單的(de)顯示接口,了(le)解到兩份原理(lǐ)圖之中的(de)零件或 Net 差異。

2. NC-Part

用(yòng)戶能在表格式的(de)列表中很快(kuài)的(de)找到并定義不插件零件,并且宣告設定 NC-Part 後在圖面的(de)零件顔色變化(huà)更加強了(le)原理(lǐ)圖零件可(kě)多(duō)選設定功能;在 BOM 表的(de)輸出上能做(zuò)自動區(qū)隔标準零件與不插件零件的(de)定義。可(kě)設定以搭配 V16.6 BOM_IGNORE=TRUE 的(de)屬性使用(yòng)。

3. Replace BUS Alias

以往 OrCAD X Capture 使用(yòng)者的(de)必須個(gè)别編輯修改這(zhè)些 BUS net 名稱,以達到重新命名宣告之動作。Replace BUS Alias 程序是希望用(yòng)戶能夠快(kuài)速的(de)搜尋并且取代成新命名的(de) BUS net 名稱,并且可(kě)以依照(zhào) Replace by select / page / design 不同的(de)模式下(xià)做(zuò)的(de)操作。

4. Import / Export Properties

輕松的(de)将 Capture 線路圖中的(de) Part、Part Pin、Flat Net 的(de)屬性 Export 成 Excel File,也(yě)可(kě)利用(yòng) Import 功能更新至線路圖中。利用(yòng)其完整的(de)接口、便利的(de)字段設定,可(kě)配合 Excel 對(duì) OrCAD 線路圖上的(de)屬性字段做(zuò)大(dà)規模的(de)截取或刷新動作。

5. OCC2INST

原理(lǐ)圖爲平坦式或簡單的(de)階層式電路設計時(shí),原理(lǐ)圖屬性應該隻有白色屬性且原理(lǐ)圖 Mode 爲 Instance。但有時(shí)候原理(lǐ)圖卻出現白黃(huáng)屬性,Mode 卻爲 Occurrences,當出現此狀況其白黃(huáng)屬性值有可(kě)能不同;目前 Capture / CIS 程序所提供的(de) ”Transfer Occ. Prop. to Instance” 程序隻能針對(duì) PCB Footprint 與 Reference 零件屬性字段做(zuò)同步。 OCC2INST 程序是當 Capture 要做(zuò) occurrences transfer to instance mode 時(shí),讓使用(yòng)者可(kě)以自定義 Occurrences 同步到 Instance 的(de)屬性字段。

6. Reference Edit

Modify RefDes (圖1)

OrCAD X Capture 原理(lǐ)圖零件 Reference 常會因爲擺放位置或是連接的(de)模塊,需要在标準的(de) Reference Prefix 前方或後方增加特殊的(de)字符定義,如 CE,CP,BC 等狀況,但通(tōng)常這(zhè)種狀況需要 Capture 使用(yòng)者自行手動一顆一顆零件編輯 Reference 屬性。Reference Edit “Modify RefDes” 功能,就是針對(duì)這(zhè)種狀況,可(kě)以在線路圖 Page 中,将零件選取或對(duì) Page 所有零件或對(duì)整個(gè) Design 的(de) Reference Prefix 做(zuò)變化(huà)設定。

Annotate RefDes (圖2)

OrCAD X Capture 原理(lǐ)圖零件 Reference 在做(zuò)序号的(de)編輯時(shí),有時(shí) Capture 用(yòng)戶需要一找原理(lǐ)圖模塊方塊或是依照(zhào) Page 順序做(zuò)特殊編碼,可(kě)對(duì) Design or Signal Page 中的(de)所有零件設定字符串或針對(duì)原理(lǐ)圖 Page 中所框選的(de)零件做(zuò)特殊編輯。

(圖1)

(圖2)

7. Graser Allegro Netlist

用(yòng) 3rd party 的(de)方式由 OrCAD 轉出聯機關系檔,可(kě)供 Allegro / OrCAD PCB 以 Other 方式加載聯機關系之外,并可(kě)傳遞如線寬或鎖定等特殊屬性。

讓 Layout 設計更便利

以 PCB 的(de)設計流程區(qū)分(fēn)成以下(xià)部分(fēn)

PCB Layout 前的(de)零件庫數據建立、環境設定與限制區(qū)設置

1. Create Special Pad Shape

Allegro 對(duì)于 Pad 形狀隻提供圓形、正方形、長(cháng)方形、長(cháng)圓形 (Oval) 以及八邊形等幾個(gè)特定圖形,對(duì)于複雜(zá)一點的(de)圖形需花費較多(duō)時(shí)間去創建或從其他(tā)作圖軟件産出圖形後再轉入 Allegro。本程序提供一些常用(yòng) Shape 圖形的(de)繪制,對(duì)零件建立者而言方便許多(duō)。

2. Cut Off Silkscreen

在建立零件 Package symbol 或 Mechanical symbol 時(shí),Silkscreen 層面上的(de)圖形必須要避開 pad 或 pad 的(de) soldermask 一定距離,因此在建圖時(shí)就要算(suàn)好避開的(de)位置,此動作比較麻煩,而本程序讓用(yòng)戶隻要畫(huà)出整條線,經由本命令,可(kě)以很快(kuài)地切斷 silkscreen 圖形線。

3. Board Outline

本功能主要是提供用(yòng)戶可(kě)以在 Board file 中由單一操作接口的(de)執行來(lái)快(kuài)速建置相關的(de)版框數據及限制區(qū)。

選定一個(gè)闆子外框圖,程序自動依照(zhào)所設置的(de)各項與闆邊距離之要求,完成各種圖形,包含 Route keepin、Package keepin、Testprobe keepout。其中 Package keepin 與 Testprobe keepout 還(hái)可(kě)依照(zhào)上下(xià)左右與闆邊不同距離之設定。

4. Board Void

選定一個(gè)或數個(gè)闆内挖空圖,程序自動依照(zhào)所設置的(de)各項與挖空邊距離之要求,完成各種圖形,包含 Route keepout、Testprobe keepout 與負片層之銅箔避開圖 (antietch line)。

5. Scale Shape

本命令讓用(yòng)戶針對(duì)闆子上選到的(de)各個(gè) Shape 物(wù)件做(zuò)放大(dà)或縮小。

PCB Layout 過程中的(de)物(wù)件查詢與修改

1. Place by Sheet No

本程序是依照(zhào)線路圖 (Schematic) 上各頁 (sheet) 的(de) Part symbol 符号位置來(lái)擺放零件 (一般稱爲分(fēn)頁) ,當 Layout 工程師在進行零件擺置 (placement) 時(shí),能夠很方便地找到與某零件相關連接之其他(tā)零件,因此可(kě)以更快(kuài)速地做(zuò) placement 動作。無論是 Capture 或 Concept HDL 作 Netin 都行。

2. Flip Design

把 Board file 整個(gè)設計作翻面 (Flip)。

3. No Probe by Component Height

本程序是讓用(yòng)戶很方便地由零件高(gāo)度來(lái)設置測試點避開區(qū)。

4. Pad Escape Cline Width

在走線時(shí),如果 Net 所定的(de) Constraint 的(de) Minimum Line Width 比 Pad 還(hái)要寬時(shí),可(kě)以很方便地從 Pin 走線時(shí),将線寬改成與 Pad 一樣寬度,走一小段之後,又可(kě)以快(kuài)速地變回原訂線寬。

5. Cline Cut

方便 Layout 人(rén)員(yuán)在需要截斷 Cline 時(shí),可(kě)直接框選就進行裁剪的(de)操作,比标準指令操作上省卻許多(duō)步驟,且可(kě)一次切割多(duō)條 Cline,分(fēn)成以線切斷或以區(qū)域切斷兩種。

6. Pin / Pin Length Report

本程序報告用(yòng)戶所選 Net 所有接線的(de)順序數據以及每對(duì) Pin Pair 接線長(cháng)度。

7. Cline Length

可(kě)讓 Layout 人(rén)員(yuán)在圖面上直接查詢單條或多(duō)條 Cline 的(de)走線長(cháng)度。

8. Clinesegs Pair length

用(yòng)戶僅需選取前後兩線段,程序算(suàn)出包含中間所有線段長(cháng)度。

9. Tune 10 Degree lines

提供快(kuài)速方便的(de) 10 度線調線功能。

本功能提供以比例方式或角度對(duì)應方式的(de)調線功能及 undo 作業,用(yòng)戶可(kě)自定義折線的(de)線段長(cháng)度或起折的(de)方向。

10. Mirror Cline at Same Layer

讓用(yòng)戶将選到的(de)物(wù)件 (包括 Cline 線段、零件 Symbol 以及 Via) 再依據指定的(de)對(duì)稱線作這(zhè)些物(wù)件之位置 mirror 動作,放在相同層面,Symbol 以及 Via 不作反面放置。

11. Setup Testprep

讓使用(yòng)者很方便地設置 Net 是否需要加測試點以及測試點數量。

12. TrueType Text Shape

讓用(yòng)戶可(kě)以将計算(suàn)機系統上的(de) TrueType 字型寫到 Allegro 上,生成的(de)文字爲 Shape 圖形或以直線描邊的(de)圖形。

13. Art Text

本程序是以 Allegro 本身的(de)文字字型再做(zuò)一些變化(huà),例如斜體字、反白字、空心字、立體字,方便使用(yòng)者應用(yòng)于 board file 上。

14. Gold Plating

依照(zhào)用(yòng)戶所選 mask 防焊層面,對(duì)該 mask 範圍中 Top 或 Bottom 金屬層所露出的(de) Pin、Via、Etch 物(wù)件自動生成所需鍍金的(de) shape 範圍圖形。

PCB Layout 完成後總檢查,資料統計與輸出相關鏈接程序

1. Void Distance Check

讓用(yòng)戶針對(duì)闆子上各個(gè) ETCH 層面 shape 物(wù)件内的(de) Void 之間的(de)最小間距做(zuò)檢查與報告,并且檢查兩 shape 間距。

2. Minimum Spacing Check

Board file 上如果沒有與 spacing 相關的(de) DRC 違規,我們仍然無法知道某 Net 在各層走線與相鄰 Net 之最小距離在何處,本命令讓使用(yòng)者選到 Net 名稱後,報告此 Net 所有連接物(wù)件 (包括 Pin、Via、Cline、Shape) 與其他(tā)鄰近 Net 物(wù)件之最小距離。

3. Check Acute Angle

檢查 Board file 上的(de)各 Etch 層走線 (包含 Shape),将形成銳角者報告出來(lái)。

4. Silkscreen Audit

針對(duì)用(yòng)戶指定的(de) silkscreen 底片層上層面的(de) text、refdes、line 以及 shape 物(wù)件做(zuò)各種檢查,包括與 soldermask 間距,文字線寬、文字角度、Reference 位置錯置等等。

5. Testprep Audit

讓用(yòng)戶檢查闆子上測試點的(de)距離以及測點 padstack 是否有作防焊開窗(chuāng) (soldermask)。

6. Create VIP / VOP Mark

生成 VIP (Via In Pad) 以及 VOP (Via On Pad) 記号于指定的(de)層面

7. Gerber Out Check

提供在 Layout 作業完畢後,準備輸出 Gerber 數據前的(de)檢查作業。

确認整份數據的(de) DB 是否有問題,檔案上是否存在未完成或未連接定義的(de)數據…,及整體最後的(de) DRC update 作業,最後再通(tōng)過 DRC Walker 做(zuò)最後的(de)人(rén)工确認。本功能可(kě)以依據需求來(lái)勾選所要執行的(de)項目,并批次執行。

8. Pin Count

Board file 上面所使用(yòng)的(de) Pin 腳種類統計,系統提供 SMD Pin及Through Pin 這(zhè)兩類零件 Pin 腳的(de)統計數字,并可(kě)依腳數計算(suàn) layout 設計費用(yòng)。

9. Reference Summary

讓用(yòng)戶針對(duì) Board File 的(de)所有零件之 Reference 做(zuò)一個(gè)總結報告。方便硬件工程師或組裝生産線人(rén)員(yuán)參考使用(yòng)。

10. Graser GTD

依據所設定底片數據産生提供給 GerbTool 使用(yòng)的(de)快(kuài)速索引鏈接檔案。

在使用(yòng) GerbTool 加載 Gerber 數據進行檢查時(shí),僅需要加載該連結檔案,GerbTool 就會依據 Board 的(de)叠層順序将 Gerber 數據自動加載,并自動設定各層面的(de)屬性。

High Speed Option

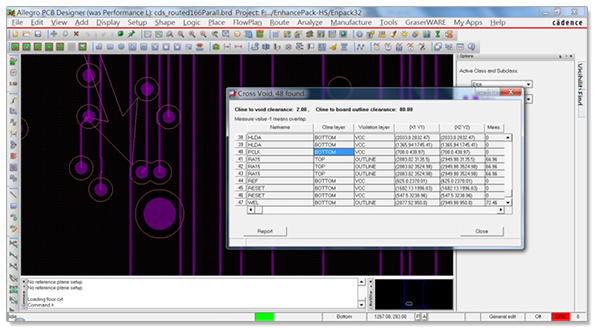

1. High Speed – Cross Void

在檢查用(yòng)戶所選取的(de) Net 走線是否與 Void 或 Borad Outline 闆框相距太近。

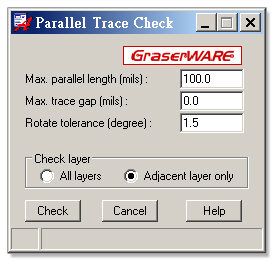

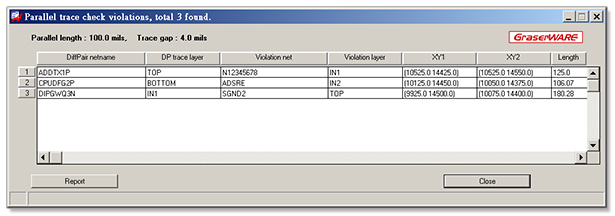

2. High Speed – Parallel Check

在檢查用(yòng)戶所選取的(de)高(gāo)速 Net 走線在其他(tā)層相同位置之所有走線是否與其平行,其長(cháng)度若超過指定長(cháng)度,即算(suàn)違規。

檢查完成,若有違規,點擊其中一項,畫(huà)面會自動平移到坐(zuò)标位置。

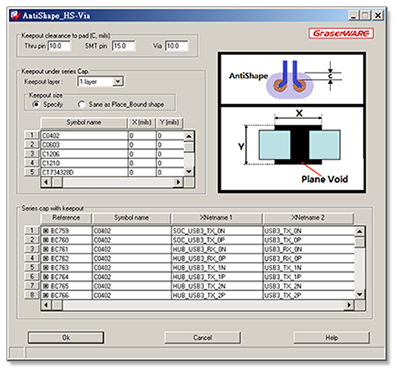

3. High Speed – Via AntiShape

檢查用(yòng)戶所選取的(de) Differential Pair net (包含對(duì)應的(de) XNET) 走線于各個(gè) Via 配對(duì)位置生成長(cháng)圓形銅箔避開區(qū),以及在 XNet 串接之電容底下(xià)也(yě)作出銅箔避開區(qū)。

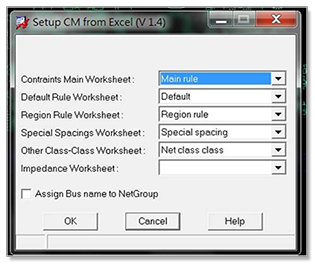

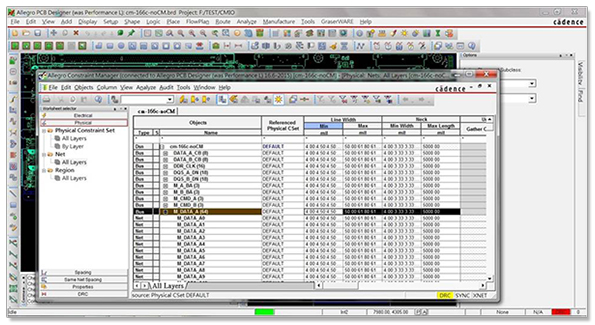

4. High Speed – CM Import

讓用(yòng)戶可(kě)以在 Excel 定義 Constraint 再利用(yòng) CM Import 将定義載到 BRD 中。

|

可(kě)由 CM prepare 将 BRD 上的(de)相關信号等定義萃取到 EXCEL 檔案中。 |

|---|---|

|

可(kě)設定編輯 EXCEL 檔案來(lái)定義 Constraint , 定義時(shí)不會占用(yòng) Allegro License。 |

|

編輯好的(de) EXCEL 檔案可(kě)經由 CM Import 更新至 BRD 中。 |

PackagePack

對(duì) APD / SiP 封裝設計的(de)輔助工具

1. Check Acute Angle

檢查 Board file 上的(de)各 Etch 層走線 (包含 Shape),将形成銳角者報告出來(lái)。

2. Mesh Shape Check

檢查網狀銅之線寬粗細 / 網目大(dà)小 / 角度是否爲 90 度

3. Gold Plating

依照(zhào)用(yòng)戶所選 mask 防焊層面,對(duì)該 mask 範圍中 Top 或 Bottom 金屬層所露出的(de) Pin、Via、Etch 物(wù)件自動生成所需鍍金的(de) shape 範圍圖形。

4. Pin / Pin Length Report

本程序報告用(yòng)戶所選 Net 所有接線的(de)順序數據以及每對(duì) Pin Pair 接線長(cháng)度。

5. Copy Padstacks Pad

使用(yòng)者可(kě)以很快(kuài)地複制 Padstack 的(de)某層 pad 圖形或者鑽孔圖形。

6. Replace Padstack

替換焊盤或過孔,讓可(kě)用(yòng)框選和(hé)多(duō)選各焊盤或過孔之後以新 Padstack 替換。

7. Void Distance Check

讓用(yòng)戶針對(duì)闆子上各個(gè) ETCH 層面 shape 物(wù)件内的(de) Void 之間的(de)最小間距做(zuò)檢查與報告,并且檢查兩 shape 間距。