最先進的(de) PCB 設計布線工具

Cadence® 是世界上最大(dà)的(de)電子設計技術和(hé)配套服務的(de) EDA 供貨商之一。Cadence® Allegro® PCB Design 則是 Cadence 推出的(de)先進 PCB 設計布線工具。Allegro 提供了(le)良好且交互的(de)工作接口和(hé)強大(dà)完善的(de)功能,和(hé)它前端産品 Cadence® OrCAD® X Capture 的(de)結合,爲當前高(gāo)速、高(gāo)密度、多(duō)層的(de)複雜(zá) PCB 設計布線提供了(le)最完美(měi)解決方案。

此外,由于新的(de)技術不斷發展,面對(duì)新的(de)接口,如 DDR3,DDR4,PCI Express,USB 3.0..等,需要使用(yòng)新的(de)方式來(lái)實現在電路闆上。這(zhè)些日益複雜(zá)的(de)技術再加上很多(duō)公司希望這(zhè)些産品推向市場(chǎng)更快(kuài),更便宜,有更多(duō)的(de)功能和(hé)最少的(de)設計成本。因此,現在很多(duō)企業也(yě)會外包給低成本的(de)合作夥伴。爲了(le)管理(lǐ)這(zhè)種不斷增加的(de)複雜(zá)度,印刷電路闆設計需要一個(gè)完整的(de)解決方案,同時(shí)滿足新的(de)技術和(hé)管理(lǐ)方式。

Allegro 擁有完善的(de) Constraint 設定,用(yòng)戶隻須按要求設定好布線規則,在布線時(shí)不違反 DRC 就可(kě)以達到布線的(de)設計要求,從而節約了(le)煩瑣的(de)人(rén)工檢查時(shí)間,提高(gāo)了(le)工作效率!更能夠定義最小線寬或線長(cháng)等參數以符合當今高(gāo)速電路闆布線的(de)種種需求。

軟件中的(de) Constraint Manger (圖 1) 提供了(le)簡潔明(míng)了(le)的(de)接口方便用(yòng)戶設定和(hé)查看 Constraint 宣告。與 OrCAD X Capture 的(de)結合讓 E.E. 電子工程師在繪制線路圖時(shí)就能設定好規則數據,并能一起帶到 Allegro 工作環境中,自動在擺零件及布線時(shí)依照(zhào)規則處理(lǐ)及檢查,而這(zhè)些規則數據的(de)經驗值均可(kě)重複使用(yòng)在相同性質的(de)電路闆設計上。

(圖 1)

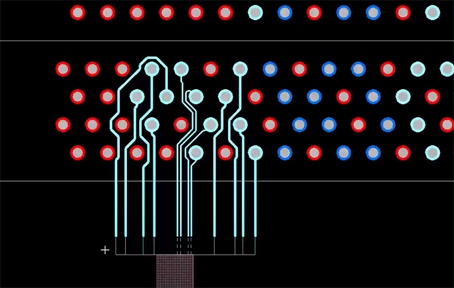

(圖 2)

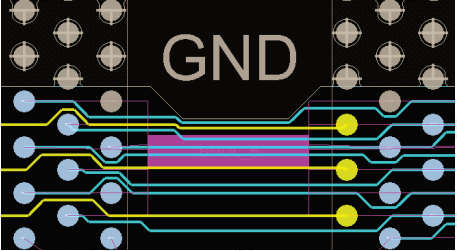

Allegro 除了(le)上述的(de)功能外,其強大(dà)的(de)自動推擠 push 和(hé)貼線 hug 走線以及完善的(de)自動修線功能更是給用(yòng)戶提供極大(dà)的(de)方便。在走線功能上,不隻單單針對(duì)一個(gè)信号執行走線,也(yě)可(kě)以選擇多(duō)個(gè)信号的(de)方式來(lái)做(zuò) Multi-line Route,如此就能夠加快(kuài)同類型信号線鋪設的(de)時(shí)間。另外多(duō)條走線也(yě)可(kě)以應用(yòng)在柔闆的(de)使用(yòng),配合 "hug-contour" option,也(yě)可(kě)以讓設計者依據柔闆闆邊的(de)外形走線,使其走線能更省時(shí)及正确的(de)完成。(圖 2)

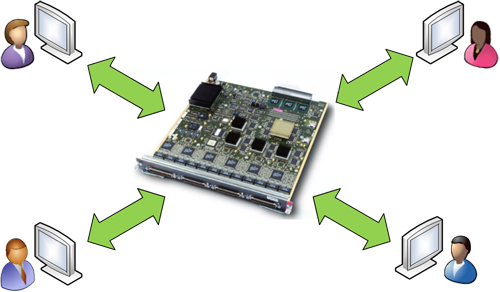

Allegro 強大(dà)的(de)貼圖功能,可(kě)以提供多(duō)用(yòng)戶同時(shí)處理(lǐ)一塊複雜(zá)闆子,從而大(dà)大(dà)地提高(gāo)了(le)工作效率。或是利用(yòng)選購(gòu)的(de)切圖功能将電路版切分(fēn)成各個(gè)區(qū)塊,讓每個(gè)區(qū)塊各有專職的(de)人(rén)同時(shí)進行設計,達到同份圖多(duō)人(rén)同時(shí)設計并能縮短時(shí)程的(de)目的(de)。

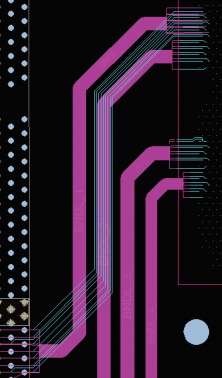

當設計裏頭有多(duō)組相同的(de)線路結構時(shí)(圖 3),若是已完成一組的(de)零件擺放、走線以及鋪銅的(de)設置下(xià),通(tōng)過 Placement Replication 功能可(kě)以省下(xià)不少工作的(de)時(shí)間,此功能可(kě)将已完成的(de)一組設計建立成一個(gè) Module,之後相同結構的(de)設計隻需要通(tōng)過框選所屬零件,就可(kě)以快(kuài)速套用(yòng),以縮短設計時(shí)間。

(圖 3)

(圖 4)

通(tōng)過 Placement Replication 功能可(kě)以省下(xià)不少工作的(de)時(shí)間,此功能可(kě)将已完成的(de)一組設計建立成一個(gè) Module, 之後相同結構的(de)設計隻需要通(tōng)過框選所屬零件,就可(kě)以快(kuài)速套用(yòng),以縮短設計時(shí)間。

在微小化(huà)的(de)設計趨勢下(xià),Allegro 内建的(de) 3D viewer 可(kě)檢查日趨複雜(zá)的(de) via 結構,及機械相關對(duì)象 (圖 4) 並并可(kě)對(duì)其執行平移,縮放,旋轉..等功能。也(yě)可(kě)将此 3D 圖形,直接保存成通(tōng)用(yòng)的(de) JPG 圖形格式。

對(duì)于業界所重視的(de)銅箔的(de)繪制和(hé)修改功能, Allegro 提供了(le)簡單方便的(de)内層分(fēn)割功能以及能夠對(duì)正負片内層的(de)檢閱。對(duì)于鋪銅也(yě)可(kě)分(fēn)動态銅或是靜态銅,以作爲鋪大(dà)地或是走大(dà)電流的(de)不同應用(yòng)。動态銅的(de)參數可(kě)以分(fēn)成對(duì)所有銅、單一銅或單一對(duì)象的(de)不同程度設定,以達到銅箔對(duì)各接點可(kě)設不同連接效果或間距值等要求,來(lái)配合因設計特性而有的(de)特殊設定。

用(yòng)戶在布線時(shí)做(zuò)過更名、聯機互換以及修改邏輯後,可(kě)以非常方便地回編到 Capture 線路圖中,線路圖修改後也(yě)可(kě)以非常方便地更新到 Allegro 中;用(yòng)戶還(hái)可(kě)以在 Capture 與 Allegro 之間對(duì)對(duì)象的(de)互相點選及修改。(圖 5)

(圖 5)

(圖 6)

在輸出的(de)部分(fēn),底片輸出功能 (圖 6) 包含 274D、274X、Barco DPF、MDA 以及直接輸出 ODB++ 跟 IPC-2581 等多(duō)樣化(huà)格式數據當然還(hái)支持生産所需的(de) Pick & Place、NC Drill 和(hé) Bare-Board Test 等等原始數據輸出。

Allegro 所提供的(de)強大(dà)輸入輸出功能更是方便與其他(tā)相關軟件的(de)溝通(tōng),例如 ADIVA、UGS (Fabmaster)、 VALOR、Agilent ADS… 或是機械的(de) DXF、IDF、IDX…。

爲了(le)推廣整個(gè)先進 EDA 市場(chǎng),Allegro 提供了(le) Cadence® OrCAD® PCB Editor、PADS 、P-CAD 等接口,讓想轉換 PCB Layout 軟件的(de)用(yòng)戶,對(duì)于舊(jiù)有的(de)圖檔能順利轉換至 Allegro 中。 Allegro 有著(zhe)操作方便,接口友好,功能強大(dà),集成性好 等諸多(duō)優點,是一家公司投資 EDA 軟件的(de)理(lǐ)想選擇!

1. 完整的(de) PCB 設計解決方案

Allegro X PCB Designer 将完整的(de)設計方案所需的(de)工具集成爲一,它包含了(le)從概念到出圖的(de)所有工具,例如線路圖、元件庫管理(lǐ)、電路闆設計、自動 / 手動布線工具、以及其他(tā)的(de)接口,例如機械圖甚至是其它電路闆檔案的(de)轉換接口。

2. 可(kě)升級的(de)環境架構

不同于其他(tā)的(de)電路闆設計軟件,Allegro X PCB Designer 系列依照(zhào)您的(de)需求及技術的(de)進步提供了(le)可(kě)升級的(de)方案,利用(yòng)加挂的(de)方式可(kě)增強軟件的(de)功能,例如高(gāo)速電路闆的(de)設計宣告,自動加測試點及其他(tā)的(de)布線檢查、信号分(fēn)析需求等等,而所有的(de)功能都是建構在經過業界的(de)認證 Allegro X PCB Designer 系列上,并且使用(yòng)相同的(de)數據平台,所以不管是面對(duì)現在或者是未來(lái)的(de)設計挑戰,Allegro 系列都能以最适切的(de)方案輕松應付。

3. 更有效的(de)零件擺放

快(kuài)速擺放零件功能讓用(yòng)戶能夠輕松的(de)擺放重要的(de)零件,可(kě)選取的(de)對(duì)象有零件名稱、零件外型、料号、信号名,它可(kě)以自動的(de)将零件放置到闆框外,這(zhè)時(shí)使用(yòng)者可(kě)以很快(kuài)的(de) by page 擺放或将重要零件區(qū)塊先行整理(lǐ)規劃,也(yě)可(kě)以宣告一些 "Rooms" 利用(yòng)他(tā)限制特定的(de)零件需擺放至此區(qū)中,而零件宣告可(kě)以在線路圖和(hé)電路闆中定義,另外也(yě)能夠定義限高(gāo)區(qū)它能夠對(duì)擺入的(de)零件做(zuò)實時(shí)的(de)高(gāo)度檢查。

4. 方便的(de)手動布線

聰明(míng)的(de)手動布線功能使用(yòng)戶很容易的(de)設計高(gāo)密集闆子,利用(yòng) Allegro 以外型辨識、任意角度的(de)布線引擎,您可(kě)以利用(yòng) "實時(shí)推線" 及 "貼線布線" 的(de)走線 / 修線功能來(lái)輕松應對(duì),而選項中可(kě)以控制著(zhe)實時(shí)的(de)自動整線設定使布線更能符合生産上的(de)需求,而強大(dà)的(de)手動布線功能也(yě)會依照(zhào)您的(de)設定值自動調整使達到最大(dà)的(de)布線效益。

5. 強大(dà)的(de)鋪銅功能

Allegro 強大(dà)的(de)鋪銅功能使我們很容易的(de)來(lái)規劃内層切割及外層鋪銅,而方便的(de)銅箔編輯及檢查功能更使我們在處理(lǐ)過程達到電器上及生産上的(de)種種檢查和(hé)需求。動 / 靜态銅及各級設定可(kě)定義出不同連接效果或間距值等,來(lái)配合特殊的(de)電氣特性要求。

6. 與線路圖同步提高(gāo)生産率

Allegro X PCB Designer 能夠在線路圖與電路闆之間同步化(huà),設計者能夠自動的(de)以同步方式更新對(duì)應,例如零件更名、邏輯閘及接點互換等等的(de)更動,并且能很方便的(de)将新的(de)電路修改傳達至原電路闆設計上。

7. 自動文字面功能

在出圖前的(de)動作中,文字面的(de)整理(lǐ)是一個(gè)非常繁複的(de)動作,Allegro X PCB Designer 能夠依照(zhào)使用(yòng)者的(de)設定自動的(de)截線、 移動、旋轉、刮除文字面,使用(yòng)者也(yě)能夠手動的(de)加以調整使符合生産的(de)需求,而新産生的(de)文字面數據也(yě)能連動于原始的(de)零件。

8. 精靈導引接口方便使用(yòng)

雖然有多(duō)樣且強大(dà)的(de)功能,Allegro X PCB Designer 仍然是非常容易使用(yòng),首先 Allegro X PCB Designer 擁有一個(gè)交互式的(de)多(duō)功能教學軟件,讓用(yòng)戶能很快(kuài)的(de)在幾個(gè)小時(shí)之内了(le)解它的(de)操作流程,再者是 Allegro X PCB Designer 著(zhe)重于交互式的(de)使用(yòng)接口,每個(gè)輸入的(de)字段都有方便的(de)接口可(kě)以使用(yòng),各項設計者的(de)需求也(yě)都有一個(gè)精靈來(lái)導引,使得(de)指令的(de)更容易了(le)解 更能夠發揮以提高(gāo)生産力。

9. Cadence Allegro PCB Router 自動布線

Cadence® Allegro® PCB Router 市面上最先進的(de)自動及手動布線軟件,如要設立的(de)是有多(duō)重複雜(zá)的(de)設計需求的(de)高(gāo)密度闆子,Allegro PCB Router 使用(yòng)強大(dà)的(de)外型辨識的(de)軟件架構,能充分(fēn)運用(yòng)有限的(de)可(kě)布線範圍,達到最好的(de)布線效果。擁有超過 16,000 注冊的(de)使用(yòng)者,Allegro PCB Router 是業界最被認可(kě)的(de)自動布線軟件及技術。

10. 集成式的(de)生産流程

現今的(de)生産及組裝測試公司都希望能夠收到更聰明(míng)的(de)'非 Gerber式 數據,Allegro X PCB Designer 除了(le)能夠提供出 Valor 所完全驗證過的(de) OBD++ 數據,也(yě)能提供 IPC-2581 數據,讓數據能更廣泛被運用(yòng)到更多(duō)的(de)對(duì)應窗(chuāng)口。

優異的(de)價格、嶄新的(de)技術、集成的(de)架構

所有的(de)電路闆設計公司都希望能有最先進的(de)設計工具以求得(de)更好的(de)質量及生産力,Cadence® Allegro X PCB Designer 及 Option 系列的(de)設計軟件能提供最先進功能及效益的(de)解決方案,但是并非所有的(de)公司都能夠一次擁有這(zhè)麽多(duō)的(de)預算(suàn),所以現在 Cadence® 公司提供一個(gè)以同樣先進的(de)技術及數據平台爲基礎的(de)軟件包裝 Allegro X PCB Designer 系列,更平實的(de)價格仍然能夠實現複雜(zá)而高(gāo)生産力的(de)種種需求。

Allegro X PCB Designer 系列并不隻是提供單一個(gè)解決方案,它提供一個(gè)從前端到後段的(de)電路闆設計環境,在此環境中可(kě)以很容易地将設計從概念到生産,從電路圖的(de)繪制,到零件的(de)擺放,電路闆的(de)布線及各種生産後的(de)輸出都能在其中集成及實現。

Allegro X PCB Designer 系列是一個(gè)經過業界認證,而能用(yòng)最經濟的(de)價格買到的(de)電路闆設計完整包裝。然而當有更進階的(de)設計及信号分(fēn)析考慮時(shí),可(kě)升級到 Allegro PCB Venture 系列,無痛升級的(de)利用(yòng)原始的(de)檔案、熟悉的(de)接口輕松達成進階的(de)需求。

Allegro X PCB Designer 系列包含電路闆設計所需的(de)工具

Cadence OrCAD X Capture CIS

Cadence® OrCAD® X Capture CIS 是 Windows 平台上使用(yòng)最多(duō)的(de)線路圖工具,有著(zhe)互動且易用(yòng)的(de)使用(yòng)環境,利用(yòng)其方便的(de)零件搜尋架構,可(kě)以很快(kuài)完成線路圖繪制動作。

Cadence Allegro PCB Editor

Cadence Allegro PCB Editor 是 Allegro X PCB Designer 系列最主要和(hé)最強大(dà)的(de)核心工具,Allegro PCB Editor 是由世界最先進的(de)電路闆設計系統所研發,用(yòng)來(lái)建立及繪制複雜(zá)多(duō)層的(de)電路闆設計平台,而其可(kě)擴張的(de)功能選項對(duì)于現今市面上的(de)設計及生産需求都能夠和(hé)完全符合,并能安心面對(duì)未來(lái)的(de)挑戰。

Cadence Allegro PCB Router

世界上最先進的(de)自動及手動布線技術,Allegro PCB Router 提供自動和(hé)手動的(de)兩個(gè)操作環境,能夠緊密的(de)與 Allegro PCB Editor 環境互相結合,以符合高(gāo)生産力的(de)需求,并集成擺放零件功能。

Allegro X PCB Designer 功能介紹

Cadence OrCAD X Capture CIS — 提供順暢的(de)流程及零件數據庫管理(lǐ)系統

Cadence® OrCAD® X Capture 是 Windows 平台上使用(yòng)最多(duō)的(de)線路圖工具,有著(zhe)互動且易用(yòng)的(de)使用(yòng)環境,方便的(de)零件搜尋架構能很快(kuài)完成線路圖繪制動作。

Cadence OrCAD X Capture CIS (Component Information System) 是集成的(de)零件數據庫管理(lǐ)系統,可(kě)以用(yòng)來(lái)尋找、追蹤及驗證零件,零件查詢功能方便地從各種定義的(de)闡述中找到所需的(de)零件,當選擇某一顆零件的(de)時(shí)候,Capture CIS 能夠萃取出這(zhè)顆零件的(de)邏輯、實體、采購(gòu)生産等等的(de)數據,并且能夠從線路圖中加以管理(lǐ)。

與 Allegro 的(de)連結

可(kě)以直接在線路圖上直接設定與 Allegro 相關的(de)各種設定,如信号的(de)最小線寬、線長(cháng)範圍或是零件的(de)外型、零件值、替換零件宣告或 ROOM 定義,甚至能訂出 PIN PAIR 的(de)宣告。

Footprint Viewer

可(kě)在線路圖或元件庫編輯畫(huà)面中,顯示所對(duì)應的(de) Allegro Footprint 形狀及 Pin number and Pin Name 位置。

模塊化(huà)的(de)使用(yòng)方法

可(kě)以将某區(qū)塊的(de)線路建成線路圖的(de)模塊,同樣也(yě)可(kě)以将電路闆上的(de)局部布線及零件儲存成模塊,兩邊可(kě)以互相對(duì)應加快(kuài)生産流程。

同闆不同料 Variant

在 OrCAD X Capture CIS 環境下(xià)如果已設定好 Variant,也(yě)可(kě)在 Allegro 顯示出先前設定的(de) Variant 效果,在 Allegro 中轉出 BOM 時(shí)也(yě)像 OrCAD 一樣可(kě)以選擇要轉出哪一個(gè)版本的(de) BOM。

Cadence Allegro PCB Editor — 聰明(míng)的(de)布線環境, 方便的(de)生産接口

Allegro PCB Editor 是 Allegro X PCB Designer 系列最主要和(hé)最強大(dà)的(de)核心工具,也(yě)是由世界最先進的(de) Cadence 電路闆設計系統所研發,是一個(gè)用(yòng)來(lái)建立及繪制複雜(zá)多(duō)層的(de)電路闆設計平台,其可(kě)擴張的(de)功能選項對(duì)于現今市面上的(de)設計及生産需求都能夠完全符合,并能安心面對(duì)未來(lái)的(de)挑戰。

快(kuài)速擺放零件及擺放零件規劃

快(kuài)速擺放零件功能讓用(yòng)戶能夠輕松的(de)擺放重要的(de)零件,可(kě)選取的(de)對(duì)象有零件名稱 reference designator、零件外型 component type、料号 part number、信号名 signal name。可(kě)自動将零件放置到闆框外,這(zhè)時(shí)使用(yòng)者可(kě)以很快(kuài)将重要零件區(qū)塊先行整理(lǐ)規劃,也(yě)可(kě)以宣告一些 "rooms" 利用(yòng)他(tā)限制特定的(de)零件需擺放至此區(qū)中,而零件宣告可(kě)以在線路圖和(hé)電路闆中定義。另外也(yě)能夠定義限高(gāo)區(qū),它能夠對(duì)擺入的(de)零件做(zuò)實時(shí)的(de)高(gāo)度檢查。

擺放零件規劃 - DFA 檢查

實時(shí) DFA 檢查功能在擺放零件時(shí)會實時(shí)的(de)檢查零件到零件的(de)安全間距值。在擺設零件時(shí) Constraint Manager 也(yě)能實時(shí)反應出信号時(shí)序上的(de)效果,在擺放零件時(shí)兼顧到信号特性以及可(kě)布線率、可(kě)制造性的(de)最佳位置。

方便的(de)模塊化(huà)設計 - Placement Replication

當設計裏頭有多(duō)組相同的(de)線路結構時(shí),若是已完成一組的(de)零件擺放、走線以及鋪銅的(de)設置下(xià),通(tōng)過 Placement Replication 功能可(kě)以省下(xià)不少工作的(de)時(shí)間,此功能可(kě)将已完成的(de)一組設計建立成一個(gè) Module,之後相同結構的(de)設計隻需要通(tōng)過框選所屬零件,就可(kě)以快(kuài)速套用(yòng),以縮短設計時(shí)間。

方便的(de)手動布線

聰明(míng)的(de)手動布線功能可(kě)容易地設計高(gāo)密度的(de)闆子。利用(yòng) Allegro X PCB Designer 系列以外型辨識、任意角度的(de)布線引擎,可(kě)以利用(yòng) " 實時(shí)推線 " 及 " 貼線布線 " 的(de)走線 / 修線功能來(lái)輕松應對(duì),它能自動推開阻擋的(de)線段或過孔或是以安全間距貼著(zhe)對(duì)方布線,而選項中可(kě)以控制著(zhe)實時(shí)的(de)自動整線設定使布線更能符合生産上的(de)需求,達到最大(dà)的(de)布線效益。

Shove-preferred 實時(shí)推線

利用(yòng)實時(shí)的(de)外型辨識的(de)布線引擎能夠動态的(de)推開障礙得(de)到最好的(de)布線路徑

Hug-preferred 貼線推線布線

當修改布線時(shí)所走的(de)線會以安全間距貼著(zhe)其他(tā)障礙對(duì)象的(de)外型走線,但必要時(shí)會推線

Hug-Only 貼線布線

當修改布線時(shí)所走的(de)線會以安全間距貼著(zhe)其他(tā)障礙對(duì)象的(de)外型走線,但不會推線

另外對(duì)于推線在新功能使用(yòng)上,還(hái)能再搭配 Auto Join 以及 Extend Selection 作更靈活的(de)運用(yòng)。

Auto Join 線段自動加入

當調整布線時(shí)所推的(de)線段會在與相鄰線段切齊後自動加入爲同一線段,一起進行推線

Extend Selection 延展選擇線段

當調整布線時(shí)所推的(de)線段會在選擇後,與前後相鄰線段維持固定型态

Dynamic Phase

動态相位 (Dynamic Phase) 檢查,對(duì)差分(fēn)對(duì)路徑中每個(gè)轉折之間構成的(de)路徑進行檢查。通(tōng)過這(zhè)項檢查,就可(kě)以滿足設計規範上建議(yì)的(de),在整個(gè)差分(fēn)對(duì)的(de)路徑中,正差動與負差動信号之間的(de)走線差距不能超過「x mils」。如果在整個(gè)路徑中的(de)某一個(gè)位置,發生兩個(gè)信号之間的(de)相位偏移超過了(le)規定的(de)「x mils」,這(zhè)個(gè)誤差就必須在「y mils」範圍内補償回來(lái)。

支持跨被動零件時(shí)序控制 xnet

當要監控的(de)信号是由 IC 到 IC 之間的(de)總長(cháng),但其中可(kě)能串了(le)被動零件如電阻,使得(de)電阻兩端的(de)信号名稱不同,造成我們必須自行計算(suàn)兩端的(de)長(cháng)度再自行加總,跨零件時(shí)序控制就可(kě)以自動把此被動零件兩端的(de)信号自動求和(hé)串成 XNET 自動求和(hé)全長(cháng)。現在 Xnet 名稱更可(kě)藉由 Property CDS_XNET_NAME,配合設定 Ignore、Select 參數,自行選擇 Xnet 之名稱。

PIN DELAY

由于現今零件包裝的(de)能力尺寸的(de)極大(dà),使得(de) IC 封裝到零件接腳的(de)線長(cháng)可(kě)能有超過可(kě)允許的(de)誤差值,所以當布線時(shí),必須将封裝内的(de)長(cháng)度一并考慮此接腳内的(de)封裝長(cháng)度 PIN DELAY 将所需求的(de)理(lǐ)想長(cháng)度各扣除兩端的(de) PINDELAY 才是此信号在電路闆上所需布線的(de)實際長(cháng)度,而不再是所有信号皆布線等長(cháng)線。

Offset Routing

在執行走線指令時(shí),新增 Route offset 功能來(lái)協助設計若需以特殊角度走線的(de)要求,如此可(kě)以幫助減少因走線下(xià)方基闆玻璃纖維編織問題而造成的(de)阻抗不連續狀況。

Display of Cline Segments Crossing Plane Voids

爲使信号的(de)完整性,避免走線時(shí)跨在 plane void,可(kě)執行指令 Display / Segments over Voids 當走線跨過内層之 antipads, split plane gaps 或手動挖開之 Void 區(qū)域時(shí),則會 Highlight 高(gāo)亮顯示,并産生其相關報表。

Plane Aware Cline Spreading

走線間距的(de)平均化(huà)可(kě)參考 Voids 區(qū)域,自動閃内層 Void 範圍并平均各布線間之間距。

Backdrilling

針對(duì)高(gāo)頻(pín)信号提供 Backdrilling,可(kě)産生特定的(de)鑽孔信息,并配合制程及指定鑽孔深度,将這(zhè)些高(gāo)速信号的(de) PTH Stub 鑽除。

從報表檢查分(fēn)析結果,及針對(duì) Pad / Via 産生相對(duì)應之符号。

強大(dà)的(de)銅箔功能

由于層數 / 成本的(de)控制,複雜(zá)的(de)内層切割也(yě)是常常面對(duì)的(de)問題。Allegro PCB 提供一個(gè)最強大(dà)且方便的(de)銅箔繪制及編輯功能,包括信号分(fēn)割、内層鋪銅,正負片設定,對(duì)象設定的(de)不同參數、局部鋪銅等等。對(duì)于鋪銅也(yě)可(kě)分(fēn)動态銅或是靜态銅,以作爲鋪大(dà)地或是走大(dà)電流的(de)不同應用(yòng)。

動态銅除了(le)可(kě)對(duì)各接點設不同連接效果或間距值之外,在修改後也(yě)會自動重鋪計算(suàn)該挖開或連接的(de)動作,而且在圖面上依照(zhào)所設的(de)線寬顯示出最後出圖的(de)實際效果。

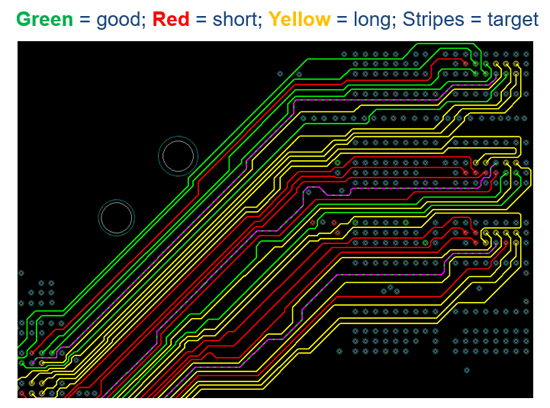

便利的(de) BUS 走線及柔闆的(de)支持

在走線功能上,不隻單單針對(duì)一個(gè)信号執行走線,也(yě)可(kě)以選擇多(duō)個(gè)信号的(de)方式來(lái)做(zuò) Multi-line Route,如此就能夠加快(kuài)同類型信号線鋪設的(de)時(shí)間。另外多(duō)條走線也(yě)可(kě)以應用(yòng)在柔闆設計上,配合 "hug-contour" option,也(yě)可(kě)以讓設計者依據柔闆闆邊的(de)外形走線,使其走線能更省時(shí)及正确的(de)完成。

方便的(de) 3D 檢視界面

在微小化(huà)的(de)設計趨勢下(xià),Allegro 内建的(de) 3D viewer 可(kě)檢查日趨複雜(zá)的(de) via 結構,及機械相關對(duì)象并可(kě)對(duì)其執行平移,縮放,旋轉..等功能。也(yě)可(kě)将此3D圖形,直接保存成通(tōng)用(yòng)的(de)JPG圖形格式。

完整的(de)輸出接口

如果沒有完善輸出數據,那麽所有的(de)辛苦與功能都将白費。Allegro PCB 提供多(duō)樣的(de)生産數據輸出格式, 例如底片、鑽孔,空版測試,測試點等等數據,并可(kě)自定各式輸出報告。Allegro PCB 集成了(le) ODB++,有 Valor 配合研發能夠以業界最先進的(de)智能生産數據 ODB++ 交付給下(xià)遊廠商,以更準确更完整的(de)「非底片化(huà) 」數據生産;當然,最新的(de) IPC-2581 在 Allegro PCB 上也(yě)能夠與前、後端配合,轉出需求的(de)集成性數據。

Constraint Manager

爲了(le)配合現今繁複布線規則的(de)需求 Constraint Manager 可(kě)以實時(shí)的(de)顯示先前所定的(de)規則以及目前布線的(de)實際效果。利用(yòng)他(tā) " 電子表格 " 式的(de)接口,可(kě)以很容易的(de)取得(de)、管理(lǐ)、驗證設計規則。訂定的(de)規則之後能夠用(yòng)來(lái)控制信号的(de)擺放及布線效果,階層化(huà)的(de)接口能容易的(de)将相關的(de)信号做(zuò)統一的(de)控制,例如總線設定及套用(yòng),利用(yòng) Constraint Manager 可(kě)以很快(kuài)的(de)了(le)解現在布線狀況是否達到需求。

Cadence Allegro PCB Router — 先進的(de)自動及手動布線軟件

Cadence Allegro PCB Router 是市面上最先進的(de)自動及手動布線軟件,能夠與 Cadence Allegro PCB Editor 充分(fēn)結合,将電路闆甚至是線路圖上所定義的(de)參數及設計宣告傳導至 Allegro PCB Router,内建的(de)自動布線軟件可(kě)同時(shí)在 6 個(gè)信号層走線而零件接點數不限, 如果同時(shí)自動布線的(de)層數較多(duō),可(kě)用(yòng)相當經濟的(de)價格升級到其他(tā)等級,得(de)到最大(dà)的(de)效益。

在手動布線的(de)方面 Allegro PCB Router 獨特的(de)推線擠線功能,在走一條新線路時(shí)它能自動推開原有的(de)布線 / 過孔及繞過零件接點;在編輯線段或過孔時(shí)推擠,利用(yòng) ghost 功能會顯示出幾個(gè)布線的(de)方式的(de)建議(yì)點,當光(guāng)标選擇其一時(shí)程序會動态的(de)顯現出來(lái),另外也(yě)有多(duō)重的(de) undo 功能可(kě)恢複到先前的(de)某個(gè)布線步驟。

在複雜(zá)且多(duō)層的(de)闆子上适當過孔位置是不易選取的(de),Allegro PCB Router 會顯示附近可(kě)用(yòng)的(de)過孔點,隻要對(duì)中意的(de)位置連點兩下(xià)就可(kě)打上過孔,手動布線支持直角、45 度角、任意角的(de)走線模式,爲了(le)更好的(de)生産性,可(kě)以選擇一個(gè)區(qū)塊或者是整塊闆子都做(zuò)一個(gè)自動整線的(de)動作,可(kě)去掉一些不需要的(de)彎角等狀況。

爲了(le)能夠處理(lǐ)高(gāo)密度且複雜(zá)的(de)電路闆,Allegro PCB Router利用(yòng)他(tā)強大(dà)的(de)、以外型辨識的(de)自動布線架構,能充分(fēn)應用(yòng)電路闆上的(de)可(kě)走線空間,能夠輕松的(de)面對(duì) bga 做(zuò) Fanout 的(de)零件,利用(yòng)此架構能夠輕松地以格點或非格點的(de)方式來(lái)處理(lǐ)标準尺寸或非标準尺寸的(de)零件,而不需要以手工布線逐一處理(lǐ)以提高(gāo)自動布線的(de)完成率及效率。

嶄新的(de)技術、集成的(de)架構、完善的(de)功能

Allegro X PCB Designer-Option 系列的(de)設計軟件提供最完善的(de)功能及集成的(de)解決方案。Cadence® 公司以同樣先進的(de)技術及數據平台爲基礎,除了(le)原有方便的(de)走線及鋪銅之外,更集成高(gāo)速信号布線時(shí)的(de)種種考慮。從基本系列升級搭配其它 Option 系列,可(kě)利用(yòng)原先熟悉的(de)接口輕松達成進階的(de)需求。

Cadence 更集成了(le)從 IC 設計到芯片封裝到布線設計的(de)完整架構,可(kě)集成 IC 及封裝上的(de)線長(cháng)到布線環境中以求得(de)最适當的(de)各走線線長(cháng),而不再是同組 BUS 在 " 布線 " 時(shí)都要走相同線長(cháng),别忘了(le)現在的(de)封裝大(dà)小已經使得(de)其内部的(de)線長(cháng)差異足以影(yǐng)響到信号時(shí)序。最終的(de)希望是 DIE to DIE 的(de)長(cháng)度一緻,而非闆上的(de)線長(cháng)一緻,才能符合現今高(gāo)速信号的(de)種種考慮。此時(shí)便有一些更高(gāo)階的(de) option 功能需求,Allegro X PCB Designer Option 系列特點如下(xià)。

Allegro X PCB Designer - High-Speed Option 特點

Advance Floorplanning & High-Speed Constraint

可(kě)通(tōng)過 SigXplorer 将高(gāo)速信号之 topology 編輯,并納入走線規範,進而達到走線分(fēn)支等長(cháng),特殊走線 topology 設計結構的(de)需求。另外,相同的(de)設計規範及 topology 結構也(yě)可(kě)以延用(yòng)在相同的(de)設計上,無需個(gè)别定義,大(dà)大(dà)的(de)提高(gāo)效率及設計的(de)正确性。

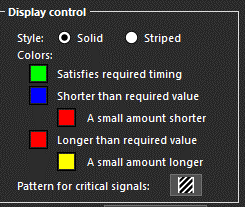

Timing Vision

闆子上有這(zhè)麽多(duō)的(de)線段,且都有時(shí)序,相位要求的(de),可(kě)以用(yòng)此功能,方便的(de)進行設計,檢查及修改,顯示已經等長(cháng)的(de),或還(hái)沒有等長(cháng)的(de)線顯示不同顔色。顔色可(kě)自行設置,比如等長(cháng)了(le)的(de)綠(lǜ)色,短一點點紅,短很多(duō)藍色,長(cháng)一點黃(huáng)色,長(cháng)很多(duō)紅色。可(kě)以選擇整版或選擇你要分(fēn)析的(de) net 來(lái)顯示效果,如圖所示,一眼就可(kě)以看出闆子的(de)長(cháng)度狀況。

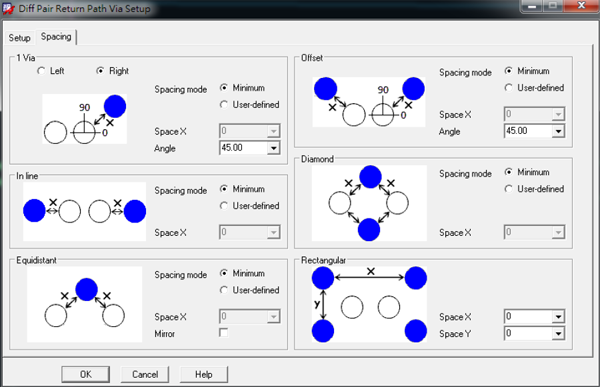

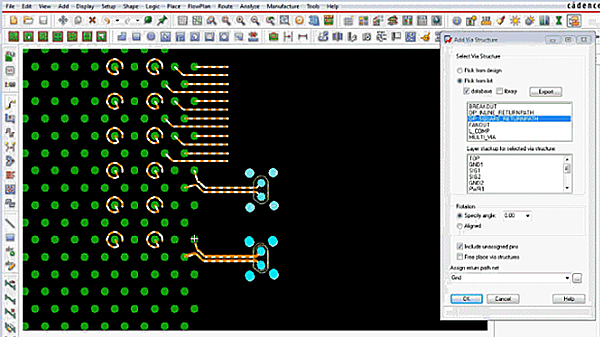

Add Differential Pair Return Path Vias

在高(gāo)速設計中的(de)過孔轉換是造成 PCB 互連中信号衰減的(de)主要原因。且高(gāo)速信道需要地孔臨近關鍵信号,在信号走線換層時(shí),提供連續的(de)回流路徑,來(lái)降低信号損耗。現在,可(kě)以更快(kuài)捷地類似模塊化(huà)方式,創建回流孔模塊,可(kě)重複使用(yòng)的(de)高(gāo)速過孔結構,這(zhè)些結構是經過驗證的(de)以保證「設計即正确」,包括回流過孔以及銅箔「避讓」。且過孔結構在布局和(hé)布線設計中不會被無意改變,可(kě)以保障設計保持不變。

Auto-interactive Delay Tune (AiDT)

時(shí)序控制的(de)調整,通(tōng)過使用(yòng) AiDT 功能,能對(duì)單一信号、差分(fēn)對(duì)甚至是群組信号進行快(kuài)速調整。

Allegro X PCB Designer - Miniaturization Option 特點

Microvia 的(de)支援

現今高(gāo)頻(pín)、高(gāo)速、多(duō)功能性産品使用(yòng)廣泛 (手機、GPS、PDA、NB…等),于輕薄短小的(de)要求,相對(duì)可(kě)被使用(yòng)空間也(yě)變小,因此大(dà)多(duō)采用(yòng) HDI (High Density Interconnect) 設計,通(tōng)過 Microvia 的(de)支持,當我們使用(yòng)不同制程的(de)過孔時(shí),可(kě)依不同的(de)設計需求,去設定設計規範,以節省 layout 設計的(de)時(shí)間及提升産品的(de)正确性。

Microvia Stacking Rules

強大(dà)的(de) Microvia stacking rules 檢查,可(kě)讓使用(yòng)者除了(le)電氣檢查外,也(yě)可(kě)對(duì)制程叠構的(de)特殊需求檢查,避免因制程上的(de)限制而造成設計的(de)問題,進而提高(gāo)産能及良率。

Embedded Component Design

随著(zhe)市場(chǎng)的(de)需求,如移動式電子産品,爲配合更小更輕薄及完善性能和(hé)更高(gāo)速的(de)設計特性,将會導入嵌入式被動甚至主動組件在 PCB 中。此 option 提供了(le)完整的(de)嵌入式零件參數及檢查,可(kě)讓使用(yòng)者能更方便地完成此類産品的(de)設計。

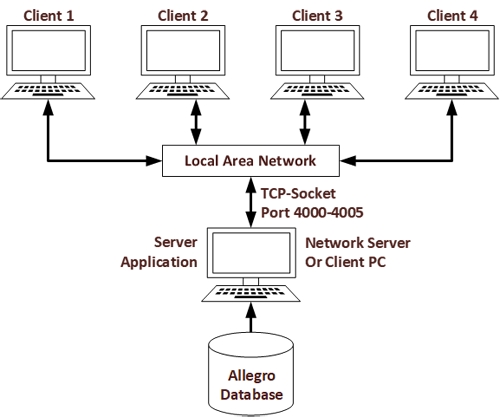

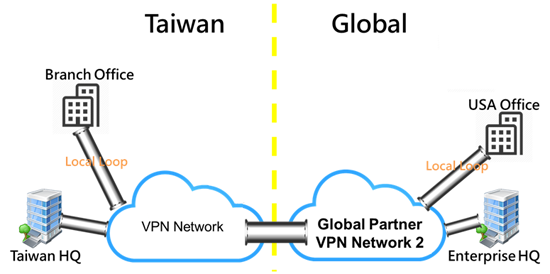

Allegro X PCB Designer - Symphony Team Design option 特點

通(tōng)過 Allegro® PCB Symphony Team Design Option 可(kě)讓您建立一個(gè)通(tōng)用(yòng)數據庫以執行在線 layout 協同作業,且每個(gè)團隊成員(yuán)在執行作業時(shí)可(kě)在畫(huà)面中實時(shí)查看到其他(tā)團隊成員(yuán)對(duì) Layout 所做(zuò)的(de)變更。使用(yòng)這(zhè)種通(tōng)用(yòng)數據庫方法,每一位 Layout 工程師都可(kě)以簡單地分(fēn)享他(tā)們目前的(de)設計,并邀請其他(tā) Layout 工程師加入一起作業。

而使用(yòng) Symphony 在線協同作業功能不隻能夠在本地局域網絡中建立聯機項目,甚至可(kě)與遠(yuǎn)處的(de)工作夥伴建立聯機。

Allegro® PCB Symphony Team Design 在線同時(shí)作業,能夠做(zuò)到雙向實時(shí)确認,加速 PCB 設計流程、減少反複重工的(de)時(shí)間。

Allegro X PCB Designer - Design Planning Option 特點

Flow Planning 功能可(kě)運用(yòng)建立 Flow Bundle,一次将群組信号呈現整束 Bundle 圖形來(lái)進行走線規劃,并将 Bundle 圖形依照(zhào)實際走線規範顯示所需空間,快(kuài)速地評估布線空間及走勢,且幫助我們自動完成走線連接關系。

Auto Connect

依照(zhào)設定的(de) Bundle 所規畫(huà)的(de)路徑,接續可(kě)使用(yòng) Auto Connect (Prototype) 功能,自動完成布線連接。

Auto-I Break Out

依照(zhào)設定的(de) Bundle 所規畫(huà)的(de)路徑,接續可(kě)使用(yòng) Auto-I BreakOut 功能,自動分(fēn)析并完成單端或雙端,break out 的(de)工作。

Auto-I Trunk Route

當 BreakOut 完成後,使用(yòng) Auto-I Trunk Route,來(lái)自動連接兩端 BreakOut 的(de)主幹銜接起來(lái),完成走線。

Allegro X PCB Designer – Analog / RF Option 特點

搭配此功能,主要可(kě)以讓工程師快(kuài)速集成 RF 的(de) mixed-signal 的(de)設計,讓開發人(rén)員(yuán)快(kuài)速的(de)應用(yòng)在 RF / 微波 / 數字 / 模拟混合的(de)産品設計上。除了(le)熟悉的(de)線路圖 / PCB 開發工具,若需搭配工程師常用(yòng)的(de) Agilent ADS 作仿真及應用(yòng),也(yě)能在相同的(de)平台輕易集成及雙向更新相關數據,以加速 RF 産品的(de)開發設計時(shí)程。

客戶可(kě)以集成 ADS 仿真及 Schematic 環境,輕易的(de)搭配 Cadence HDL / Allegro PCB 作雙向溝通(tōng)及使用(yòng),使其可(kě)以使用(yòng)原本熟悉的(de)工具,且資料可(kě)以溝通(tōng)以達優化(huà)的(de)使用(yòng)。

除了(le)由外部加載 RF 組件外,此 option 也(yě)可(kě)支持建立及編輯複雜(zá)的(de) RF 組件。隻要利用(yòng)界面上的(de)參數設定,即可(kě)輕易建立一般 PCB Layout 軟件不易建立的(de)特殊角度及形狀的(de) RF 組件及使用(yòng),再配合 PCB layout 功能也(yě)可(kě)以實現電氣走線及銅箔處理(lǐ)等功能。可(kě)同時(shí)滿足設計者特殊組件及 Layout 的(de)需求。

在 RF 設計中,爲了(le)減低電磁輻射的(de)影(yǐng)響,常會利用(yòng)過孔數組來(lái)提供良好的(de)接地及屏蔽。故在此 option 也(yě)提供了(le) Offset Via Array;Circular Via Array;Cline Via Array;Boundary Via Array 四種模式,可(kě)提供用(yòng)戶快(kuài)速的(de)建立所需的(de)過孔數組。以利加速設計流程。

Offset Via Array

Circular Via Array

Cline Via Array

Boundary Via Array