适用(yòng)于 PCB 和(hé) IC 封裝結構的(de)完整 3D 電磁場(chǎng)解決方案

Cadence® Clarity™ 3D Solver 是一款 3D 全波電磁 (EM) 仿真軟件工具,用(yòng)于設計 PCB、IC 封裝和(hé) IC 系統 (SoIC) 設計之間的(de)關鍵互連。在設計用(yòng)于 5G、汽車、高(gāo)性能計算(suàn) (HPC) 和(hé)機器學習(xí)應用(yòng)的(de)系統時(shí),Clarity 3D Solver 的(de)仿真精度可(kě)達到黃(huáng)金标準,其突破性 EM 仿真技術可(kě)解決最複雜(zá)的(de)電磁 (EM) 挑戰,使您能夠順利完成驗收并成功将系統投入生産過程。

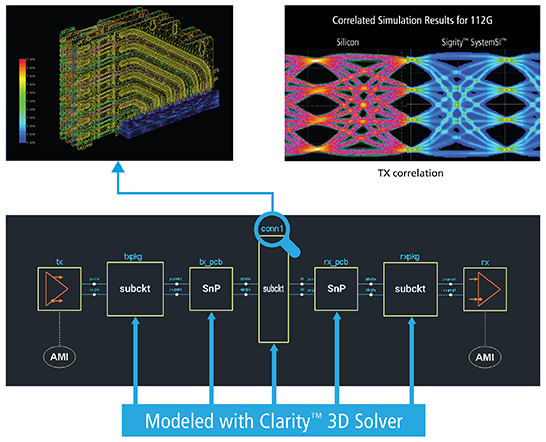

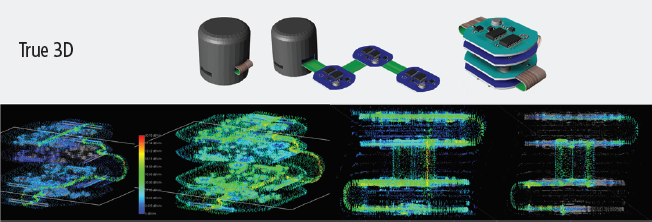

Cadence 業内領先的(de)分(fēn)布式多(duō)處理(lǐ)技術使 Clarity 3D Solver 能夠提供近乎無限的(de)處理(lǐ)能力和(hé)至少10 倍以上的(de)求解速度,利用(yòng)雲端或本地分(fēn)布式計算(suàn),可(kě)以高(gāo)效地解決更龐大(dà)、更複雜(zá)的(de)結構問題。該産品可(kě)創建高(gāo)精度 S 參數模型,用(yòng)于信号完整性 (SI)、電源完整性 (PI) 和(hé)電磁兼容性 (EMC) 分(fēn)析,即使在 112Gbps+ 的(de)數據傳輸速度下(xià),也(yě)可(kě)實現仿真結果與實驗室測量結果的(de)高(gāo)度吻合。Clarity 3D Solver 可(kě)以求解真正完整的(de)全 3D 結構,而無需人(rén)工縮小待建模結構的(de)尺寸。

通(tōng)過並行化(huà)節省設計時(shí)程

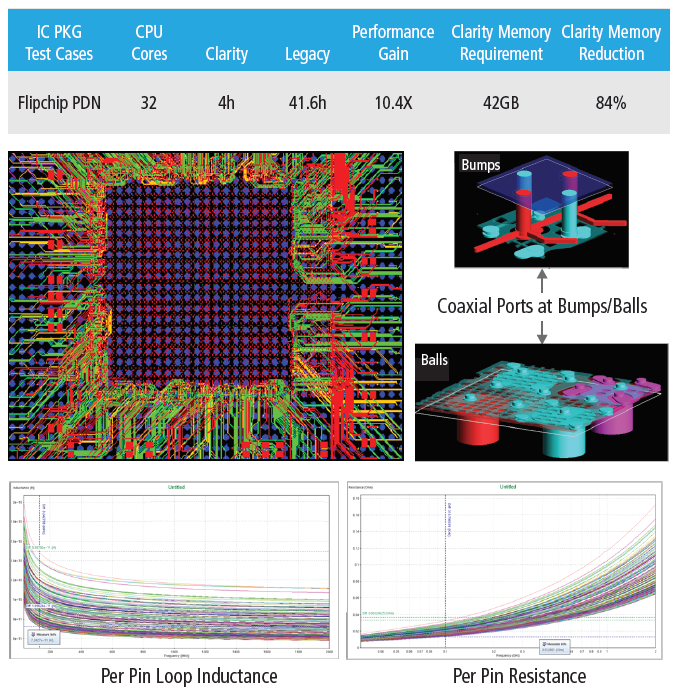

在過去,大(dà)型結構往往被人(rén)工切割成較小的(de)結構,以利用(yòng)最大(dà)、最強的(de)計算(suàn)資源進行分(fēn)析。Clarity 3D Solver 使這(zhè)一麻煩不複存在。采用(yòng)了(le)全新設計,通(tōng)過並行化(huà)解決3D結構所需的(de)矩陣計算(suàn),從而充分(fēn)利用(yòng)您的(de)多(duō)核計算(suàn)資源。這(zhè)些任務可(kě)以在一台計算(suàn)機的(de)内核或多(duō)台計算(suàn)機上並行處理(lǐ),将解決複雜(zá)結構的(de)時(shí)間縮短了(le) 10 倍甚至更多(duō)。

業内領先的(de)並行化(huà)技術可(kě)确保網格劃分(fēn)和(hé)頻(pín)率掃描在盡可(kě)能多(duō)的(de)計算(suàn)機、計算(suàn)機配置和(hé)内核上進行分(fēn)區(qū)和(hé)並行化(huà)。解決問題的(de)速度随著(zhe)計算(suàn)機内核數量的(de)增加而線性提升。如果用(yòng)戶可(kě)以将計算(suàn)機内核數量增加一倍,那麽求解速度也(yě)将近乎翻倍。

Clarity 3D Solver 僅用(yòng)半天即可(kě)對(duì)整個(gè)封裝 PDN 進行建模,而傳統的(de) 3D 求解器則需耗時(shí)幾天

利用(yòng)雲端的(de)基礎架構降低 3D 求解的(de)成本

使用(yòng)基于網絡的(de)雲端服務器來(lái)求解 3D 結構,可(kě)作爲購(gòu)買服務器硬件的(de)替代方案。無需使用(yòng)成本昂貴的(de)大(dà)型服務器,設計人(rén)員(yuán)可(kě)使用(yòng) Clarity 3D Solver 選擇成本較低的(de)雲端計算(suàn)資源,同時(shí)仍然保持最高(gāo)的(de)設計性能。解決 3D 結構時(shí),這(zhè)種靈活性可(kě)以大(dà)大(dà)節省雲端計算(suàn)時(shí)的(de)成本。

完整的(de)設計和(hé)分(fēn)析流程

Clarity 3D Solver 是高(gāo)端電子産品設計團隊所需的(de)智能系統設計 (Intelligent System Design™) 方案中的(de)關鍵要素。藉助 Cadence 完整的(de)設計和(hé)分(fēn)析流程,您将能夠創建可(kě)靠且具有競争力的(de)産品、在預算(suàn)内按時(shí)交付、增加市占率。

Clarity 3D Solver 特點

|

提供 10 倍快(kuài)電磁仿真速度,具備無限處理(lǐ)容量和(hé)黃(huáng)金标準精度 |

|---|---|

|

全新突破性架構可(kě)運行于數百個(gè) CPU,提供接近線性的(de)可(kě)擴展性,并兼用(yòng)于雲端與就地部署分(fēn)布式計算(suàn),大(dà)幅提高(gāo)速度并減少内存 |

|

使用(yòng) Sigrity™ 3D Workbench 的(de)參數化(huà)和(hé)用(yòng)戶定義的(de)方程表達式進行 what-if 分(fēn)析,從而改善産品設計,輕松編輯、修改和(hé)優化(huà)機械結構 |

|

爲芯片、封裝和(hé) PCB 提供集成模型萃取功能 |

|

通(tōng)過快(kuài)速準确的(de)互連提取以提高(gāo)産品可(kě)靠性 |

|

準确預測實驗室産品性能,避免在設計後期的(de)叠代返工 |

爲 EM 界面建模

将機械結構 (例如線纜和(hé)連接器) 與其系統設計相結合,并以單一模型方式對(duì) EM 接口進行建模。

3D 集成解決方案

輕松集成 Cadence 的(de) Allegro® Package Designer Plus、SiP Layout Option、Virtuoso® 和(hé) Allegro 平台,在分(fēn)析工具中進行優化(huà)後,無需重新繪制即可(kě)在設計工具中使用(yòng)。

爲包括有折叠和(hé)彎折在内的(de)剛柔闆設計建模

Sigrity 3D Workbench

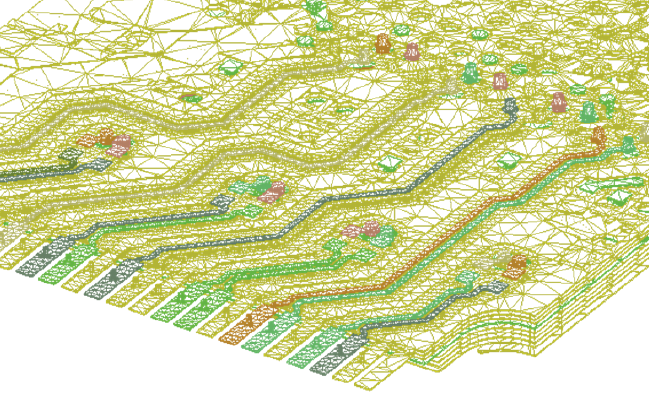

包含 3D 機械 CAD 的(de) GUI 使用(yòng)接口,用(yòng)于創建、編輯和(hé)導入 3D 實體模型以進行電氣分(fēn)析。您可(kě)以從 ACIS、IGES 和(hé) STEP 等常用(yòng) MCAD 格式以及 Cadence Allegro 和(hé) Sigrity 格式中獲取設計數據。通(tōng)過參數化(huà)和(hé)程序化(huà)的(de)表達式可(kě)以輕松創建 3D 組件,以實現建模靈活性和(hé)仿真優化(huà)。使用(yòng) 3D Workbench 的(de)模型清理(lǐ)功能可(kě)快(kuài)速修複 3D CAD 幾何問題和(hé)未對(duì)準錯誤。藉助先進的(de)自适應網格劃分(fēn)算(suàn)法,您可(kě)以自動爲小型複雜(zá) 3D 組件到帶有外殼的(de)大(dà)型複雜(zá)電子系統生成精确的(de)網格。

快(kuài)速有效地進行自我調整網格劃分(fēn),确保在較大(dà)頻(pín)率範圍内進行精确建模。

可(kě)用(yòng)性增強

爲待解決結構自動匹配可(kě)用(yòng)的(de)計算(suàn)資源,3D 專家和(hé)非 3D 專家均可(kě)及時(shí)獲得(de)準确的(de)結果。

突破性並行化(huà)運算(suàn)架構

在爲 3D 仿真所需的(de)計算(suàn)機配置編制預算(suàn)時(shí),将擁有更大(dà)的(de)靈活性。

靈活性

任何工程師均可(kě)使用(yòng)桌面、本地或雲端 HPC 資源進行真正的(de)整體的(de) 3D 分(fēn)析。

資源利用(yòng)最大(dà)化(huà)

在隻有少量内核可(kě)用(yòng)的(de)情況下(xià),可(kě)避免因計算(suàn)機資源被耗盡而提前終止運算(suàn)。

适用(yòng)于所有設計平台的(de)用(yòng)戶

從所有标準的(de)芯片、IC 封裝和(hé) PCB 平台輕松讀取設計數據。

操作系統和(hé)接口數據庫

|

适用(yòng)于 Microsoft Windows 和(hé) Linux |

|---|---|

|

擁有 Cadence、Mentor Graphics、Altium、Zuken 和(hé) AutoCAD 的(de) PCB 和(hé) IC 封裝布局數據庫之接口 |