許多(duō)電子產品的(de)創意都是從草(cǎo)圖開始,然後在 Visio 或 PowerPoint 中繪製圖表,最後再進入特定的(de) EDA 工具中進行設計。但是,這種方法使得(de)純圖形工具繪製的(de)圖與 EDA 工具的(de)設計之間存在很大(dà)的(de)脫節,由於沒有發生資料連結,所以在規範進行了(le)更改後無法實現一緻性和(hé)自動化(huà)。需求是前進的(de)動力,Cadence® Allegro® System Capture 工具可(kě)將對 PCB 系統級設計的(de)需求轉化(huà)為現實功能,不妨請 Cadence 的(de) Gary Hinde 來為大(dà)家稍作介紹。

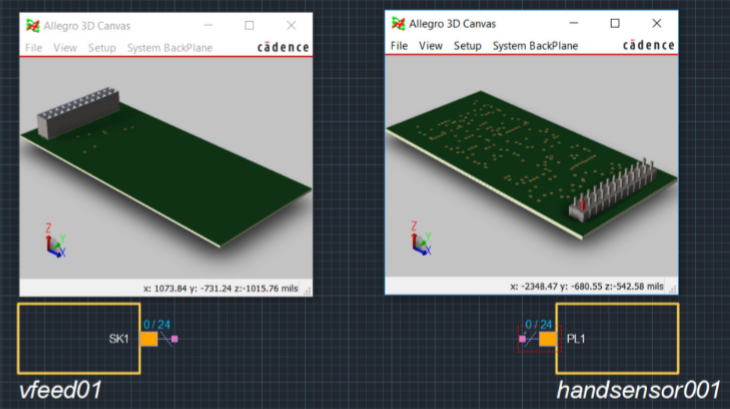

圖 1:在設計週期早期查看裸闆上的(de)連接器,確保連接器的(de)相容性和(hé)設計的(de)正確方向

Q:System Capture 軟體是何時開發的(de)?

System Capture 開發已有幾年,它是一個具有多(duō)個電路闆、封裝、電纜以及纜束系統的(de)硬體設計平臺。

Q:開發 System Capture 的(de)最初原因是什(shén)麼?

我曾在 Cadence 擔任應用(yòng)工程師及應用(yòng)工程師主管,拜訪過歐洲各地為汽車、工業、軍事 / 航空航太、網路甚至方程式賽車設計 PCB 系統的(de)客戶。這些客戶團隊在設計之初經常使用(yòng) PowerPoint 或 Visio 以捕捉全域,但是從來沒有與電氣系統及要求有任何聯繫。因此,我們開發了(le) System Capture 軟體,說明(míng)客戶自動化(huà)包含連接的(de)圖形圖表,並將系統劃分(fēn)為多(duō)個電路闆。

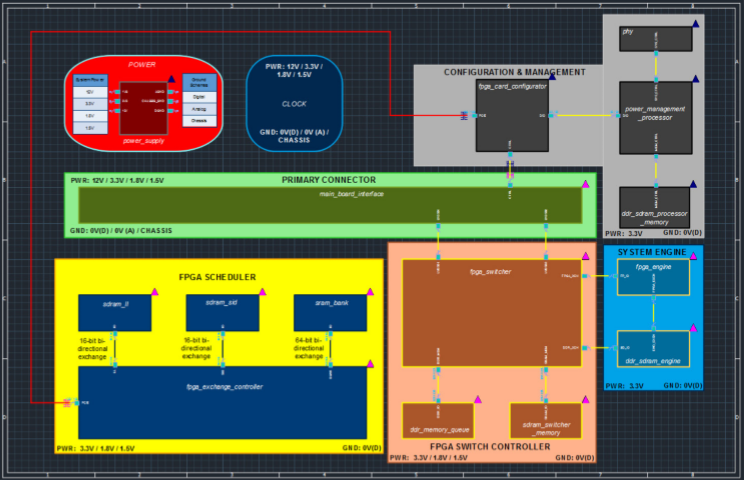

圖 2:電子系統定義推動設計詳細實現

Q:System Capture 是否適用(yòng)于任一電路圖或 PCB 佈局工具?

我們的(de) System Capture 工具目前僅支持 Cadence Allegro 和(hé) OrCAD 工具。

Q:能否舉例說明(míng) System Capture 的(de)優勢?

假設我們有一個帶有射頻和(hé)數位的(de)雙闆系統。藉助 System Capture,我們可(kě)以將系統劃分(fēn)為兩塊闆,然後給每塊闆分(fēn)配不同的(de)設計工程師以開展並行工作;此時由於兩個闆之間的(de)互連已率先輸入了(le) System Capture,因此即使在並行工作的(de)情況下(xià)也(yě)可(kě)保持電路闆之間的(de)互連一緻性。

Q:哪些工程師會使用(yòng)這個工具?

這要取決於設計專案,典型的(de)用(yòng)戶有:系統架構師、硬體架構師、首席工程師、高(gāo)級工程師、電子工程師、MCAD 使用(yòng)者、PCB 設計師、信號完整性專家,甚至是製造工程師。

Q:這種新方法有助於緩解哪些問題?

它可(kě)以消除將兩個或多(duō)個電路闆放在一起時產生的(de)分(fēn)歧或脫節現象:比如當管腳位置或管腳名稱發生變化(huà)時,該方法可(kě)以及時地捕捉到這些變化(huà),並應用(yòng)到統一的(de)設計中去。系統級連接是自上而下(xià)的(de),而且在為每個電路闆創建 PCB 佈局時,都會進行一緻性檢查。

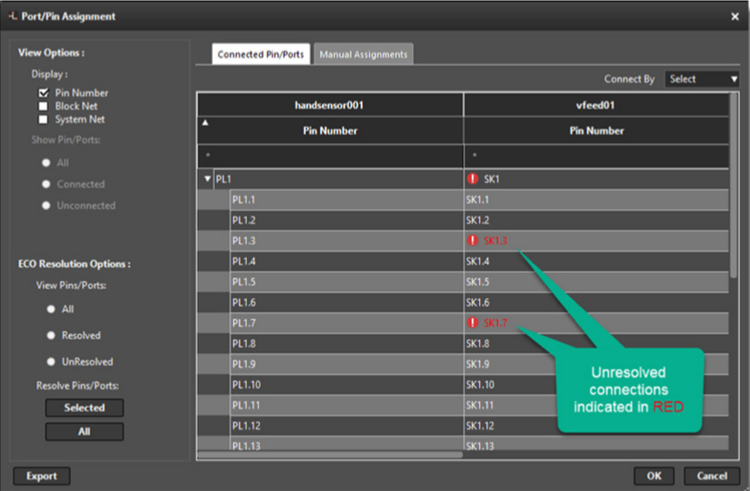

圖 3:識別並突出顯示系統連接不匹配的(de)情況,方便使用(yòng)者進行解決

Q:採用(yòng)這種方法,工程師可(kě)以節約多(duō)少時間?

透過 System Capture 中已經定義的(de)連接,我們可(kě)以將電路圖繪製期間的(de)設計速度提高(gāo) 2 倍至 5 倍。目前,電路圖頁面上放置去耦電容軌的(de)速度可(kě)提高(gāo) 10 倍。

Q:System Capture 可(kě)以支援什(shén)麼類型的(de)模擬分(fēn)析?

可(kě)使用(yòng) Sigrity™ 信號完整性工具進行信號完整性分(fēn)析,Sigrity 電源完整性進行電源完整性分(fēn)析。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」