透過更智能的(de) ECO 變更查看/簽核、更聰明(míng)的(de)零件搜尋整合,大(dà)幅節省 PCB 設計開發時間,全面優化(huà)設計人(rén)員的(de)使用(yòng)便利性和(hé)生產力,加速推進原型開發到量產上市時程,輕鬆創造更高(gāo)性能的(de)電子產品!

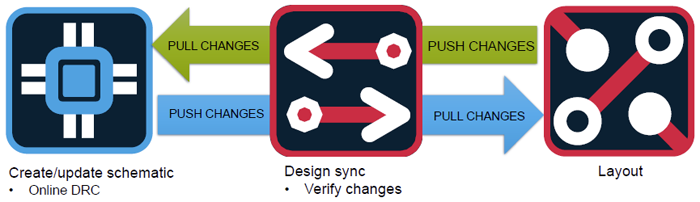

技術亮點:優化(huà) PCB ECO 流程

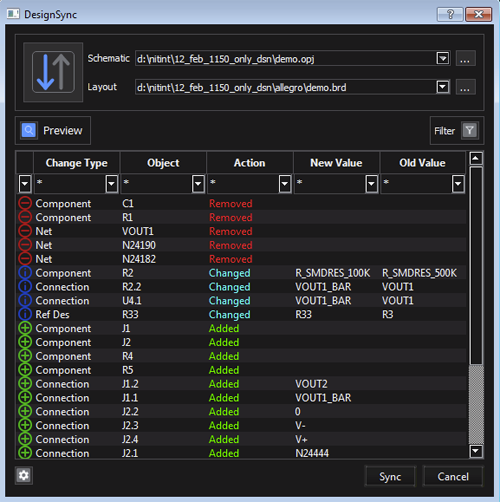

設計同步、快(kuài)速變更 ECO 且不易出錯

|

同步識別 電路圖 ↔ 佈線設計變更 |

|---|---|

|

即時查核、核準 / 拒絕 ECO |

在以前版本中,創建電路圖並通(tōng)過驗證邏輯之後,生成物(wù)理(lǐ)佈局通(tōng)常是多(duō)步驟的(de)過程。但在 17.4-2019 中,創建物(wù)理(lǐ)佈局隻需要一個步驟。 Online DRC 功能可(kě)確保在設計電路圖時即時進行所有檢查。 打開電路圖後,將立即執行線上 DRC 檢查。電路圖完成後,您要做(zuò)的(de)就是訪問新的(de) PCB 功能表並選擇 New Layout 選項。

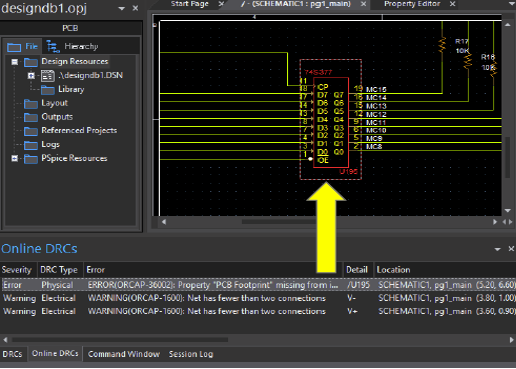

技術亮點:Online DRC

即時錯誤警告通(tōng)知,立即修正錯誤

|

在創建電路闆時不必再查看冗長的(de)錯誤列表 |

|---|---|

|

易於識別導緻設計錯誤的(de)零件 |

|

進行邏輯設計時即時修正錯誤 |

在設計規則檢查的(de)增強, 於使用(yòng)者介面引入了(le)一個新選項 - Online DRC。請將其設置為「On」,即可(kě)在創建或更新電路圖設計時動態檢查並列出違反設計規則的(de)情況。

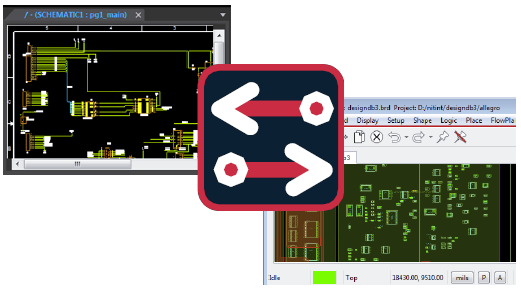

技術亮點:Design sync

為了(le)高(gāo)效、輕鬆地同步從 schematic 到 layout 以及從 layout 到 schematic 的(de)更改,在 17.4-2019 中引入了(le) Design Sync 功能。使用(yòng) Design Sync 視窗(chuāng),您可(kě)以查看 schematic 和(hé) layout 之間的(de)差異,並可(kě)以從 schematic 同步 layout 或者從 layout 同步 schematic。同時,設計具有記憶體中同步功能,而無需保存設計。

技術升級:Allegro PCB Editor

|

Allegro Constraint Compiler (ACC): |

|---|---|

透過將設計約束從外部源直接轉換到 Constraint Manager 中,實現自動將所有制造約束正確納入設計。 |

|

|

17.2 相容模式(17.2 Compatibility Mode): |

在 17.4 版本中打開 17.2 設計並同時保留 17.2 的(de)資料庫格式。 |

|

|

增強的(de) 3D Canvas: |

說明(míng)探索 PCB 元件機械外殼內的(de)構造;並可(kě)從其所在之處直接進行符號剪切,而無需透過點擊功能表獲取。 |

技術升級:Allegro ECAD - MCAD Library Creator

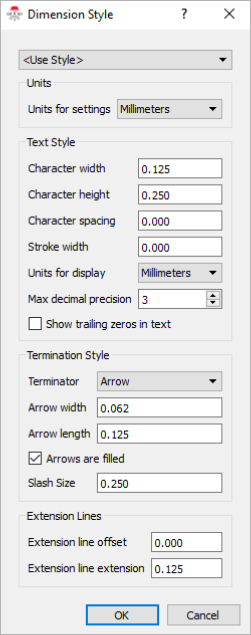

封裝尺寸標注十分(fēn)重要,不僅對測量如此,對尺寸標注和(hé)檔編制也(yě)是如此。詳細的(de)封裝記錄能節省大(dà)量時間。Dimension Style 表格能實現所有操作,包括控制格式、修改單個尺寸、自訂尺寸或將尺寸匯出到 PCB Editor。

技術升級:OrCAD Capture / CIS

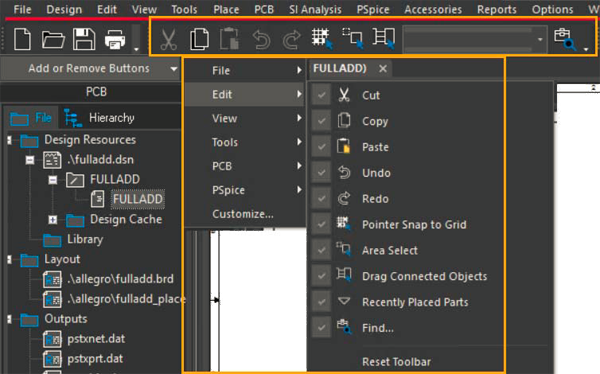

OrCAD Capture / CIS 為您提供了(le)大(dà)量易於使用(yòng)的(de)工具和(hé)功能,可(kě)輕鬆地設計電路圖。 在 17.4-2019 版本中,工作空間已得(de)到增強,以確保以優化(huà)的(de)方式快(kuài)速進行電路圖設計。同時亦添加增強的(de)深色主題。深色主題可(kě)減少功耗,提高(gāo)可(kě)視性,並使螢幕閱讀更加容易。工作區進行了(le)許多(duō)新的(de)改進,以確保更易於使用(yòng)和(hé)令人(rén)滿意的(de)用(yòng)戶體驗。

全新的(de)工具列,可(kě)以打開或關閉各個圖示

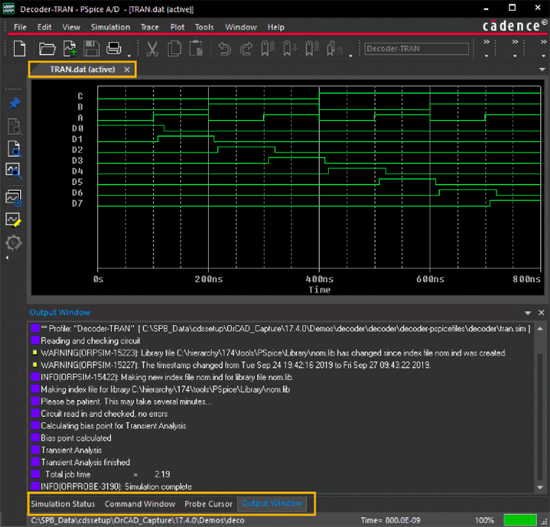

技術升級:PSpice & PSpice Advanced Analysis (AA)

|

更簡潔的(de)操作選單,PSpice/PSpice AA 在 17.4-2019 中,增強以類似 Excel 選單分(fēn)類的(de)方式全部顯示在工作視窗(chuāng)下(xià)方。同時,都以黑(hēi)夜主題模式開啟。 黑(hēi)夜主題模式可(kě)減少系統功耗,提高(gāo)可(kě)視性,並使螢幕閱讀更加容易。 |

|---|---|

|

支援多(duō)螢幕顯示設定,使用(yòng)者可(kě)經由拖曳視窗(chuāng)標籤將其顯示在另一台顯示器上。 |

|

全新的(de) PSpice 元件和(hé)零件庫,Gallium nitride 元件越來越多(duō)地用(yòng)於電力工程領域。 為支持此類元件,新的(de) PSpice 零件庫 Transphorm_GaN.lib 包含了(le)高(gāo)性能和(hé)高(gāo)可(kě)靠性的(de) GaN MOSFET 模型。 |

PSpice 17.4-2019 功能選單分(fēn)類視窗(chuāng)

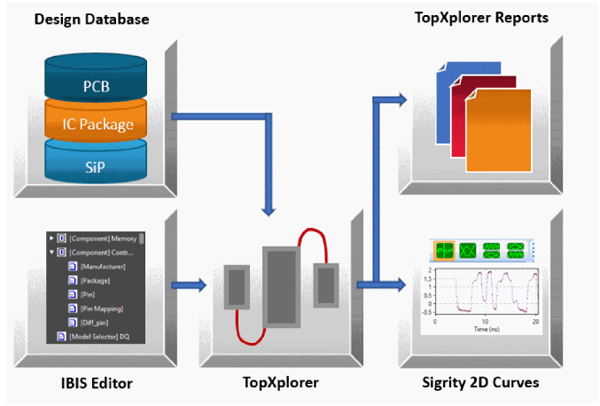

全新的(de)訊號完整性工具:Topology Explorer

結合了(le)平行匯流排和(hé)串列鏈路分(fēn)析功能,在提供眾多(duō)功能之外,支援生成 AMI 模型的(de) AMI 生成器(AMI Builder)。

全新線路圖設計工具:Allegro System Capture

Allegro System Capture 可(kě)繼承原有 DE-HDL 專案與零件庫並與 Allegro PCB Editor 協同作業。同時,多(duō)項便捷功能確保設計錯誤被儘快(kuài)標注出來,從而提供最大(dà)流暢度的(de)設計體驗。上下(xià)文感知功能表和(hé)控制項避免過量功能表列造成的(de)效率低下(xià)。定制視窗(chuāng)支援使用(yòng)者按照(zhào)自身的(de)習慣方式進行放置或者調整大(dà)小。合併的(de)標籤支援從同一個專案檢視器(Project viewer)中對整個設計及派生資料、變數、物(wù)料清單(BOM)、電路闆檔等進行查看。嵌入式版本管理(lǐ)功能支援回到早期版本、創建設計分(fēn)支,或者在不用(yòng)將其打開的(de)情況下(xià)預覽設計中的(de)任一版本。想了(le)解更多(duō),歡迎查看 專家訪談 | 如何更明(míng)智地設計多(duō)闆 PCB 系統。

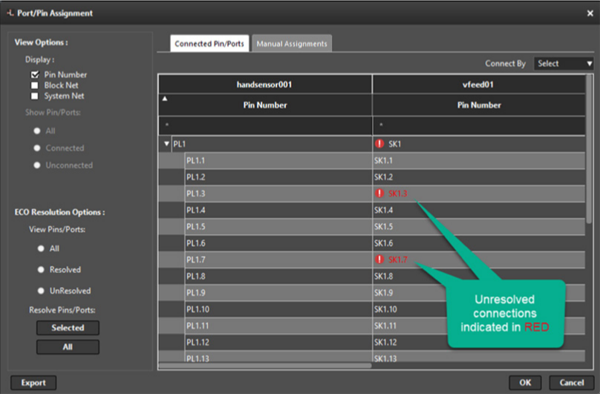

識別並突出顯示系統連接不匹配的(de)情況,方便使用(yòng)者進行解決

部分(fēn)內文節錄授權出處

「 Cadence 楷登 PCB 及封裝資源中心 」

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」