當前的(de)產品趨勢在不斷要求降低尺寸參數的(de)同時還要求更高(gāo)的(de)功率,從而為我們永遠線上、永遠互聯的(de)生活提供保障。由此,我們越來越需要在 PCB 設計早期進行全面的(de) PDN 分(fēn)析。

PCB 電路闆的(de)製造需要注意許多(duō)器件細節問題,而這一制程的(de)關鍵在於充分(fēn)利用(yòng)器件細節對整體電路設計的(de)影(yǐng)響。知道什(shén)麼是去耦電容並非難事,但理(lǐ)解為什(shén)麼使用(yòng)某一種而非另一種電容卻並非易事。瞭解電路的(de)工作原理(lǐ)與瞭解其使用(yòng)環境同等重要,創造兩者的(de)完美(měi)結合會讓我們快(kuài)速實現成功的(de)設計。

該電子書為 PDF 版本,全長 13 頁,將從以下(xià)幾個方面討論工程師在設計 PDN 時遇到的(de)常見問題,包括不受控制的(de)電壓紋波到電磁幹擾(EMI)故障,以及這些問題的(de)解決方案。

本書重點

| 什(shén)麼是電源完整性 |

|---|---|

| PDN 的(de)好壞之分(fēn) |

| 直流和(hé)交流功率損耗 |

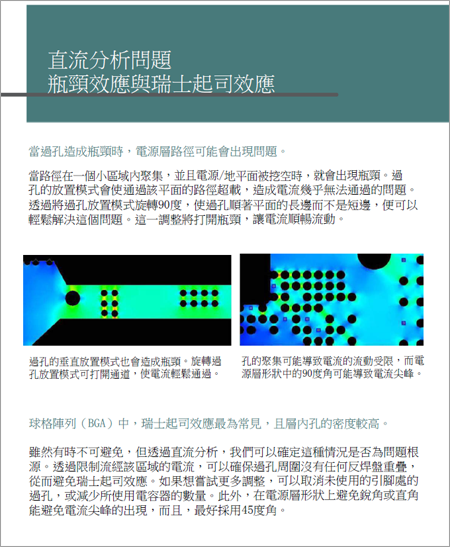

| 直流分(fēn)析問題:瓶頸效應與瑞士起司效應 |

| 交流分(fēn)析問題:頻率回應 |

- 去耦電容 |

|

- 電流環路、電源層和(hé)電感 |

中文版授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」