以下(xià)轉載文章(zhāng)授權來源於國際電子商情 ,作者王瓊芳

「三明(míng)治」兩端的(de)產業勢力開始往中間的(de)封測市場滲透,已是公認的(de)大(dà)勢所趨。SiP 技術為後摩爾時代提供了(le)一個完美(měi)的(de)紅利!不僅台積電這樣的(de)晶圓代工大(dà)廠清楚這一點,封測、EMS 和(hé)大(dà)多(duō)數半導體晶片客戶都體會到了(le) SiP 乃重中之重。

「摩爾定律」正逐步走向極限,SiP (系統級封裝,System in Package) 技術正推動摩爾定律繼續向前邁進。據 ASE 和(hé)西部證券研發中心預測,到 2020 年 SiP 的(de)市場空間將達到 166.9 億美(měi)元,營收增速提升到 50% 左右! 儘管受疫情影(yǐng)響,5G 手機仍將是這 50% 增速的(de)重要貢獻者。

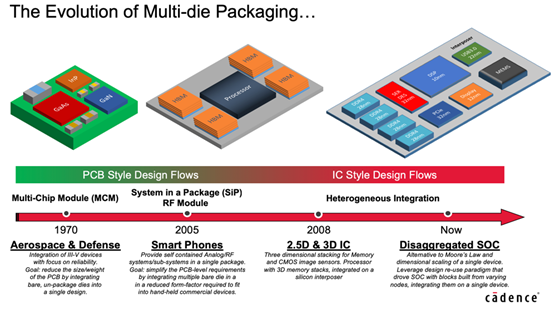

圖片來源:Cadence

新冠疫情影(yǐng)響甚小

2020 年春節期間爆發的(de)武漢新冠疫情,打亂了(le)電子產業鏈穩步發展的(de)節奏。復工時間延遲、醫療防護物(wù)資緊缺、物(wù)流運輸等問題,給上遊晶圓及封測產能帶來不小的(de)衝擊。

江蘇長電科技股份有限公司 (簡稱「長電」) 技術市場部總監劉明(míng)亮表示,從去年中到今年 3 月(yuè)初,長電的(de)訂單一直飽滿,春節期間也(yě)未停工,江陰廠更是滿負荷生產。在疫情出現之後,長電採取了(le)緊急防疫措施。公司過半數員工來自於江蘇及周邊地區。從 2 月(yuè) 10 日起,長電在大(dà)陸的(de)廠區已全面復工! 截至 3 月(yuè)初,公司產能已超過 90%,同比疫情前已無太大(dà)差別。

江蘇長電科技股份有限公司技術市場部總監劉明(míng)亮

疫情對長電復工的(de)影(yǐng)響甚小,這也(yě)是長電能在疫情期間應對緊急訂單的(de)一大(dà)優勢。據《國際電子商情》瞭解,大(dà)陸其它封測廠商如天水(shuǐ)華天、通(tōng)富微電等,因 60% 的(de)員工皆外地人(rén),其員工到崗率較低,對其產能的(de)影(yǐng)響較大(dà),不過自 2 月(yuè)中旬起也(yě)已逐漸復工。

「在特殊時期,供應鏈的(de)復工情況對原材料供應有所影(yǐng)響。我們的(de)目標是,在保障員工安全的(de)前提下(xià)最大(dà)限度的(de)保證產品的(de)良率、生產效率及產能供應。節前,長電已經備有材料庫存,疫情發生後,長電積極與供應商溝通(tōng),採購到了(le)一些他(tā)們的(de)存貨,因此受原材料影(yǐng)響不大(dà)。比如 01005 和(hé) 008004 型號的(de)被動元件,都是在系統級晶片封裝過程中必不可(kě)少的(de)元器件,長電現持的(de)這方面原材料,可(kě)以滿足客戶的(de)量產使用(yòng)需求。」 劉明(míng)亮說。

疫情帶來壓力的(de)同時也(yě)帶給企業動力。上海芯波電子科技有限公司 (芯和(hé)半導體子公司)研發總監胡孝偉坦言,新冠疫情對公司的(de)復工造成了(le)一定程度的(de)影(yǐng)響,但截至 3 月(yuè) 6 日,公司復工率已達 95% 左右。他(tā)預計 2020 年 5G 手機相關的(de)產品研發和(hé)生產均將承受不小的(de)壓力,但對芯波而言卻是個很好的(de)調整產業結構、優化(huà)內外流程的(de)時機。

5G 用(yòng)量是 4G 的(de)兩倍

5G 手機相比 4G 手機需要更多(duō)的(de) SiP 晶片。據《國際電子商情》瞭解,4G 標準手機 (不帶 LTE ) 射頻前端用(yòng)芯量約 15-20 顆; LTE 手機 (增加了(le) 2.7GHz 頻段) 用(yòng)芯量約 25-30 顆; 5G 手機也(yě)分(fēn)兩個頻段:(1) Sub-6GHz 頻段用(yòng)芯量是 40 顆左右; (2)毫米波頻段(相容 Sub-6GHz),平均射頻前端用(yòng)芯量高(gāo)達 55-60 顆。

由上推算(suàn),Sub-6GHz 頻段的(de) 5G 用(yòng)芯量相比 4G 增長了(le) 60% 左右,若將毫米波頻段和(hé) Sub-6GHz 頻段都囊括在內,則是兩倍的(de)用(yòng)芯量,這其中 80% 的(de)晶片都會採用(yòng) SiP 封裝。

「長電已準備好迎接 5G 的(de)市場需求,」據劉明(míng)亮介紹,目前長電大(dà)部分(fēn)先進 SiP 封裝的(de)技術成果及成熟產能集中在韓國仁川廠和(hé)國內江陰廠,其他(tā)廠區的(de) SiP 封裝技術與產能也(yě)在大(dà)跨步成長中。

芯波科技 SiP 產品主要集中在射頻前端、Wi-Fi 和(hé)藍牙產品。胡孝偉說:「5G 不僅需要支援新的(de)頻段,還要相容 2G、3G、4G頻段,這使得(de)射頻前端中功率放大(dà)器(PA)、開關(Switch)、低雜訊放大(dà)器(LNA)、濾波器 (SAW/BAW) 等數量大(dà)幅度增加,進而緻使其不得(de)不透過 SiP 封裝來解決因頻段增加帶來的(de)射頻前端 PCB 面積增大(dà)的(de)問題。由於不同功能的(de)射頻器件採用(yòng)不同的(de)工藝制程,相比 SoC,SiP 幾乎是實現射頻前端高(gāo)度整合的(de)唯一方式。」

當傳統的(de)摩爾定律迫近極限,需要廠商在更短的(de)開發時程中,用(yòng)更經濟的(de)方法來節約成本,做(zuò)出更佳的(de)產品,比如電源管理(lǐ)擁有更好的(de)電源效率並增加處理(lǐ)效能,將是工程師們的(de)終極挑戰。

Cadence 產品市場總監 Julian Sun

Cadence 產品市場總監 Julian Sun 表示,Cadence 現在正在協助業界諸多(duō)公司克服摩爾定律,走進後摩爾時代「More than Moore」,利用(yòng)異質整合的(de)能力 (Heterogeneous integration) 將不同的(de)元素整合到 SiP 以開發新的(de)電子產品。SiP 可(kě)以説明(míng)客戶進行新的(de)模組化(huà)設計,並解決從闆級到封裝到 IC 的(de)跨域設計問題,比如採用(yòng) Chiplet 的(de)設計理(lǐ)念。

來自 5G 多(duō)頻高(gāo)頻的(de)挑戰

針對 5G 智慧手機,目前 SiP 封裝技術遇到不小的(de)挑戰,比如整合毫米波技術、相容整合 2G / 3G / 4G 多(duō)個射頻前端等,該如何應對?

日月(yuè)光(guāng)表示,對於毫米波相容整合 2G / 3G / 4G 射頻前端,新的(de)前端模組增加如 sub-6GHz 與毫米波天線模組,因此更緊密的(de)整合與厚度的(de)薄化(huà)是趨勢與技術挑戰。在應對策略上,新的(de) Conformal shielding / Compartment shielding 解決方案、Fan-out SiP、double-side molding 與毫米波 AiP / AiM 量產測試解決方案等都是很好的(de)選擇。

劉明(míng)亮表示,從長電的(de)角度來看,5G SiP 封裝主要面臨三大(dà)技術挑戰:一是整合毫米波技術。因毫米波是超高(gāo)頻段,天線數量有所增加且尺寸要求較小,加上 5G 收發模式跟 4G 不同,在大(dà)多(duō)數應用(yòng)場景下(xià)天線需要被融入到封裝中去,即採用(yòng)封裝級天線 (Antenna-in-Package,AiP) 技術。AiP 天線的(de)匹配、微調是很大(dà)的(de)挑戰。

二是材料。過去封測廠做(zuò) 3G 或 4G 射頻產品的(de) SiP 封裝,不需要考慮太多(duō)材料方面的(de)設計問題,隻要整體產品的(de)應力、可(kě)靠性等達標就行。而到了(le) 5G Sub-6GHz 頻段,就要求所有的(de)材料如基闆、塑封原材料、晶片與基闆的(de)連接 / 耦合材料等,都必須具備低損耗特性,如 Dk 介電常數必須小於 3.2,Df 損耗因數必須小於 0.05 等,而且這還隻是在 5G Sub-6GHz 頻段 (尚未達到毫米波頻段) 的(de)硬性標準。未來毫米波 SiP 達標任務之艱巨,可(kě)窺一斑!

三是 5G 比起 4G 需要處理(lǐ)的(de)頻段複雜程度和(hé)即時可(kě)程式設計性高(gāo)很多(duō),而且客戶對於手機的(de)空間設計要求也(yě)越來越高(gāo)。將因5G所新增六成左右的(de)晶片擠進不可(kě)擴容的(de)手機空間這一要求,要求封裝廠商能夠提出更多(duō)、更好的(de)技術創新,比如在基闆的(de)兩面放置晶片或被動元件 (原來隻放一面) 以達到縮減封裝面積的(de)目的(de)。但這樣做(zuò)又不可(kě)避免地增加了(le)封裝的(de)整體厚度,所以封裝工程師們還必須採用(yòng)其它的(de)方法把整體厚度變薄,可(kě)謂使盡了(le)渾身解數! 這種雙面超薄設計難度較大(dà),長電針對此 SiP 創新專案做(zuò)了(le)大(dà)量技術開發和(hé)反復驗證的(de)工作,目前已達到世界領先水(shuǐ)準。

事實上,上述挑戰對於日月(yuè)光(guāng)、長電、安靠以及天水(shuǐ)華天、通(tōng)富微電等都是共同的(de)難題。相對而言,在 5GSub-6GHz 頻段,日月(yuè)光(guāng)、長電和(hé)安靠 SiP 晶片良率較高(gāo),AiP 的(de)厚度做(zuò)到了(le)較薄,而通(tōng)富微電和(hé)天水(shuǐ)華天仍需進一步努力突破技術難點。

上海芯波電子科技有限公司研發總監胡孝偉

在芯波科技胡孝偉看來,5G 通(tōng)信對 SiP 封裝的(de)挑戰有三個方面:首先,設計端如何處理(lǐ)多(duō)頻段射頻前端的(de)電磁相容,以及如何處理(lǐ)多(duō)器件小尺寸高(gāo)熱密度散熱問題;其次,製造端如何使用(yòng)低成本常規工藝完成超常規的(de)技術要求;最後,如何用(yòng)同一種封裝工藝封裝不同工藝的(de)器件。

他(tā)給出了(le)一些解決方案:「這需要在信號完整性、電源完整性、射頻指標模擬(例如插損、回損和(hé)諧振)、熱、應力等方面進行充分(fēn)的(de)模擬分(fēn)析。在設計端,充分(fēn)利用(yòng)自身的(de) SiP 和(hé) IPD 設計能力,結合 EDA 工具提升設計品質和(hé)準確度,在製造端充分(fēn)使用(yòng)組合現有工藝,探索新工藝、減少反覆運算(suàn)。」

Cadence Julian Sun 則建議客戶應考慮轉換原來 SoC 的(de)理(lǐ)念到 SiP 的(de)作法。透過採用(yòng) Chiplet 方法,利用(yòng) Cadence APD+ 來設計 SiP 説明(míng)客戶縮短開發週期、節省成本,並降低整個晶片開發的(de)風險,以實現與市場競爭的(de)差異化(huà)。

「客戶可(kě)以從各個 IP 供應商(就算(suàn)是不同的(de)工藝節點) 處獲取適當的(de) Chiplet 並加以組合。這是一個多(duō)方面協作的(de)問題。它將要求 3D / 2.5D IC 設計流程,具有矽中介層 Silicon Interposer 或嵌入式橋 Embedded Bridge 和(hé)可(kě)佈線基闆 RDL 以及 FOWLP(Fan out Wafer Level Package) 的(de)封裝設計。它需要考慮 PI/SI (電源完整性/信號完整性),3D EM 和(hé)熱感知電氣設計 (Thermal awareness electrical design)。」Julian Sun 說。

整合 eMMC,是否會成為世紀難題?

一般情況下(xià),SoC 隻整合 AP 類的(de)邏輯系統,而 SiP 則是整合 AP+mobileDDR。某種程度上說 SiP=SoC+DDR。隨著將來晶片整合度要求越來越高(gāo),eMMC 也(yě)很有可(kě)能會整合至 SiP 中。

Julian Sun 表示,SoC 的(de)缺點是開發時間長,其自身的(de)複雜性緻使成本推高(gāo),並且每一次功能的(de)修改,都需要再次流片。而對於 Chiplet 的(de)概念,SiP 不再隻是用(yòng)來設計 HBM,而且因為 TSV (Through Silicon Via) 和(hé) WLP (Wafer Level Package) 的(de)加入能夠在設計中添加更多(duō)組件。異質整合的(de)能力可(kě)以説明(míng)客戶以新的(de)封裝樣式,快(kuài)速開發產品並投入上市。

「SiP 設計面臨的(de)挑戰是系統的(de)連接複雜性,LV S(Layout vs. Schematic 版圖與電路圖互連檢查)、跨域協作(用(yòng)於數位digital、類比 Analog、混合信號 Mixed Signal、機械和(hé)熱感知設計 Thermal awareness electrical design 的(de)多(duō)種技術以及工程變更管理(lǐ)),如何説明(míng)客戶有效縮短設計週期、提高(gāo)設計品質與降低成本始終是 Cadence 的(de)首要任務。」Julian Sun 說。

據《國際電子商情》瞭解,5G 所需的(de) SiP 涉及高(gāo)頻射頻技術,天線調節和(hé)信號屏蔽都是難題,尤其是到了(le)一定頻段,各晶片、被動元件、基闆乃至注塑材料之間都會產生不同程度的(de)信號互擾,因此如何做(zuò)到一邊做(zuò) EMI 屏蔽一邊又把 eMMC 和(hé) AP、5G射頻無縫連接是一門關鍵技術。並且,目前大(dà)部分(fēn)存儲晶片都採用(yòng) 3D 堆疊技術,進一步增加了(le) EMI 屏蔽技術實現的(de)難度。

此外,目前 eMMC 已經堆疊到 64 層了(le),64 層晶片中間有很多(duō)超精細型銀線、金線穿來穿去,和(hé)各種 14 奈米、16 奈米甚至28 奈米的(de) SoC 無縫連接,難免會有很多(duō) I/O 方面的(de)問題。另外,這些金屬線之間也(yě)互有幹擾。需要考慮的(de)各種設計因素實在很多(duō)!

日月(yuè)光(guāng)也(yě)表示,挑戰主要來自封裝厚度進一步的(de)薄化(huà),在技術突破上,有機基闆 PoP 封裝 (HBPoP) 與扇出型 PoP 封裝(FOPoP) 都是可(kě)行的(de)解決方案。

「在 5G 時代的(de) SiP 設計,多(duō)種混合電源、極高(gāo)密度的(de)高(gāo)速高(gāo)頻走線設計的(de)成為常規要求,其最大(dà)挑戰是電源完整性和(hé)信號完整性的(de)設計,」芯波科技胡孝偉說,芯波在 SiP 設計領域中擁有豐富的(de)經驗,充分(fēn)準確的(de)模擬代替測試與試驗是解決技術難題的(de)必經之路。

「三明(míng)治」格局掣肘,如何突破?

目前,晶圓代工廠商台積電(TSMC) 研發出 CoWoS (Chip-on-Wafer-on-Substrate) 和(hé) InFO (Integrated Fan Out) 2.5D 晶圓級封裝技術,同時終端 EMS 廠商也(yě)開始向上遊封測「開展業務」,這對傳統封測廠商是否帶來一定的(de)競爭壓力?

劉明(míng)亮將目前封測產業的(de)大(dà)趨勢形像化(huà)地比喻成一個「三明(míng)治」。首先,這個三明(míng)治的(de)一邊,台積電 (TSMC) 等晶圓代工大(dà)廠,基於後摩爾時代的(de)壓力以及重點客戶的(de)要求,開始將他(tā)們自主研發的(de)晶圓級封裝工藝導入量產。其次,三明(míng)治的(de)另一邊,傳統的(de) EMS 巨頭如偉創力 (Flextronics) 等,出於拓展市場以及提高(gāo)企業競爭力的(de)考慮,試圖從基闆材料和(hé)技術入手,由組裝技術的(de)下(xià)端進入 SiP 封裝業務生態系統。而封測企業,如日月(yuè)光(guāng)、長電、安靠、天水(shuǐ)華天、通(tōng)富微電等,則處於這個三明(míng)治的(de)中央,不但要繼續與自己的(de)老對手們競爭,而且還必須應對來自三明(míng)治兩邊的(de)勢力夾擊。由此可(kě)見,未來幾年封測廠商將承壓不小。在此大(dà)趨勢當中,如何運籌博弈,化(huà)危機為契機,是出給每個封測廠商的(de)必答(dá)題。

劉明(míng)亮坦言,TSMC 量產化(huà) inFO、COWOS 封裝工藝,對封測廠商確有壓力,尤其是具備晶圓級 SiP 能力的(de)封測廠商。畢竟 TSMC 它是晶圓代工業公認的(de) NO.1,有深厚的(de)晶圓級技術積累。從市場角度來講,它們做(zuò) inFO 主要是為了(le)順應其重點客戶的(de)要求,專攻的(de)是晶圓級 3D 堆疊封裝技術。

據《國際電子商情》瞭解,該重點客戶已經多(duō)次要求 TSMC 將晶片間的(de)最小距離縮減到 80 微米。目前日月(yuè)光(guāng)、安靠、長電等已量產的(de)晶片中能實現的(de)最小距離,普遍為 150 微米,離 TSMC 仍有近 2 倍的(de)差距。目前長電的(de)研發部門也(yě)可(kě)做(zuò)到 80 微米 - 100 微米的(de)技術實現,但離可(kě)量產化(huà)的(de)良率水(shuǐ)準還有一定距離。

3D 堆疊封裝的(de)難度在於,對設備的(de)精密度要求很高(gāo),TSMC 有現成的(de)晶圓級設備,透過適當改裝和(hé) DOE 就可(kě)適用(yòng)於 3D 堆疊封裝,同時憑藉自身多(duō)年的(de)晶圓級晶片代工經驗,因此相比封測廠商做(zuò) 3D 晶片封裝,成功係數較高(gāo)。

「長電採取的(de)是雙管齊下(xià)的(de)策略,一方面按照(zhào) TSMC 的(de)晶圓級技術方向走,目前比起 TSMC 的(de) inFO,長電在精度上差了(le) 15% 左右,將會繼續迎頭趕上; 另一方面長電在商業模式上,跟 TSMC、SMIC 這些晶圓代工大(dà)廠長期保持緊密合作,互相扶持,取長補短,共同服務好國內外等重點 SiP 客戶。」劉明(míng)亮說。

據《國際電子商情》瞭解,「三明(míng)治」兩端的(de)產業勢力開始往中間的(de)封測市場滲透,已是公認的(de)大(dà)勢所趨。從 Foundry 的(de)角度來看,進入後摩爾時代以來,晶片制程微縮的(de)優勢已日趨進入極限,尤其到了(le) 5 奈米之後,幾乎不能再光(guāng)靠縮小電晶體的(de)尺寸來完成技術和(hé)成本上的(de)反覆運算(suàn)了(le)。SiP 技術恰恰為後摩爾時代提供了(le)一個完美(měi)的(de)紅利!其實,不光(guāng)是台積電這樣的(de)晶圓代工大(dà)廠很清楚這一點,封測、EMS 和(hé)大(dà)多(duō)數半導體晶片客戶都體會到了(le) SiP 乃重中之重。

從 EMS 的(de)角度來看,隨著低端代工製造業的(de)利潤日漸微薄,往上遊走不失為一條提升利潤空間的(de)出路。不少 EMS 大(dà)廠已經開始積極運作,其中包括在軟闆材料技術與 HDI 基闆設計方面有著雄厚實力的(de)偉創力,按照(zhào)當前的(de) BOM 表計價標準,基闆在半導體封裝中的(de)成本占比 30% 以上,相當高(gāo)。偉創力藉其基闆方面的(de)技術優勢殺進封測領域,算(suàn)是妙計。不過,與 TSMC 等晶圓大(dà)廠往下(xià)遊走時水(shuǐ)到渠成般的(de)「輕鬆」相比,偉創力等傳統 EMS 企業往上遊走的(de)過程中,必須經歷更難的(de)技術積累以及付出更多(duō)的(de)資本投入,可(kě)真的(de)不「輕鬆」! 在資本投入這方面,據悉偉創力正在物(wù)色封測行業中的(de)收購目標。

總之,作為當前超越摩爾定律的(de)幾乎唯一路徑,SiP 勢不可(kě)擋被封測廠商投入重金研發。從市場前景來看,2020 年,5G 手機、AR / VR、可(kě)穿戴、TWS 耳機等將帶給 SiP 巨大(dà)的(de)市場成長動力; 從技術層面來看,對 5G 多(duō)頻高(gāo)頻的(de)技術整合是各大(dà)封測廠努力突破的(de)方向; 從產業格局來看,隨著台積電和(hé)偉創力等上下(xià)遊企業加入戰局,封測廠商在雙面夾擊之下(xià)需要做(zuò)的(de)是練好內功,找準自身核心競爭優勢,保持在封測賽道上持續領先。

本文授權轉載出處

|

|---|