目前,Cadence 的(de)產品組合提供多(duō)種電磁 (EM) 技術。一些是收購而來,另一些則是內部創新。面對 Cadence 產品系列中的(de)諸多(duō) EM 模擬和(hé)分(fēn)析工具,您可(kě)能會問自己:我需要瞭解關於它們的(de)哪些知識,又該使用(yòng)其中的(de)哪些產品?

讓我們先來瞭解一下(xià) EM 求解器的(de)功能。首先,它會讀取導體中的(de)物(wù)理(lǐ)描述,這些描述通(tōng)常是電路佈線;但對於連接器等,則是機械模型。然後,EM 求解器會處理(lǐ)佈線結構,將其轉化(huà)為可(kě)用(yòng)於分(fēn)析階段的(de)形式。這一過程通(tōng)常涉及使用(yòng)有限元素分(fēn)析法 (FEM),或由於佈線限制 (例如平面) 而經過優化(huà)的(de)方法,對導體進行「網格劃分(fēn) (Meshing)」。 需要進行「網格劃分(fēn)」的(de)原因在於,要對導體的(de)細小部位運用(yòng)各種分(fēn)析方法,其中可(kě)能會進行很多(duō)粗略估算(suàn),但不會造成重大(dà)誤差,然後透過將所有這些細小部位的(de)分(fēn)析結果整合在一個整體的(de)解中,完成整體分(fēn)析。因此,對於每個元素,下(xià)一個階段是根據 Maxwell 電磁方程式進行分(fēn)析。然後將這些分(fēn)析結果整合,得(de)出最終解。分(fēn)析結果以模型 (例如 S 參數) 的(de)形式提供,可(kě)以用(yòng)於電路模擬,以驗證性能。

為何以及何時進行 EM 分(fēn)析

進行 EM 分(fēn)析的(de)主要原因有兩個 :第一個是瞭解設計中的(de)信號是否符合其性能規格,第二個是瞭解設計在電路/系統中是否存在意外的(de) EM 交互。

我們可(kě)能還需要在不同的(de)場合進行 EM 分(fēn)析。首先是,我們正在進行一些設計 (晶片、封裝、電路闆、系統),並且希望瞭解當前的(de)設計品質。我們希望根據分(fēn)析結果調整設計物(wù)件,進而進一步優化(huà)設計。在這種情況下(xià),我們需要實現高(gāo)性能和(hé)整合,想要從設計系統 (比如用(yòng)於晶片的(de) Virtuoso®、用(yòng)於電路闆的(de) Allegro®、或用(yòng)於連接器的(de)協力廠商模型) 中盡可(kě)能快(kuài)地獲取結果。同時,我們不希望手動傳輸檔、手動引導網格劃分(fēn)過程,也(yě)不希望手動將結果傳輸回設計環境。事實上,除了(le)按一下(xià)功能表項目以啟動分(fēn)析之外,我們根本不希望進行任何手動操作。另外,由於在分(fēn)析過程中需要持續等待,因此我們希望能縮短等待時間——最好幾秒鐘就可(kě)以完成。

進行 EM 分(fēn)析的(de)第二個原因是用(yòng)於簽核。此時我們已經完成了(le)設計,並想確定最終的(de)設計結果是否和(hé)預想的(de)一樣好。在這種情況下(xià),相比於性能,我們更關心準確度。我們希望僅進行一次或最多(duō)幾次分(fēn)析,因此隻要資料盡可(kě)能接近設計的(de)最終製造結果,我們並不介意整個過程可(kě)能耗時較慢(màn)。在實踐中,效率和(hé)精確性並不是一定要二選一,隨著設計的(de)進行,執行時間與準確度之間的(de)權衡會不斷變化(huà)。

在瞭解了(le)所有求解器共有的(de)基礎知識之後,讓我們來瞭解 Cadence 公司的(de) EM 技術,並進一步瞭解它們的(de)來源以及每種技術的(de)優勢。

Sigrity

Cadence 於 2012 年收購了(le) Sigrity (公司) 。該公司具有各種專業的(de)產品選項 (例如,Sigrity Serial Link Analysis),但是在本文中,我們將重點介紹完整的(de) EM 分(fēn)析。Sigrity™ PowerSI® 是一種平面 3D (或稱為混合) 求解器,即它主要採用(yòng)啟發法式 2D 演算(suàn)法,來得(de)出接近於使用(yòng)完整 3D 求解器所能獲得(de)的(de)結果,但求解速度要快(kuài)得(de)多(duō)。

Clarity

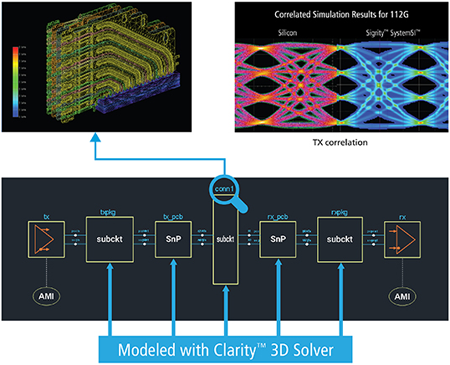

Clarity™ 3D Solver 由 Cadence 內部研發,於去年發佈,詳情請見《 視頻解密|Clarity 如何為系統分(fēn)析和(hé)設計提供前所未有的(de)性能及容量 》一文。

Clarity 是所有求解器中最通(tōng)用(yòng)的(de)求解器,可(kě)以處理(lǐ)任意 3D 結構。當需要進行完整的(de) 3D 分(fēn)析或沒有其他(tā)合適的(de)求解器時,Clarity 便是理(lǐ)想之選——例如,分(fēn)析電路闆和(hé)連接器,或者分(fēn)析完整的(de)球柵陣列 (BGA) 封裝。Clarity 也(yě)是擴展性最強的(de)求解器,從最初就設計為可(kě)以在大(dà)型伺服器場和(hé)雲資料中心運行,而無需在任何伺服器上使用(yòng)大(dà)量記憶體。因此,Clarity 進行的(de)是系統級分(fēn)析。如今,唯一超出其能力範圍的(de)分(fēn)析類型,是將整個雷達單元放在室內,然後分(fēn)析三米外的(de)信號。

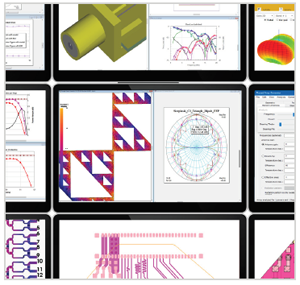

AWR AXIEM 和(hé) Analyst

Cadence 於今年初透過收購 AWR 收購了(le) AWR AXIEM® 軟體,詳情請參見《 利用(yòng) AWR 進行無線電和(hé)雷達設計 》一文。AXIEM 已針對 PCB 級別的(de)使用(yòng)進行了(le)優化(huà),還針對 AWR® Microwave Office 軟體中更通(tōng)用(yòng)的(de) RF 解決方案進行了(le)優化(huà)。收購之前,AXIEM 已整合到 Virtuoso RF (在原始程式碼級別) 軟體中。

AWR EM 技術包括 AXIEM (平面 3D) 和(hé) Analyst™(完整 3D)。這兩者都緊密整合到 Cadence AWR Design Environment® 中,該平臺的(de)應用(yòng)物(wù)件包括從 III-V 晶片到 RF 模組甚至是天線在內的(de)微波應用(yòng)。

AXIEM 針對平面結構級別的(de)使用(yòng) (例如 PCB、MMIC 等) 進行了(le)優化(huà)。 對於採用(yòng)多(duō)種技術的(de)更複雜的(de)設計 (例如微波 / RF 模組或包含非平面天線的(de)系統級設計),Analyst 是理(lǐ)想之選。

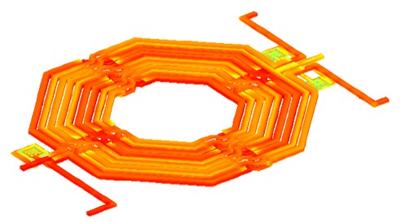

EMX

Cadence 於今年早些時候透過收購 Integrand Software 公司收購了(le) EMX® 軟體。EMX 經過優化(huà),可(kě)分(fēn)析矽晶片上的(de)無源元件。如同片上互連一樣,它主要針對平面導體和(hé)小過孔進行了(le)優化(huà)。EMX 還擁有一個廣泛的(de)來自所有主要晶圓代工廠 PDK 庫。這種組合意味著,它可(kě)以為晶圓代工廠流程中的(de)矽晶片上的(de)無源元件提供快(kuài)速而準確的(de)分(fēn)析結果。但僅限於這種特殊情況。幸運的(de)是,這是一種覆蓋範圍很大(dà)的(de)特殊情況,因為有越來越多(duō)的(de)無源元件被轉移到晶片上。

如何選擇 EM 求解器

如果因為元素的(de)平面程度不夠充足,或者您正在分(fēn)析一個大(dà)型系統,而需要一個完整的(de) 3D 求解器,那麼 Clarity 3D Solver 就是您的(de)理(lǐ)想之選。

在電路闆和(hé)封裝級別,Sigrity PowerSI 將為您提供快(kuài)速而精準的(de)結果;但如果您追求的(de)是黃金標準的(de)精準性,那麼 Clarity 3D Solver 才是您的(de)不二選擇。

對於在 AWR Microwave Office 中設計的(de) RF 結構,AWR AXIEM 軟體 (平面) 和(hé) AWR Analyst 軟體 (3D) 都是合適的(de)選擇,並且都已非常好地整合到了(le) AWR 平臺中。

如果您要進行片上分(fēn)析 (CMOS) ,則 EMX 就是您的(de)首選 EM 求解器。

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」