通(tōng)常,設計人(rén)員將連接器安裝在電路闆上,並將其整合到訊號完整性分(fēn)析中。因此,連接器也(yě)必須經過精心設計。一方面,它們是由塑膠和(hé)金屬導體組裝而來的(de)機械部件;另一方面,它們是需要分(fēn)析的(de)電磁結構。

為了(le)更好地瞭解連接器設計,我們請來 Cadence 硬體驗證部門的(de)高(gāo)級首席硬體工程師 Jason Chan 詳細講解連接器設計的(de)流程與要點。在加入 Cadence 之前,Jason 曾在 Amphenol 擔任連接器設計師,該公司是連接器產業的(de)領導者之一。

連接器設計

由於規格衝突,設計連接器是一項艱巨的(de)任務。對此,Jason 表示:

「 從表面上看,連接器並不複雜,其構造隻是塑膠成型和(hé)沖壓金屬。然而對於高(gāo)速連接器而言,連接器公司不僅需要以低成本進行設計,更要使其性能媲美(měi)昂貴的(de)微波連接器。 」

連接器的(de)設計必須考慮到訊號完整性問題。有些問題無法僅透過 SerDes 發射器和(hé)接收器中的(de)等化(huà)器來解決。尤其是,回波損耗導緻接收噪音(yīn)容限降低,因為部分(fēn)訊號並未抵達接收器,這些訊號在均衡期間顯然沒有用(yòng)處。 串擾 (即各路訊號之間的(de)相互幹擾) 是不能透過均衡來補償的(de),因為它的(de)發生頻率與訊號大(dà)緻相同 (假設加擾者也(yě)以相似的(de)資料速率運行),其速度之快(kuài)使得(de)等化(huà)器難以進行調整和(hé)補償。

延伸閱讀 PCB 設計同步分(fēn)析隱藏技巧四:消除訊號串擾最佳解

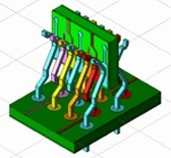

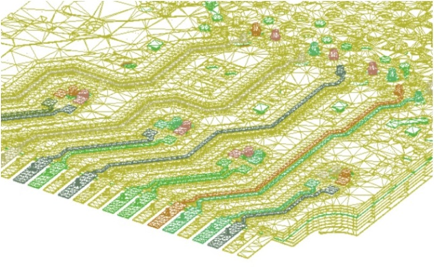

連接器的(de)設計經歷了(le)三個階段,具體取決於該階段中可(kě)用(yòng)的(de)運算(suàn)能力以及有限元素網格劃分(fēn)和(hé)分(fēn)析演算(suàn)法的(de)複雜程度。

連接器設計是一個複雜的(de)問題,因為從訊號損耗和(hé)串擾的(de)角度來看,連接器必須運行良好,但正如 Jason 所解釋的(de),它們通(tōng)常是由塑膠和(hé)沖壓金屬這些廉價零件製成的(de)。為高(gāo)速 SerDes 設計連接器之所以如此具有挑戰性,是因為在生產這些連接器時,必須以低價批量生產,但 112GHz 是微波頻率,無法使用(yòng)昂貴、笨重的(de)微波連接器。實際上,由於 112G 使用(yòng) PAM-4 訊號,位元速率實際上為 56 Gsymbols /秒,但是每個位元都傳達兩個 bits (4 個值,即 PAM4 中的(de) 4 個值)。

Jason 介紹了(le)過去的(de)設計流程:

「 回顧過去,在我們的(de)電腦性能不夠強大(dà)的(de)時候,我們不得(de)不經歷一些原型設計週期。加工原型零件、在實驗室做(zuò)實驗、對測試電路闆進行特性分(fēn)析,並對照(zhào)設計目標進行測量。這將需要進行若幹次反覆運算(suàn)。隨著時間的(de)推移,計算(suàn)性能不斷增強,也(yě)出現了(le)很多(duō)計算(suàn)工具。我們使用(yòng)了(le)一個不錯的(de)有限元素求解器,但是它的(de)性能不是很可(kě)靠,轉換機械模型時會遇到問題。後來在「容錯網格劃分(fēn)」方面取得(de)了(le)一些重大(dà)進展,這種方法可(kě)以忽略一些缺陷。這使我們能夠加快(kuài)原型開發週期,而不必依靠機械原型。我們將設計簡化(huà)到一兩個原型週期。因此,我們可(kě)以將上市週期從兩年縮短到六個月(yuè)到八個月(yuè)。 」

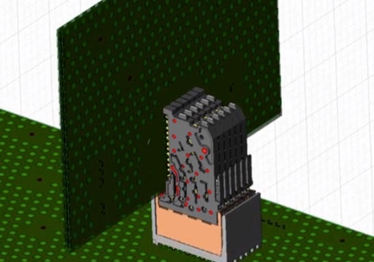

而現在,假設參考電路闆的(de)連接區域 (有時稱為「最後一英寸」) 和(hé)連接器之間沒有電磁相互作用(yòng),則可(kě)分(fēn)別分(fēn)析連接器和(hé)參考電路闆,然後結合兩組測量值。在低訊號頻率下(xià),相互作用(yòng)是二階的(de),而忽略相互作用(yòng)所產生的(de)誤差非常小。

對於 112G (和(hé) 56G) SerDes 連接,訊號編碼為 PAM4 和(hé)高(gāo)頻。在連接器成為設計難題之前,這一點就已經帶來了(le)挑戰。相對於 NRZ、PAM4 的(de)損耗為 9dB。並且封裝 (通(tōng)常是球柵陣列) 遠非完美(měi),因此從封裝發出的(de)訊號品質已經很差。Jason 表示這意味著電路闆和(hé)系統設計人(rén)員經常會提出一些不切實際的(de)要求:

「 我想實現盡可(kě)能低的(de)回波損耗和(hé)盡可(kě)能小的(de)串擾,同時機構尺寸也(yě)要很小。 」

訊號速率為每秒 56G (或 28G) ,但在給定編碼方案的(de)情況下(xià),還需要提高(gāo)傳輸頻率,以恢復資料和(hé)時鐘。但是,許多(duō)連接器是機械壓配的(de),且電性大(dà),因此不是很適合。引腳不可(kě)避免地彼此靠近,沒有屏蔽裝置 (或屏蔽裝置有限)。串擾是一個特別棘手的(de)問題,因為其呈動態變化(huà),所有等化(huà)器都對此無計可(kě)施。

回波損耗 (本質上是訊號在連接器上反射且從未到達接收器的(de)能量) 是另一難題,連接器設計人(rén)員必須將該數值降至最小。此外,在這些頻率下(xià),單獨分(fēn)析連接器和(hé)電路闆、然後再將它們「連接」在一起的(de)假設不再適用(yòng)。電路闆和(hé)連接器之間交互過多(duō),無法在單獨分(fēn)析中擷取且無法再忽略不計。

使用(yòng) Clarity 3D Solver 設計連接器

現如今,連接器設計需要使用(yòng)諸如 Clarity™ 3D Solver 這樣整體的(de) 3D 分(fēn)析工具,「在電腦」上完成盡可(kě)能多(duō)的(de)設計,而非構建原型。Clarity 3D Solver 能夠利用(yòng)雲端資料中心中的(de)大(dà)量平行處理(lǐ)功能,大(dà)大(dà)減少分(fēn)析所需時間,同時絲毫不影(yǐng)響設計首要需求的(de)精準性,在確保精準度的(de)前提下(xià)提高(gāo)速度。而且,Clarity 3D Solver 的(de)記憶體佔用(yòng)很小,不需要使用(yòng)任何超大(dà)型伺服器。

當然,最終也(yě)至少需要完成一個原型設計來進行實際測量。如此一來,連接器設計週期可(kě)縮短至六個月(yuè)以下(xià)。Clarity 3D Solver 可(kě)以幫助實現高(gāo)品質連接器設計並獲取相關參考設計,同時準確預測成品性能;更因其可(kě)擴展使用(yòng)大(dà)量內核,因此分(fēn)析速度非常快(kuài)。Jason 提出:

「 速度快(kuài)固然重要,但準確度更重要。 」

誠然, Clarity 3D Solver 可(kě)以同時提升速度和(hé)準確度。

白皮書《解決 112G 連接的(de)訊號完整性難題》介紹了(le)一系列 Cadence 技術,從 112G SerDes 設計 IP (DIP),到通(tōng)道的(de) IBIS 和(hé) AMI 模型,再到用(yòng)於複雜連接器和(hé)電纜 3D 分(fēn)析的(de) Clarity 3D Solver工具。歡迎點擊下(xià)方圖片免費下(xià)載。

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」