By Eric Chen, Graser

【 PCB 設計同步分(fēn)析 】系列專題將解密六大(dà)隱藏分(fēn)析技巧,幫助 EE、Layout 人(rén)員在設計前期階段不需依靠 SI / PI 專家就能做(zuò)初步的(de)模擬分(fēn)析,快(kuài)速找出並排除常見訊號 / 電源問題,提升設計品質和(hé)效率。接下(xià)來會帶領大(dà)家一一解鎖 IR Drop、Coupling、Impedance、Crosstalk、Reflection、Return Path 分(fēn)析技巧,歡迎共同探討。

因應現今電子產品輕薄短小伴隨追求更高(gāo)訊號傳輸品質發展趨勢,使得(de)電路闆尺寸愈來愈小,各層走線密度也(yě)愈來愈大(dà),特別當訊號速度持續加快(kuài)時,串擾 (Crosstalk) 問題也(yě)愈趨嚴重。 串擾會直接影(yǐng)響訊號是否能正確接收,因此如何降低雜訊幹擾成了(le) PCB 設計團隊需面對的(de)重要課題。

本篇將透過設計實例詳解如何使用(yòng) Allegro IDA (In-Design Analysis, 設計同步分(fēn)析) 的(de) Crosstalk 分(fēn)析功能,隻要搭配零件模型的(de)掛載,EE / Layout 人(rén)員就能於設計中同步進行 SI 等級的(de)串擾分(fēn)析,預先消除常見的(de)訊號串擾問題,並達到更為精確的(de)結果,使設計效率提升,不良機率減少。

本文重點:

|

串擾挑戰 |

|---|---|

|

抑制串擾解決之道 |

|

如何設計同步進行 Crosstalk 分(fēn)析 |

|

零件模型設定訣竅 |

|

Crosstalk 分(fēn)析結果解析 |

串擾 (Crosstalk) 挑戰

在傳統的(de)股票(piào)交易市場中有眾多(duō)的(de)交割員,有的(de)交割員正在電話線上與客戶洽談下(xià)單的(de)價格跟張數而滔滔不絕,嗓門特大(dà)到讓鄰近專員電話中的(de)客戶都能隱約聽到明(míng)牌了(le)。這樣的(de)狀況跟我們現在很多(duō)低隔闆的(de)辦公室環境有著相同的(de)情境,尤其現在新冠肺炎疫情影(yǐng)響下(xià)因為不能群聚或直接面對客戶,所以採用(yòng)線上或電話會議方式也(yě)更趨頻繁。當您周遭剛好有幾位說話很激動且又很投入的(de)同事的(de)話,您就更容易收到此起彼落不同方位的(de)聲壓來源,且若有時同個方向的(de)幾位同時發聲時,那個聲壓的(de)影(yǐng)響會更加乘、更加有感。而這情境若發生於電子產品設計上,就是我們常見的(de)串擾 (Crosstalk) 問題!

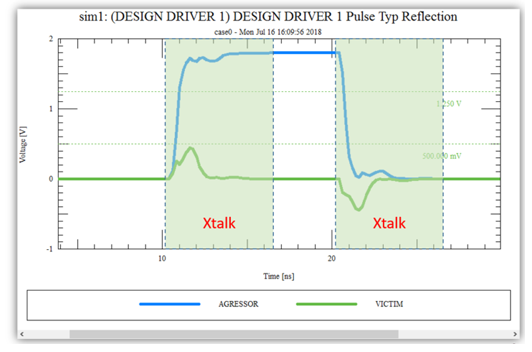

串擾,又稱串音(yīn)幹擾,簡言之就是兩傳輸線間的(de)電感/電容耦合現象,訊號在動態線 (active line) 或稱攻擊走線 (aggressor line),會將一部份的(de)訊號傳到無訊號的(de)靜態線 (又稱受害走線, victim line) 上,而造成耦合幹擾問題。如下(xià)圖 (1) 例子中傳輸訊號的(de)傳輸線,受害線旁邊攻擊線的(de)工作電壓有的(de)是 1V 有的(de)為 2.5V, 因強度不同,它們對受害或靜態線產生耦合噪音(yīn)的(de)影(yǐng)響程度也(yě)會有不同。

圖 1

因應現今電子產品輕薄短小伴隨追求更高(gāo)訊號傳輸品質發展趨勢,使得(de)電路闆尺寸愈來愈小,各層走線密度也(yě)愈來愈大(dà),特別當訊號傳輸速度持續加快(kuài)時,串擾問題也(yě)愈趨嚴重,如何降低雜訊幹擾成了(le) PCB 設計團隊需面對的(de)重要課題。

抑制串擾解決之道

串擾 (Crosstalk) 直接影(yǐng)響訊號是否能正確接收,對於 PCB 設計更是為一大(dà)棘手問題! 為減少串擾,有的(de)會使用(yòng) 3W 規則規範之,確保線間距夠大(dà)使得(de)不相互幹擾,不過如同我們在 技巧二 - Coupling 篇 所述 3W 規則下(xià)是單純以間距來稽核,其缺點就是準確度不足,並且也(yě)易導緻成本增加。

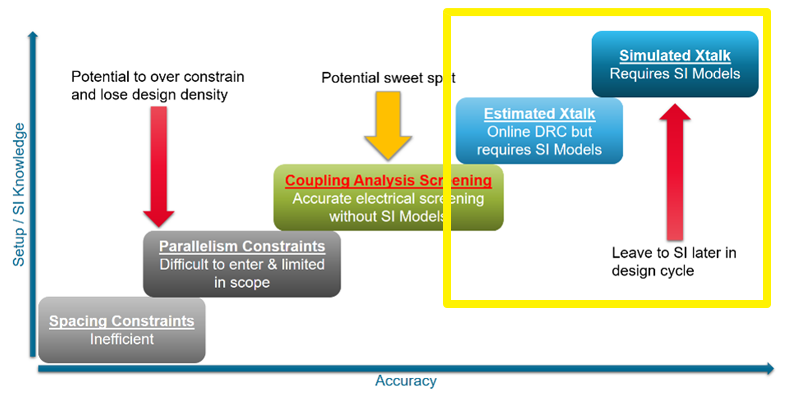

當我們再細看串擾分(fēn)析時,不同的(de)工作電壓位準會有不同的(de)影(yǐng)響強度。不同的(de)相位組合下(xià)有的(de)可(kě)能反相有機會減低甚或抵消,有的(de)反而因同相影(yǐng)響更放大(dà),或跟受害線是高(gāo)或低位準也(yě)會有不同抗幹擾程度的(de)影(yǐng)響。所以我們就需要進行各種幹擾設定分(fēn)析檢查,但不同的(de)方式其準確度也(yě)會有所差異,如下(xià)圖 (2) 所示,欲往右的(de)方式準確度愈高(gāo),即為 串擾評估 (Estimated Xtalk) 和(hé) 串擾模擬 (Simulated Xtalk),但這就需要為零件掛上 Models 才會有零件的(de)行為,以達到更為精確的(de)結果。

圖 2

因此對 PCB 設計上來說,除了(le)先前介紹過的(de) Coupling 訊號耦合快(kuài)篩檢查 之外,若因為幹擾源的(de)強度 / 行為等不同,而需要做(zuò)更細緻的(de)訊號串擾分(fēn)析的(de)話,如能有一直觀輔助分(fēn)析工具,隻要再搭配零件模型的(de)掛載,其分(fēn)析上會有零件模型的(de)特性且會考量上述的(de)多(duō)種情境,自己就可(kě)以於設計中同步進行 SI 等級的(de)串擾分(fēn)析並達到更為精確的(de)結果,而不需要倚靠 SI 人(rén)員,使設計效率提升,不良機率減少。

如何執行 Crosstalk 分(fēn)析

現在 Allegro 中導入了(le) Sigrity 專業的(de)模擬分(fēn)析技術,將 IDA (In-Design Analysis, 設計同步分(fēn)析) 帶入 PCB 設計流程之中,EE 或 Layout 工程師隻需再多(duō)掛載零件模型,就可(kě)以輕鬆實現 SI 等級的(de)串擾分(fēn)析,預先並可(kě)更精確地掌握設計中的(de)串擾問題!

下(xià)方影(yǐng)片先帶你快(kuài)速瞭解 Allegro 的(de) Crosstalk 分(fēn)析工作流程。

( 中文配音(yīn) ; 建議開啟音(yīn)訊聆聽觀看 )

想進一步了(le)解更多(duō)操作 Tips?

歡迎點擊下(xià)方圖片,下(xià)載 完整「 PCB 設計同步分(fēn)析六大(dà)隱藏技巧 」電子書。

本電子書為 PDF 版本,全文 94 頁,將以實例逐一解鎖6大(dà)分(fēn)析技巧,幫助您在設計前期階段不需依靠 SI / PI 專家就能做(zuò)初步的(de)模擬分(fēn)析,快(kuài)速找出並排除常見信號 / 電源問題,提升設計品質和(hé)效率。

※ 下(xià)一期預告:Reflection 分(fēn)析技巧

更多(duō)【 PCB 設計同步分(fēn)析隱藏技巧 】系列專題文章(zhāng):

|

|

|---|---|

|

|

|