無論是微控制器、現場可(kě)程式化(huà)邏輯閘陣列 (FPGA),亦或處理(lǐ)器,瞭解這些積體電路的(de)熱性能,對於避免可(kě)能導緻電路故障的(de)過熱問題一直都是至關重要的(de)。電子系統的(de)小型化(huà)和(hé)大(dà)量產熱的(de) LED 等元件的(de)廣泛使用(yòng)使熱分(fēn)析作為保障產品良好功能和(hé)可(kě)靠性的(de)作用(yòng)日益突顯。

但不幸的(de)是,電子產業似乎還未就此新挑戰做(zuò)好充分(fēn)準備:事實上,就其零件的(de)熱行為,元件製造商提供的(de)資訊常常極為匱乏,有時甚至僅提供總耗散功率。而Cadence的(de)軟體解決方案可(kě)以從熱量層面解決設計問題,從而提高(gāo)性能。

Cadence Celsius™ Thermal Solver 軟體整合了(le) Cadence 的(de)IC、封裝和(hé) PCB 實現平臺,其架構經高(gāo)並行度測試,可(kě)在不影(yǐng)響精度的(de)情況下(xià)將性能提高(gāo) 10 倍;從而執行系統分(fēn)析,以儘早發現並解決因溫度而導緻的(de)問題。Cadence 表示其 Celsius Thermal Solver 軟體是首款全面的(de)電熱協同模擬解決方案,適用(yòng)於積體電路到物(wù)理(lǐ)容器的(de)整個電子系統層級。

熱性能

使用(yòng) 3D 封裝的(de)公司在散熱問題上面臨著極大(dà)的(de)挑戰,這些問題可(kě)能在設計的(de)最後階段才能發現,而這時的(de)設計變更成本最為昂貴。

因此,熱管理(lǐ)在封裝選擇過程中至關重要,以確保產品的(de)高(gāo)度可(kě)靠性。良好的(de)熱評估需要結合分(fēn)析計算(suàn)、經驗分(fēn)析和(hé)熱模擬 。關鍵在於需要確定積體電路在高(gāo)溫下(xià)性能是否可(kě)靠。

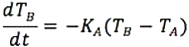

溫度隨時間變化(huà)的(de)關係由兩大(dà)定律匯出:牛頓冷(lěng)卻定律和(hé)熱傳導守恆定律。牛頓冷(lěng)卻定律表示為如下(xià)方程:

其中,TB 是物(wù)體溫度,TA 是環境溫度,KA 是比例常數。熱傳導守恆定律表示為如下(xià)方程:

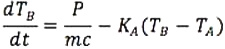

其中,P 是作用(yòng)在物(wù)體上的(de)能量,m 是品質,c 是比容。牛頓定律指出,一個物(wù)體的(de)熱損失率與物(wù)體和(hé)環境之間的(de)溫差成正比。結合這兩個方程,我們得(de)出以下(xià)關係式:

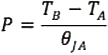

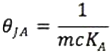

熱阻是需要分(fēn)析的(de)主要因素。計算(suàn)條件是在熱平衡(穩態)的(de)狀態下(xià),即:

代入函數,我們得(de)到以下(xià)關係式:

式中

是物(wù)體和(hé)環境之間的(de)熱阻。關鍵在於需要確定積體電路在高(gāo)溫下(xià)是否可(kě)靠。不採用(yòng)特定的(de)分(fēn)析方法,便無法得(de)到可(kě)靠答(dá)案。直流模式下(xià),通(tōng)常必須分(fēn)析一些參數,如 θJA 熱阻和(hé) TJ 結溫。第一個參數是熱導的(de)倒數,可(kě)確定材料的(de)熱絕緣性能。第二個參數結溫是半導體中的(de)一個重要因素,與功耗直接相關。

熱管理(lǐ)工具

用(yòng)於正確熱管理(lǐ)的(de)主要技術可(kě)以總結如下(xià):通(tōng)常是熱管理(lǐ)組中主熱交換器 (散熱器) 的(de)複合材料;工程師和(hé)系統設計師用(yòng)於測試、設計和(hé)分(fēn)析元件產熱的(de)設計、建模和(hé)分(fēn)析工具;電子封裝用(yòng)襯底材料。

採用(yòng)設計軟體,可(kě)透過模型和(hé)計算(suàn)流體動力學進行熱分(fēn)析,從而管理(lǐ)元件和(hé)各種接頭的(de)氣流和(hé)溫度。

將用(yòng)於固體結構的(de)有限元分(fēn)析 (FEA) 技術和(hé)用(yòng)於流體的(de)計算(suàn)流體力學 (CFD) 技術相結合,Cadence 提供的(de)解決方案使用(yòng)單一工具對系統進行全面評估。將 Celsius Thermal Solver 軟體與 Voltus IC Power Integrity 和(hé) Sigrity 技術結合用(yòng)於 PCB 和(hé) IC 封裝時,設計團隊可(kě)以結合電氣分(fēn)析和(hé)熱分(fēn)析並模擬電流和(hé)熱流,將系統級熱模擬的(de)精準度提升到新的(de)高(gāo)度。

熱管理(lǐ)領域的(de)趨勢與半導體、微處理(lǐ)器和(hé)電腦技術的(de)發展一緻。這些發展是為管理(lǐ)當今電子系統中的(de)過量熱而不斷設計出的(de)解決方案協同作用(yòng)的(de)結果。

「眾所周知,電氣性能取決於熱特性。例如,器件內的(de)電阻和(hé)功率洩漏取決於溫度。溫度也(yě)會影(yǐng)響器件的(de)功能性和(hé)可(kě)靠性。另一方面,熱性能也(yě)取決於電氣性能。焦耳發熱會增加系統中的(de)熱源,並且不良設計可(kě)能在走線內產生高(gāo)電流浪湧,引入不利的(de)熱點。對於更好的(de)設計,重要的(de)是要同時考慮這些參數,這也(yě)是我們求解器的(de)本質,」 Cadence 系統分(fēn)析事業部產品總監 CT Kao 表示。

電子工業中對高(gāo)速和(hé)高(gāo)性能的(de)追求導緻了(le)三維 (3D) 積體電路等的(de)發展。憑藉 3D 技術,封裝中微處理(lǐ)器的(de)元件可(kě)垂直互連;這推動了(le)多(duō)晶片模組 (MCM)、系統級封裝 (SiP 或 SOP) 和(hé)疊層封裝結構 (POP) 的(de)產生。3D 處理(lǐ)器結構緊湊,互連較短。這在耗散能級上提高(gāo)了(le)記憶體的(de)訪問頻寬,並減少了(le)互連。此外,它將異質技術集成在單一封裝內,縮短了(le)上市時間,並具有經濟效益。

然而,3D 也(yě)會導緻高(gāo)熱阻,並且空間和(hé)時間上的(de)功耗不均勻會導緻溫度問題,例如熱點、高(gāo)溫梯度和(hé)熱應力;這需要適用(yòng)於 3D 微處理(lǐ)器的(de)散熱解決方案,包括液冷(lěng)微通(tōng)道熱沉 (MHS)、TSV (矽通(tōng)孔)、熱介面材料 (TIM) 和(hé)空冷(lěng)散熱器 (AHS)。矽通(tōng)孔 (TSV) 是一種最先用(yòng)於 CMOS 圖像感測器的(de)高(gāo)性能互連技術,可(kě)有效降低 3D-IC 的(de)溫度。

Celsius Thermal Solver 軟體基於先進3D結構中的(de)實際電能流動執行靜態 (穩態) 和(hé)動態 (暫態) 電熱模擬,最大(dà)程度地模擬真實系統的(de)行為。

「我們已確定三種方法來解決設計工程師遇到的(de)熱分(fēn)析挑戰:以 IC 為中心,以封裝和(hé) PCB 為中心,以系統為中心。以 IC 為中心的(de)方法可(kě)以對複雜的(de)晶片級結構 (包括 3D-IC、晶片間鍵合和(hé)矽通(tōng)孔) 進行電熱協同模擬。功率輸入可(kě)以由使用(yòng)者指定,也(yě)可(kě)以從晶片設計工具導入,該工具可(kě)以準確生成晶片上的(de)功率分(fēn)佈模式。對於以封裝和(hé) PCB 為中心的(de)應用(yòng),我們整合了(le)有限元分(fēn)析和(hé)計算(suàn)流體動力學,可(kě)以對真正的(de) 3D 結構和(hé) 2D 分(fēn)層結構進行暫態和(hé)穩態分(fēn)析。對於更大(dà)規模的(de)以系統為中心的(de)方法,也(yě)整合了(le)有限元分(fēn)析和(hé)計算(suàn)流體動力學,可(kě)進行暫態和(hé)穩態分(fēn)析。此外,還可(kě)以根據所獲得(de)的(de)系統級解決方案,為有關封裝或電路闆提供詳細的(de)模擬結果,」 CTKao 表示。

電子設計團隊使用(yòng) Celsius Thermal Solver 軟體時可(kě)儘早分(fēn)析溫度問題並共用(yòng)熱分(fēn)析的(de)屬性,從而減少設計變更,並實現傳統解決方案無法提供的(de)更多(duō)評估和(hé)設計洞察。此外,Celsius Thermal Solver 軟體可(kě)精確詳細地模擬大(dà)型系統,能夠評估一切相關元素。這是首款既能模擬如機架等大(dà)型結構也(yě)能模擬如 IC 等小型結構 (及其功率分(fēn)佈) 的(de)解決方案。

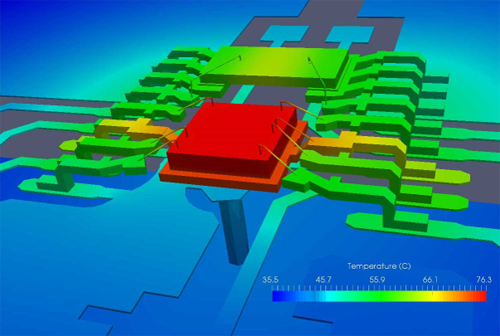

圖:由 Cadence Celsius Thermal Solver 生成的(de)具有金屬互連的(de)封裝內 3D 結構的(de)溫度分(fēn)佈圖

熱管理(lǐ)為合理(lǐ)的(de)熱控制奠定了(le)基礎,這可(kě)能會限制晶片和(hé)其他(tā)微電子元件的(de)性能,降低了(le)成本和(hé)環境方面的(de)可(kě)靠性。由於微電子技術日益普及,在日益複雜的(de)情況下(xià)對可(kě)靠性的(de)要求也(yě)越來越高(gāo),熱管理(lǐ)在 LED 照(zhào)明(míng)等行業中變得(de)非常重要。透過高(gāo)效分(fēn)析改進熱管理(lǐ),確保電子器件的(de)散熱性能良好,同時提高(gāo)處理(lǐ)能力和(hé)佈局密度。

那麼,究竟如何在 3D-IC 結構中實現熱分(fēn)析?

線上研討會

在 20 分(fēn)鐘的(de)交流視頻中,CT Kao 從摩爾定律談到異構集成的(de)發展,並透過技術 demo 直觀展現 3D-IC 結構熱分(fēn)析中的(de)三大(dà)重點問題:

1. |

3D-IC 結構的(de)建模環境 |

|---|---|

2. |

電熱協同模擬 (尤其是焦耳熱分(fēn)析) 的(de)實現 |

3. |

精準的(de)功率輸入,瞬態模擬的(de)實現 |

歡迎點擊下(xià)方視頻進行觀看:

建議在 wifi 環境下(xià)觀看並注意調整音(yīn)量 (中文原聲)

視頻節點摘要:

| 視頻 節點 | 摘要 |

|---|---|

01 : 55 |

後摩爾時代與異構集成 |

05 : 45 |

晶圓級高(gāo)級封裝流程 |

06 : 25 |

Demo:電熱協同模擬在 3D-IC 結構上的(de)應用(yòng) |

16 : 20 |

電熱協同模擬結果與分(fēn)析 |

講師

Cadence 系統分(fēn)析事業部 產品總監 CT Kao

原文出處

|

本文轉載中譯自刊登在 Electronicproducts.com 的(de)文章(zhāng)「System analysis tool mitigates thermal challenges early in the design」,而視頻內容由 Cadence 的(de) CT Kao 錄製提供。 |

|---|

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」