日前 Cadence 收購了(le) National Instruments (國家儀器; 以下(xià)簡稱 NI)旗下(xià)的(de) AWR。為了(le)解 AWR 的(de)歷史和(hé)產品,以及對 AWR 有通(tōng)盤的(de)了(le)解,本文訪問 AWR 行銷副總裁 Sherry Hess。

總體而言,AWR 的(de)工具是針對於通(tōng)訊系統(無線電)和(hé)雷達等電子設備之射頻前級所提供的(de)設計軟體,主要用(yòng)於實現三五族半導體材料(如 GaAs 和(hé) GaN)、RF / 混合訊號 PCB,以及多(duō)晶片模組等的(de)單片微波 IC(MMIC)。AWR 設計環境平台與矽基 IC 工具(尤其是矽基數位晶片)有很大(dà)的(de)不同,因為 RF 設計是高(gāo)度互動的(de)工作,擁有特定的(de)模型和(hé)分(fēn)析方式、極低電晶體數(1-100 s),並且受佈局的(de)影(yǐng)響很大(dà)。

AWR 簡介

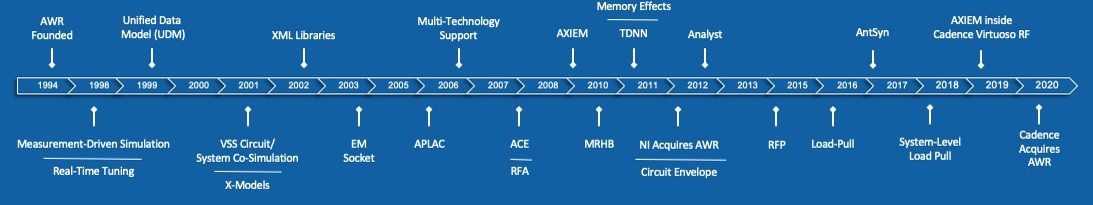

AWR 由休斯公司 (Hughes)的(de)微波工程師 Joe Pekarek 於 1994 年創立,他(tā)對當時既有的(de)RF設計軟體感到失望。通(tōng)過休斯贊助的(de)博士學位計劃,Joe Pekarek 開發了(le)一個早期版本作為他(tā)的(de)論文的(de)一部分(fēn),該版本最終成為 AWR 軟體的(de)一部分(fēn)。然後,他(tā)與其他(tā)同事一起創立了(le) AWR (Applied Wave Research)。新公司及其旗艦產品 Microwave Office 通(tōng)過其直觀的(de)用(yòng)戶介面,電路原理(lǐ)圖輸入(schematic capture)/ 佈局功能,同時引入了(le)創新的(de)設計輔助工具(即時調整),使得(de)早期轉換(early converts)得(de)以實現。

隨著 AWR 公司持續增成長,AWR 在 2011 年被 NI 收購,這是 NI 緻力將其專業領域擴展到 RF / 無線產業策略的(de)一部分(fēn)。之後,NI 和(hé) Cadence 針對迅速發展的(de) 5G 通(tōng)訊、IoT 和(hé)航空業等技術上的(de)瓶頸,共同發展策略以及最佳因應方式。最初合作的(de)項目,就是 NI 與 Cadence 密切合作將 AWR 的(de) AXIEM 在 2018 年整合入 Virtuoso RF 環境中。

AWR 的(de)客戶來自採用(yòng)無線技術的(de)各行各業,從航太、國防到電信設備製造商。 Sherry 表示,AWR 希望在大(dà)型企業客戶能展現大(dà)幅增長,而 Cadence 收購 AWR 在此領域將是一大(dà)利多(duō),因為 Cadence 已經與許多(duō)公司合作,而 AWR 將幫助填補、建立和(hé)整合Cadence 的(de) RF / 微波設計的(de)產品組合。

學術界也(yě)有許多(duō)採用(yòng)案例,因為它可(kě)以在五分(fēn)鐘內完成安裝,並在 PC 上運行,因此非常適合教授結合微波設計課程使用(yòng)。北(běi)卡羅來納州立大(dà)學的(de) Alan Victor 教授表示:『 作為開發單片微波 IC 的(de)首席工程師,我指導學生參加進階設計課程。我的(de)學生使用(yòng) AWR 軟體,設計了(le) LNA 和(hé)微波 PA。不用(yòng)說,這對學生是一個挑戰,然而這軟體方便使用(yòng)的(de)特性確保了(le)最後設計成功。 』

AWR 產品組合

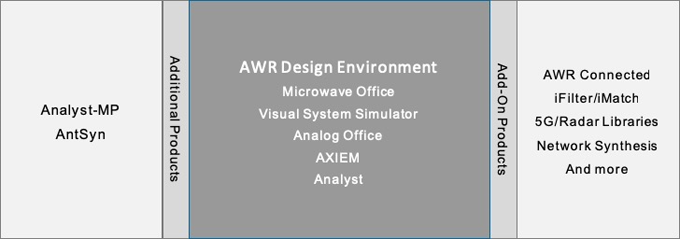

AWR 產品組合在 AWR 設計環境平台內運行,作為設計輸入(電路圖 / 佈局)、分(fēn)析(系統 / 電路 / 電磁)、優化(huà)、良率分(fēn)析和(hé)結果繪圖的(de)整合界面。AWR 的(de)旗艦產品 MicrowaveOffice 是一種 RF 電路模擬器,用(yòng)於開發前端元件,例如功率放大(dà)器、低噪聲放大(dà)器、濾波器、混頻器等。 AXIEM 是一種矩量法(MoM)、3D 平面電磁分(fēn)析工具,用(yòng)於描述(S 參數)被動結構和(hé) RF 互連的(de)特性,AXIEM 已整合到 Microwave Office 和(hé) Virtuoso RF 中。還有一個名為可(kě)視系統模擬器(VSS)的(de)工具,該工具使用(yòng)基於行為模型的(de) RF 和(hé) DSP 模組來支持通(tōng)訊 / 雷達系統級開發。 VSS 支持許多(duō)系統分(fēn)析(鏈路預算(suàn)規劃、ACPR 和(hé) EVM,串接式噪聲、IP3、頻譜),組件規格 / 驗證和(hé)架構設計。憑藉其符合標準的(de)元件和(hé)測試平台,VSS 可(kě)以用(yòng)於如測試 5G 訊號激發的(de)設備。還有其他(tā)一些專門的(de)工具,例如用(yòng)於天線合成和(hé)優化(huà)的(de) AntSyn、5G / 雷達元件等。

在開始創建 Virtuoso RF 並集成 AXIEM 時,Cadence 面臨的(de)挑戰之一,是 OA 數據庫不支持 RF 設計所需的(de)所有奇怪幾何形狀(按照(zhào) IC 設計標準):圓形、圓弧形、任意角度路線、接合線等。這些根本不會出現在 OA 最初為之設計的(de)傳統 IC 設計中。另外,矽光(guāng)子設計也(yě)需要許多(duō)這樣的(de)設計,RF 訊號和(hé)光(guāng)都不太喜歡繞過尖角。

對於晶片上 (on-chip) 分(fēn)析是否也(yě)是需要? Sherry 表示:『 晶片分(fēn)析當然需要 AWR 技術,這就是在 Cadence 收購前,AXIEM 電磁求解器就被視為需要直接整合到 Virtuoso RF 的(de)原因。 』

Pocket Radar 的(de) Phil Jobson 說:『 進行 RF 設計並完成首次設計成功是一項艱鉅挑戰。RF 的(de)實體層設計很重要,不僅是 RF / 微波裝置的(de)細節,還包括裝置、附近的(de)走線和(hé)其他(tā)導電表面之間的(de)互相作用(yòng)。AWR 設計環境讓我能夠快(kuài)速建模和(hé)重新設計 24GHz 微波系統,並完成首次設計成功。 』