今年 4 月(yuè)在 Cadence 用(yòng)戶大(dà)會—— CDNLive 矽谷站,Cadence 公司 CEO 陳立武(Lip-Bu Tan)宣佈了(le)發佈 Cadence® Clarity™ 3D Solver 產品。這是 Cadence 公司系統級分(fēn)析策略下(xià)推出的(de)第一款產品,突破性的(de)電磁場(EM)模擬技術可(kě)提供 10 倍的(de)性能、無限容量,以及黃金標準的(de)模擬精度。

對此,Teradyne 半導體測試事業部的(de)工程副總裁 Rick Burns 亦表示:

「對於傳送速率超過十億位元以及高(gāo)層數(大(dà)於 30 層)、高(gāo)密度的(de) PCB,我們依靠對複雜結構的(de)精確互連模型提取來支援信號完整性分(fēn)析。使用(yòng) Cadence Clarity 3D Solver,我們隻需花費曾經的(de)一小部分(fēn)時間即可(kě)達到所需精度。這為我們開闢了(le)一個分(fēn)析模擬的(de)新時代,因為我們現在可(kě)以在之前運行一次模擬的(de)時間裡運行數十次模擬。這減少了(le)重複設計,並說明(míng)我們實現對客戶的(de)承諾——以最低的(de)測試成本為客戶提供最高(gāo)的(de)產出。」

那麼,這一突破性的(de)性能究竟是如何實現的(de)?

歡迎點擊下(xià)方視頻尋找答(dá)案。

視頻全長 8 分(fēn)鐘,涵蓋如下(xià)內容:

► |

00:30 當今系統設計挑戰 |

|---|---|

► |

01:22 傳統有限元分(fēn)散式運算(suàn)與 Clarity 3D Solver 創新方案比較 |

► |

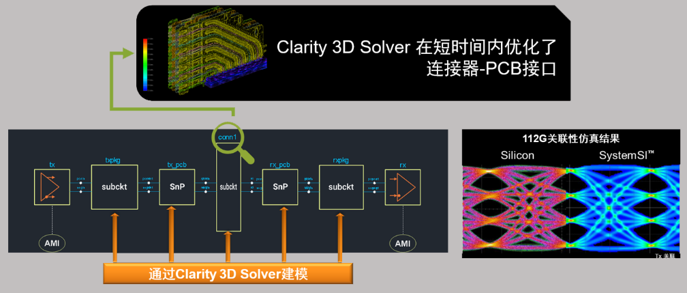

04:26 112G SerDes 分(fēn)析示例 |

► |

05:40 112G SerDes 和(hé) DDR4 介面性能比較示例 |

(建議在 wifi 環境下(xià)觀看)

本文及視頻授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」