條理(lǐ)性是設計有效率的(de)關鍵,缺乏條理(lǐ)性會降低我們 PCB 設計的(de)效率。以設計規則為例:在開始新專案時,許多(duō) PCB 設計工程師傾向於按照(zhào)自己的(de)設計規則來重新打造設計,而不是依靠一個適當的(de)、有條理(lǐ)的(de)、系統的(de)規則方法。當時間因素至關重要時,這種做(zuò)法會大(dà)大(dà)降低專案進展,本文將討論可(kě)以提高(gāo)多(duō)層電路闆設計效率的(de)規則方法。

多(duō)層電路闆設計規則:一緻性與零件庫管理(lǐ)

為每個正在進行的(de)新專案重新創建 PCB 設計規則是一種平常做(zuò)法。這可(kě)能是因為設計部門尚無適當的(de)制程來複用(yòng)規則,或者隻是因為 PCB 設計工程師不想重複使用(yòng)這些規則。無論出於何種原因,這都表明(míng)需要更新設計工作流,以提高(gāo)設計效率和(hé)一緻性。如果不進行改進和(hé)提升,當前的(de)工作流可(kě)能需要花費大(dà)量額外的(de)時間和(hé)精力,且不一緻性會導緻繼承問題。

每種多(duō)層電路闆的(de)設計規則都不相同。通(tōng)常,我們期望 PCB 設計工程師充分(fēn)瞭解規則,並能夠在每個設計中輸入相同的(de)值。然而,即使他(tā)們的(de)記憶正確,也(yě)總有輸入錯誤值的(de)可(kě)能性。

缺乏一緻性可(kě)能會最終導緻整個系統中的(de)多(duō)層電路闆元件受到不同規則的(de)控制。如果在同一製造面闆上使用(yòng)不同的(de)電路闆,這可(kě)能會是一個更大(dà)的(de)問題。如果在不同設計之間的(de) 一層結構不同,則可(kě)能會導緻製造延期、結構不良或重新設計。

為了(le)簡化(huà)創建多(duō)層電路闆設計規則的(de)程式,最好保存和(hé)管理(lǐ)這些規則,以備將來再次使用(yòng)。用(yòng)於保存和(hé)管理(lǐ)規則的(de)地方我們稱之為「零件庫 (library)」,其中包括電路圖符號、模擬模型、設計約束、PCB footprints 和(hé) STEP 模型。零件庫可(kě)以像存儲資料的(de)中央文件目錄一樣簡單,也(yě)可(kě)以是由多(duō)個目錄位置和(hé)連結組成的(de)複雜系統。

無論如何設置 CAD 零件庫,設計規則集都可(kě)以同樣的(de)方式保存。為了(le)成功管理(lǐ)設計規則的(de)「零件庫」,系統中應該有三種基本實踐:

|

位置: |

|---|---|

在伺服器上建立一個所有用(yòng)戶都可(kě)以訪問的(de)中心位置。在個人(rén)電腦上保存頻繁使用(yòng)的(de)設計規則和(hé)其他(tā)類型的(de)資料,以備日後使用(yòng)。這種做(zuò)法可(kě)以限制其他(tā)人(rén)訪問,且保存檔更容易被更改或刪除。 |

|

|

命名約定: |

使用(yòng)其他(tā)人(rén)更容易識別的(de)方式來為保存的(de)檔命名。日期、描述和(hé)工作編號都是很好的(de)檔案名選擇。「Joes_really_cool_design_rules.txt」這種命名方式並不推薦。 |

|

|

限制編輯許可(kě)權: |

最好能夠讓設計團隊成員在將自己的(de)檔保存到該位置後便不能在此位置中進行編輯。通(tōng)常,在上一次使用(yòng)之後突然發現六層電路闆的(de)設計規則發生了(le)變化(huà)將十分(fēn)令人(rén)崩潰。設計團隊成員可(kě)以隨時將這些規則複製到新檔、進行更改,然後用(yòng)新名稱命名並保存。 |

延伸閱讀 可(kě)靠電路設計指南(nán)下(xià)載|如何快(kuài)速找出潛在線路錯誤與零件 Derating 問題

當設計資料存儲系統就位後,便利用(yòng)其來保存檔。

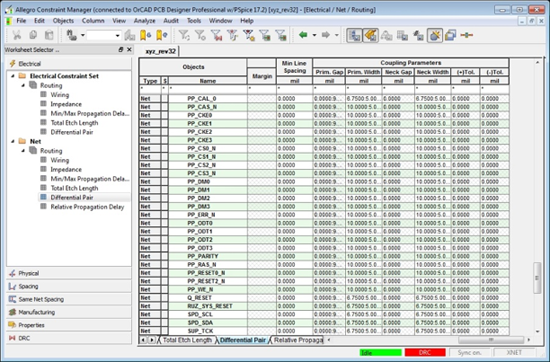

實用(yòng)軟體如 Allegro® Constraint Manager 簡化(huà)了(le)控制和(hé)編輯設計規則的(de)流程

多(duō)層電路闆約束、測試和(hé)系統級完整性

即使隻有一塊電路闆可(kě)用(yòng),信號完整性和(hé)電源完整性仍然是設計中需要謹慎考慮的(de)關鍵因素。與當今的(de)多(duō)層電路闆系統相比,單一電路闆的(de)考量因素則較為簡單:電源更簡單、幹擾元件更少、信號傳輸距離更短。

系統級信號完整性和(hé)電磁幹擾 (EMI)

確保適當的(de)多(duō)層電路闆信號完整性 (SI) 的(de)最佳方式是擁有一個可(kě)靠和(hé)準確的(de)信號完整性分(fēn)析及模擬工具,以便在每一步流程中與設計協同工作。相互作用(yòng)的(de)高(gāo)速和(hé)低速信號肯定會引發信號完整性問題,此外,與所有有源元件的(de)串擾可(kě)能性更大(dà)。因此由於高(gāo)速信號間的(de)相互作用(yòng),多(duō)層電路闆設計幾乎總是面臨更大(dà)的(de)電磁幹擾風險。

延伸閱讀 PCB 設計同步分(fēn)析 6 大(dà)隱藏技巧四 : 消除訊號串擾最佳解

透過有效工具,或者借助我們的(de)知識增強其功能,來分(fēn)離類比和(hé)數位信號、採用(yòng)智慧走線 (意味著電路中沒有直角走線) 並保持信號和(hé)返回電流緊密耦合,可(kě)以顯著降低電磁幹擾問題。

分(fēn)區設計和(hé)多(duō)層電路闆成本分(fēn)析

基於目的(de)和(hé)功能對元件進行物(wù)理(lǐ)分(fēn)組,可(kě)使許多(duō)因素達到更高(gāo)的(de)安全性。這一過程稱為 PCB 分(fēn)區,可(kě)在多(duō)層電路闆闆設計中將子系統視為一組元件。

適當的(de) PCB 分(fēn)區可(kě)簡化(huà)操作,提高(gāo)成本效益,例如:

1. |

模組化(huà),或者將標準化(huà)元件整合至更大(dà)的(de)多(duō)種產品設計 |

|---|---|

2. |

電路闆間距和(hé)外殼電路實際安裝 |

3. |

製造更便宜、更小型的(de)連接主機闆的(de)電路闆,而不是昂貴的(de)多(duō)層電路闆疊層結構中的(de)配件 |

4. |

在多(duō)層電路闆設計中,分(fēn)離類比和(hé)數位電路,減少電磁幹擾 |

PCB 約束管理(lǐ)器和(hé)多(duō)層電路闆輔助設備

雖然許多(duō)約束管理(lǐ)器已配備完成工作所需的(de)阻抗、疊層結構、Net 和(hé)平面選擇,但一個優秀的(de)約束管理(lǐ)器還會考慮元件列表和(hé)參數,這將使多(duō)層電路闆設計更易於管理(lǐ),尤其是處理(lǐ)每塊電路闆上的(de)數千個獨立元件時。

多(duō)層電路闆約束管理(lǐ)器可(kě)管理(lǐ)進階 net 層級、設置散熱需求、在約束條件下(xià)快(kuài)速調整散熱規範並處理(lǐ)信號條件。

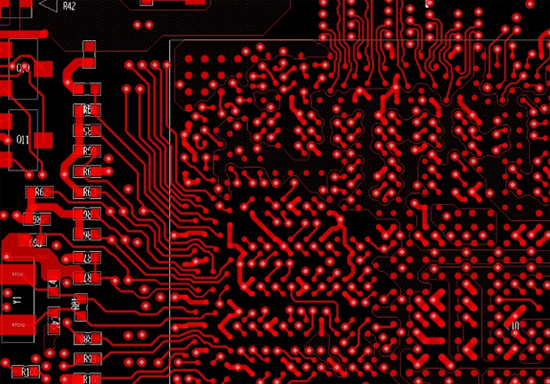

如此複雜的(de)走線依賴於正確的(de)設計規則和(hé)適當的(de)約束

多(duō)層電路闆系統架構和(hé)設計工具

對於系統的(de)整體完整性來說,管理(lǐ)多(duō)層電路闆系統中的(de)連接器至關重要。儘管我們可(kě)能已經對一切做(zuò)了(le)適當的(de)規劃,但確定適合設計的(de)連接器時,確定連接器在外殼環境中的(de)處理(lǐ)方式、是否設計電路闆垂直疊層或水(shuǐ)準分(fēn)層以及潛在的(de)腐蝕 (環境、電流、電解等),所有這些都至關重要。

在整個 layout 階段,都應該對連接器進行謹慎管理(lǐ),如果尚未充分(fēn)考慮,則可(kě)能需要更加關注設計規則和(hé)約束管理(lǐ)器。在我們經過長時間的(de)重新走線而沒有足夠的(de)精力進行最後檢查 (比如檢查過孔阻抗值) 時,設計規則檢查 (DRC) 可(kě)以使我們清楚地看到違規行為並迅速解決問題,而不是一味煩惱焦慮。

延伸閱讀 PCB 設計同步分(fēn)析 6 大(dà)隱藏技巧三 : 分(fēn)秒掌握訊號特性阻抗

當設計規則最開始應用(yòng)於 PCB 設計工具中時,其操作並不簡單。使用(yòng)者經常必須流覽多(duō)個功能表並填寫多(duō)個不同的(de)表格。通(tōng)常,這些系統保存資訊的(de)方法也(yě)並不可(kě)靠,或者即使保存了(le),也(yě)僅僅是保存在了(le)一個非格式化(huà)的(de)文字檔中。但是,時代在發展。

當今的(de) PCB 設計系統通(tōng)常具備先進的(de)設計規則和(hé)約束,可(kě)透過試算(suàn)表類型的(de)實用(yòng)程式進行訪問。此外,這些規則和(hé)約束通(tōng)常與設計系統中的(de)其他(tā)功能相關聯。例如,阻抗計算(suàn)器可(kě)以將值直接輸入規則和(hé)約束中,而無需手動輸入資料。

Allegro® PCB Designer 軟體具備上文所述的(de)試算(suàn)表類型規則和(hé)約束系統,可(kě)以讓您的(de)設計工作變得(de)更加輕鬆。透過該工具,您不僅可(kě)以創建和(hé)修改自己的(de)設計規則,更可(kě)以保存這些設計規則以備將來使用(yòng)。

更多(duō)多(duō)層闆設計內容

|

|

|---|---|

|

|

|

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」