我們並不能用(yòng)單層印刷電路闆(PCB)實現全部的(de)設計。儘管微型化(huà)取得(de)了(le)進步,單個晶片上壓縮電晶體的(de)數量在穩定增長;但是,諸如電磁幹擾、溫度限制和(hé)電路複雜度整體上升等因素已使多(duō)層電路闆設計成為 PCB 產業的(de)必然。

多(duō)層電路闆 PCB 系統是一種需要將一個以上 PCB 協同工作的(de)設計。現在讓我們來深入研究多(duō)層電路闆 PCB 系統的(de)常見器件佈局策略,從分(fēn)區到電路闆內連接再到三維設計考量以及減少 EMI(電磁幹擾)的(de)設計技巧。

分(fēn)區

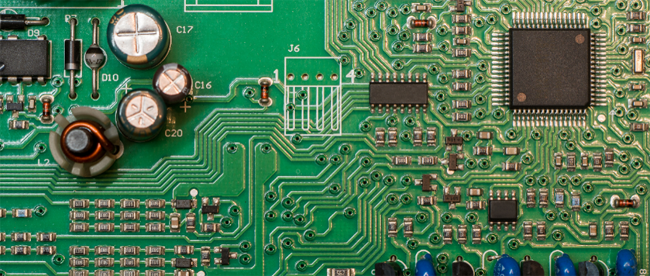

PCB 分(fēn)區(不要與用(yòng)於記憶體用(yòng)途的(de)硬碟驅動器數位分(fēn)區相混淆)是基於器件功能的(de)實體分(fēn)組。每個功能子系統均可(kě)視為一組器件及其配套電路。

例如,典型主機闆可(kě)以進一步細分(fēn)為許多(duō)功能單元,如處理(lǐ)器時鐘邏輯、匯流排控制器、匯流排界面、記憶體、視頻 / 音(yīn)訊處理(lǐ)模組和(hé)週邊設備(輸入 / 輸出)。

在多(duō)層電路闆 PCB 設計情況下(xià),分(fēn)區之後可(kě)以將器件重新組建到不同的(de)電路闆上。這樣做(zuò)的(de)原因有很多(duō),其中包括:

|

EMC(電磁相容性): |

|---|---|

透過最優方法(例如分(fēn)離類比電路和(hé)數位電路)來減少電磁幹擾(EMI)問題(我們將在本文後面部分(fēn)研究這些減少電磁幹擾的(de)技術)。 |

|

|

成本: |

對於需要較昂貴多(duō)層電路闆架構的(de)功能電路,採用(yòng)可(kě)連接到主機闆的(de)較小電路闆會使價格更便宜。 |

|

|

模組化(huà): |

在設計多(duō)個產品時,可(kě)以透過將模組標準化(huà)單元整合在設計中以節省工作時間和(hé)成本,從而使我們可(kě)以按照(zhào)需要在底闆上添加功能(例如 Arduino 晶片組中的(de) think shields)。 |

|

|

3D 空間: |

僅僅因為我們可(kě)以將所有電路安裝到單層標準 10x16 英寸電路闆上(大(dà)約是一個披薩盒的(de)大(dà)小),並不意味著我們的(de)設計能通(tōng)過設備外殼實際尺寸和(hé)形狀的(de)要求。 |

圖片來源網路

內部電路闆連通(tōng)性

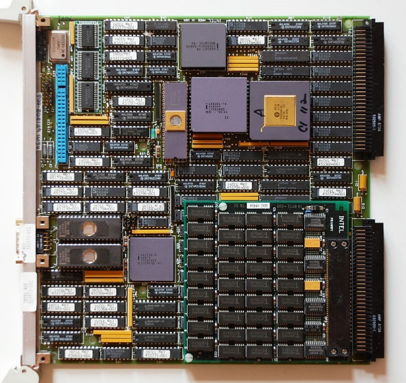

內部電路闆連接器是多(duō)層電路闆 PCB 設計的(de)基礎。不同類型的(de)內部電路闆連接方式如下(xià):

|

闆對闆方式: |

|---|---|

公 / 母式引腳 / 插座接頭是最常見類型的(de)闆對闆連接器。它們往往成本很低,對於高(gāo)速電路而言卻並不理(lǐ)想。但是我們可(kě)以使用(yòng)較多(duō)引腳數和(hé)多(duō)個引腳來處理(lǐ)較大(dà)電流情況。良好的(de)做(zuò)法是要注意製造商產品每個引腳的(de)額定電流處理(lǐ)能力。 |

|

|

插卡邊緣連接器: |

從一塊電路闆邊緣引出的(de)走線可(kě)以插入另一塊電路闆上的(de)匹配插座中,使兩塊闆互相垂直。插卡邊緣連接器通(tōng)常用(yòng)作主機闆、背闆或立式插卡上的(de)擴充槽,用(yòng)於向電腦添加更多(duō) RAM 的(de) PCI-e 插槽(周邊元件連接通(tōng)道)就是一個典型範例。耐腐蝕金觸點與電路闆上的(de)走線直接接觸,使其對高(gāo)速數位訊號電路極為重要。 |

|

|

電路闆對導線: |

在許多(duō)情況下(xià),可(kě)能必須將電纜和(hé)電線連接到電路闆上。典型範例是特定伺服器機房(fáng)內的(de) FFC(軟性薄膜電纜)、FPC(軟性印刷電纜)和(hé)帶狀連接器。 |

|

|

直接焊接: |

齒形的(de)過孔可(kě)以讓我們創建 PCB 模組,這樣可(kě)以很容易焊接在一起。這種方法對於將小型無線模組連接到較大(dà)電路闆的(de)情況較為流行,隻要確保符合高(gāo)焊接標準(例如 IPC-A-610 或 J-STD-001 標準)即可(kě)。 |

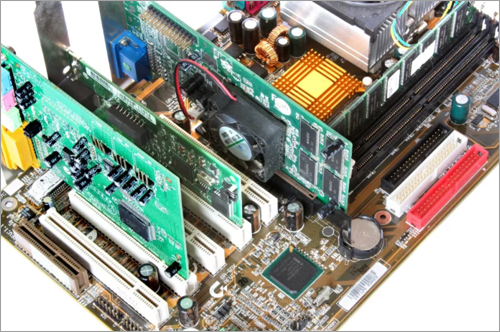

無論我們的(de)設計需要創建互相堆疊在一起的(de) PCB 堆疊結構,還是將電路闆滑動放入機架或底闆,重要的(de)是確保能夠在構成產品的(de)不同電路闆之間建立牢固連接。

圖片來源網路

減少電磁幹擾

電磁相容性 / 電磁幹擾問題是多(duō)層電路闆 PCB 設計背後的(de)主要驅動因素之一。電源和(hé)天線都會產生電磁幹擾,對高(gāo)性能電子設備的(de)需求意味著高(gāo)速訊號電路在未來幾年內隻會變得(de)更加流行。

多(duō)層電路闆設計為我們提供更多(duō)空間以適應電磁相容性 / 電磁幹擾的(de)最佳方法。諸如將類比訊號和(hé)數位訊號分(fēn)開、避免在狹小電路闆上出現直角走線以及根據需要合理(lǐ)使用(yòng)多(duō)層電路闆等內容。與此同時,多(duō)層電路闆設計也(yě)引入了(le)新的(de)關注點,要求我們將分(fēn)析從單層電路闆擴展到電路闆與整個系統之間的(de)連接。

以上因素與 3D 設計綜合考量

多(duō)層電路闆設計就像一個昂貴的(de) 3D 拼圖。組成系統的(de)每塊電路闆都必須裝入一個物(wù)理(lǐ)外殼或主機殼中。沒有什(shén)麼比起草(cǎo)「完美(měi)」CAD 圖紙更困難的(de)了(le),採購了(le)所有電路闆、部件和(hé)連接器之後,卻在組裝時發現在 3D 角度(多(duō)層電路闆)上存在問題。更糟的(de)是,沒有留下(xià)足夠的(de)空間進行適當通(tōng)風,這會導緻產品與熱有關的(de)性能退化(huà)。到這一步,我們甚至還沒有觸及電磁幹擾的(de)問題。

現在,我們可(kě)以使用(yòng)軟體追蹤所有這些「拼圖」。隨著Cadence® Sigrity™ 最新版於 2018 年 7 月(yuè)發佈,Sigrity 工具與 Cadence Allegro® 技術和(hé)新型 3D 工作平臺整合在一起 〈 Cadence Sigrity 2018 整合 3D 設計與分(fēn)析 大(dà)幅縮短 PCB 設計週期 〉,在 PCB 設計中架起了(le)機電領域之間的(de)橋樑。設計人(rén)員現在可(kě)以對多(duō)層電路闆 PCB 設計採取整體方法,對所有電路闆、連接器、電纜、插座和(hé)其它結構進行訊號完整性分(fēn)析。

瞭解更多(duō),歡迎點擊「 圖文解密三維建模與電磁場分(fēn)析新工具 」。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」