本文要點

|

BGA 封裝尺寸小巧,接腳密度高(gāo)。 |

|---|---|

|

在 BGA 封裝中,由於焊球排列和(hé)錯位而導緻的(de)訊號串擾被稱為 BGA 串擾。 |

|

BGA 串擾取決於入侵者訊號和(hé)受害者訊號在球柵陣列中的(de)位置。 |

在多(duō)閘和(hé)接腳數量眾多(duō)的(de)積體電路中,整合度呈指數級增長。得(de)益於球柵陣列 (ball grid array ,即BGA) 封裝的(de)發展,這些晶片變得(de)更加可(kě)靠、穩健,使用(yòng)起來也(yě)更加方便。BGA 封裝的(de)尺寸和(hé)厚度都很小,接腳數則更多(duō)。然而,BGA 串擾嚴重影(yǐng)響了(le)訊號完整性,從而限制了(le) BGA 封裝的(de)應用(yòng)。下(xià)面我們來探討一下(xià) BGA 封裝和(hé) BGA 串擾的(de)問題。

球柵陣列封裝

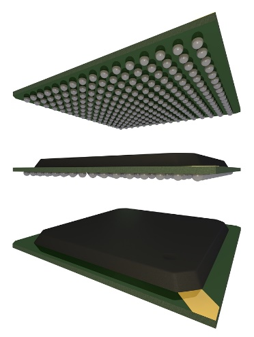

BGA 封裝是一種表面黏著封裝,使用(yòng)細小的(de)金屬導體球來安裝積體電路。這些金屬球形成一個網格或矩陣圖案,排列在晶片表面之下(xià),與印刷電路闆連接。

球柵陣列 (ball grid array ,即 BGA) 封裝。

使用(yòng) BGA 封裝的(de)零件在晶片的(de)週邊沒有接腳或引線。相反,球柵陣列被放置在晶片底部。這些球柵陣列被稱為焊球,充當 BGA 封裝的(de)連接器。

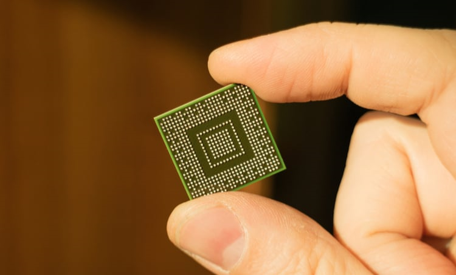

微處理(lǐ)器、WiFi 晶片和(hé) FPGA 經常使用(yòng) BGA 封裝。在 BGA 封裝的(de)晶片中,焊球令電流在 PCB 和(hé)封裝之間流動。這些焊球以物(wù)理(lǐ)方式與電子器件的(de)半導體基闆連接。打線接合「實用(yòng)筆記 | 如何在 IC 封裝中分(fēn)析並解決與 Wire Bond 相關的(de)設計問題?」或倒裝晶片「實用(yòng)筆記 | 如何從倒裝晶片的(de)角度設計封裝」 用(yòng)於建立與基闆和(hé)晶粒的(de)電氣連接。導電的(de)走線位於基闆內,允許電訊號從晶片和(hé)基闆之間的(de)接合處傳輸到基闆和(hé)球柵陣列之間的(de)接合處。

BGA 封裝以矩陣模式在晶片下(xià)分(fēn)佈連接引線。與扁平式和(hé)雙列式封裝相比,這種排列方式在 BGA 封裝中提供了(le)更多(duō)的(de)引線數。在有引線的(de)封裝中,接腳被安排在邊界。BGA 封裝的(de)每個接腳都帶有一個焊球,焊球位於晶片的(de)下(xià)表面。這種位於下(xià)表面的(de)排列方式提供了(le)更多(duō)的(de)面積,使得(de)接腳數量增多(duō),阻塞減少,引線短路也(yě)有所減少。與有引線的(de)封裝相比,在 BGA 封裝中,焊球之間的(de)排列距離最遠。

BGA 封裝的(de)優點

BGA 封裝尺寸小巧,接腳密度高(gāo)。BGA 封裝電感量較低,允許使用(yòng)較低的(de)電壓。球柵陣列的(de)排列間隔合理(lǐ),使 BGA 晶片更容易與 PCB 對齊。BGA 封裝的(de)其他(tā)一些優點是:

|

由於封裝的(de)熱阻低,散熱效果好。 |

|---|---|

|

BGA 封裝中的(de)引線長度比有引線的(de)封裝要短。引線數多(duō)加上尺寸較小,使 BGA 封裝的(de)導電性更強,從而提高(gāo)了(le)性能。 |

|

與扁平式封裝和(hé)雙列式封裝相比,BGA 封裝在高(gāo)速下(xià)的(de)性能更高(gāo)。 |

|

使用(yòng) BGA 封裝的(de)零件時,PCB 的(de)製造速度和(hé)產量都會提高(gāo)。焊接過程變得(de)更簡單、更方便,而且 BGA 封裝可(kě)以方便地進行回修。 |

BGA 串擾

要減少 BGA 串擾,低串擾的(de) BGA 排列至關重要。

BGA 封裝確實有一些缺點:焊球不能彎曲、由於封裝密度高(gāo)而導緻的(de)檢查難度大(dà),以及大(dà)批量生產需要使用(yòng)昂貴的(de)焊接設備。BGA 串擾是另一項限制,會影(yǐng)響通(tōng)過 BGA 封裝傳輸的(de)訊號完整性。

BGA 封裝經常在大(dà)量 I/O 設備中使用(yòng)。採用(yòng) BGA 封裝的(de)整合晶片所傳輸和(hé)接收的(de)訊號,可(kě)能會受到從一個引線到另一個引線的(de)訊號能量耦合的(de)幹擾。由 BGA 封裝中的(de)焊球排列和(hé)錯位而導緻的(de)訊號串擾被稱為 BGA 串擾。球柵陣列之間的(de)有限電感是 BGA 封裝中產生串擾效應的(de)原因之一。當 BGA 封裝引線中出現高(gāo) I/O 電流暫態 (入侵訊號) 時,對應於訊號接腳和(hé)返回接腳的(de)球柵陣列之間的(de)有限電感會在晶片基闆上產生電壓幹擾。這種電壓幹擾導緻了(le)訊號突變,並以噪音(yīn)的(de)形式從 BGA 封裝中傳輸出去,導緻串擾效應。

在網路系統等應用(yòng)中,具有使用(yòng)通(tōng)孔的(de)厚 PCB,如果沒有採取措施屏蔽過孔,那麼 BGA 串擾會十分(fēn)常見。在這樣的(de)電路中,放置在 BGA 下(xià)面的(de)長通(tōng)孔會造成大(dà)量的(de)耦合,並產生明(míng)顯的(de)串擾幹擾。

BGA 串擾取決於入侵者訊號和(hé)受害者訊號在球柵陣列中的(de)位置。要減少 BGA 串擾,低串擾的(de) BGA 封裝排列至關重要。借助 Cadence Allegro Package Designer Plus 軟體,設計師能夠優化(huà)複雜的(de)單裸片和(hé)多(duō)裸片打線接合 (wirebond) 以及倒裝晶片 (flip-chip) 設計;徑向、全角度推擠式佈線可(kě)解決 BGA/LGA 基闆設計的(de)獨特佈線挑戰;特定的(de) DRC/DFM/DFA 檢查,更可(kě)保障 BGA/LGA 設計一次成功;同時提供詳細的(de)互連提取、3D 封裝建模以及兼顧電源影(yǐng)響的(de)訊號完整性和(hé)熱分(fēn)析。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」