移動資料的(de)迅速攀升、蓬勃發展的(de)人(rén)工智慧及機器學習 (AI / ML) 應用(yòng),以及 5G 通(tōng)訊對頻寬前所未有的(de)需求,導緻對現有雲資料中心的(de)伺服器、存儲和(hé)網路架構形成了(le)巨大(dà)壓力。這些頗具挑戰性的(de)應用(yòng)需要高(gāo) I / O 頻寬和(hé)低延遲通(tōng)訊的(de)支援。112G SerDes 技術具有卓越的(de)長距性能、優秀的(de)設計裕度、優化(huà)的(de)功耗和(hé)面積,是下(xià)一代雲網路、AI / ML 和(hé) 5G 無線應用(yòng)的(de)理(lǐ)想選擇。由於更小的(de) UI 和(hé)更低的(de) SNR,在採用(yòng) 112G 資料速率的(de)過程中會遇到更大(dà)的(de)挑戰。解決這一問題需要綜合考慮 RX / TX 規範、串擾、抖動、碼間幹擾 (ISI) 和(hé)雜訊等多(duō)種因素,IEEE 標準也(yě)推出了(le)通(tōng)道運行裕度 (COM) 和(hé)有效回波損耗 (ERL) 作為測量標準,用(yòng)於檢查高(gāo)速串列系統的(de)交互操作裕度。

體現到訊號完整性工程師的(de)實際工作中,一項重要內容就是要分(fēn)析和(hé)優化(huà)無源鏈路中的(de)阻抗連續性和(hé)不同訊號之間的(de)串擾。封裝基闆上的(de) Core 層過孔 (Via) 和(hé) BGA 焊盤 (Pad) 區域,是封裝上影(yǐng)響最大(dà)的(de)阻抗不連續段,同時,這個區域因為有比較長的(de)過孔縱向耦合,也(yě)是最容易導緻串擾的(de)地方,是我們需要重點優化(huà)的(de)。本文我們將聚焦封裝 Core 層過孔的(de)阻抗連續性優化(huà)。

封裝過孔區域的(de)阻抗特性分(fēn)析

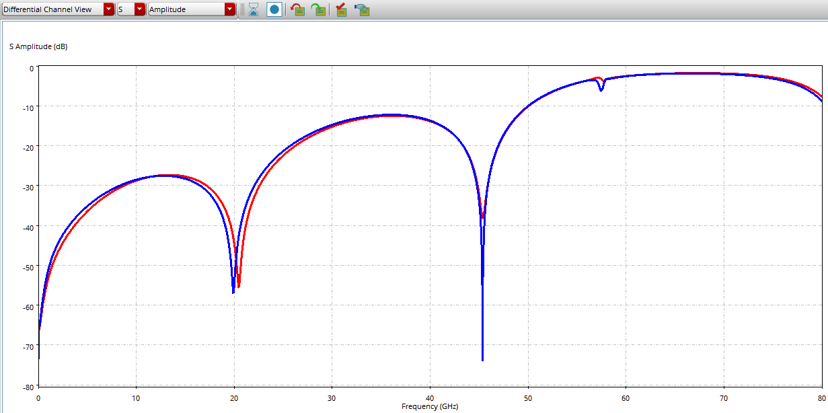

下(xià)圖是一個典型的(de)封裝 Core 過孔和(hé) BGA 焊盤區域的(de)差分(fēn)回波損耗結果。在奈奎斯特頻率以下(xià)的(de)差模-差模回損都已基本控制到 -20dB 以下(xià)。

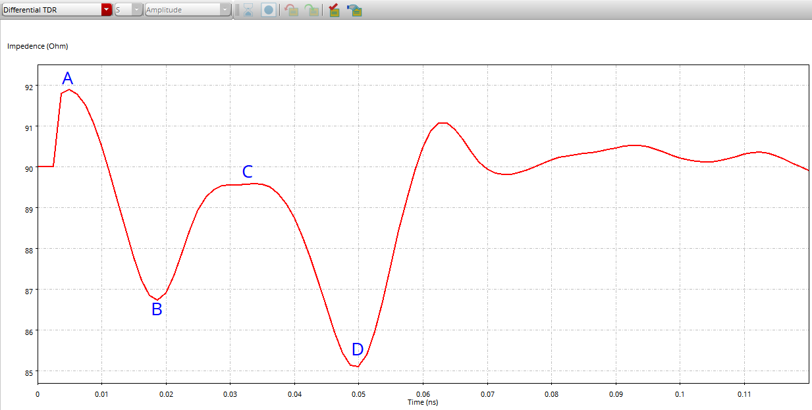

我們再看下(xià)其對應的(de) TDR 結果。可(kě)以看到實際阻抗並不是很靠近目標值 90 歐姆的(de)一條直線,而是存在多(duō)個阻抗不連續點。

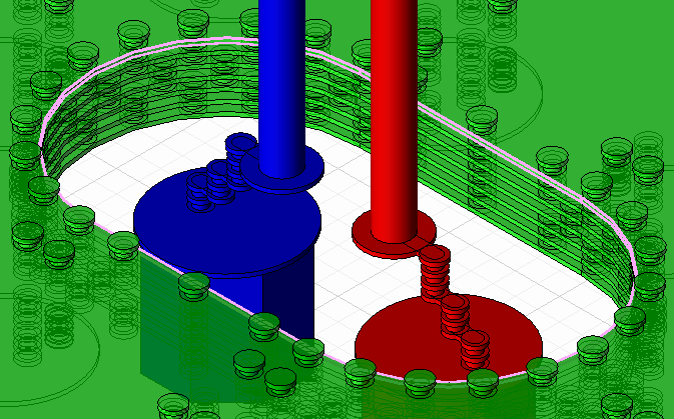

我們可(kě)以結合 Layout 結構來理(lǐ)解其中的(de)各段阻抗變化(huà)。首先看下(xià)阻抗最低的(de) D 點,這個地方對應的(de)是 BGA 焊盤區域。一般要控制差分(fēn)阻抗 90 歐,差分(fēn)走線的(de)線寬在 25-30um 左右,而 BGA 焊盤的(de)直徑會有 500-600um,所以這裡最容易出現阻抗偏低的(de)情況,需要把相鄰的(de)幾層平面挖空。

另外一個阻抗較低的(de) B 點是 Core 層過孔的(de)焊盤位置。這個焊盤的(de)直徑一般是 250-350um,也(yě)是比走線線寬高(gāo)了(le)一個數量級,所以這裡也(yě)要對相鄰幾層的(de)平面做(zuò)挖空處理(lǐ)。

C 點區域是 Core 過孔的(de)筒身部分(fēn)。這部分(fēn)會根據不同的(de)筒身高(gāo)度 (Core層厚度) 、相鄰層挖空大(dà)小 / 層數、周圍回流地孔的(de)距離 / 數量等體現出容性或者感性。

最開始的(de)阻抗較大(dà)的(de) A 點是走線在回流平面挖空區域部分(fēn)。這個地方因為相鄰層都挖空掉,按照(zhào)差分(fēn)線寬量級的(de)寬度佈線,就會出現實際阻抗比目標值高(gāo)的(de)情況。

封裝過孔分(fēn)析案例自動化(huà)建模

如上所述,封裝 Core 層過孔和(hé) BGA 焊盤區域的(de)多(duō)個佈線參數都會影(yǐng)響這段鏈路的(de)阻抗連續性,而且鏈路上不同組件對這些參數的(de)調整方向需求有的(de)還相互衝突,需要綜合權衡。這麼多(duō)參數需要調整,不可(kě)能把所有的(de)組合都先在封裝工具中設計出來再逐一用(yòng)模擬工具提取模型進行分(fēn)析。比較常見的(de)做(zuò)法是由資深的(de) SI 工程師根據經驗判斷最關鍵的(de)參數和(hé)大(dà)緻的(de)取值範圍,請封裝設計工程師做(zuò)幾種不同的(de)場景,然後在這基礎上把各層挖空大(dà)小做(zuò)成變數進行掃描,或者根據模擬結果手動反覆運算(suàn)調整參數。但是,這種做(zuò)法存在很多(duō)限制:首先是嚴重依賴資深工程師的(de)經驗;其次是受項目交付週期限制,實際能覆蓋到的(de)參數組合和(hé)調整範圍空間都比較有限;最後,如果出線層、疊層、材料、管腳排布、訊號速率等發生變化(huà),這些參數調整的(de)結論不能直接複用(yòng),重新建模分(fēn)析又非常消耗時間。

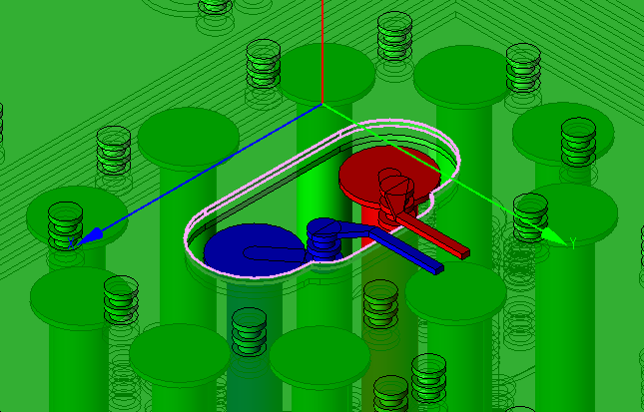

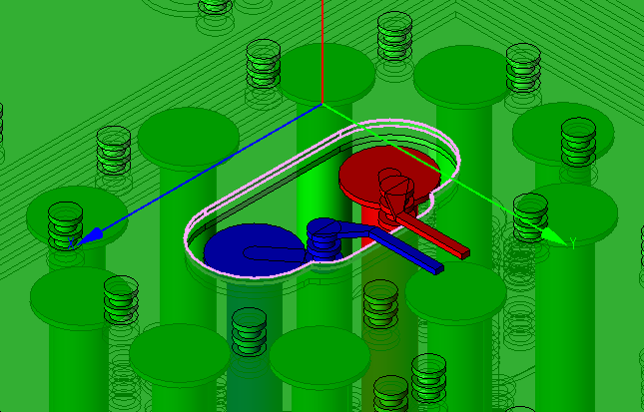

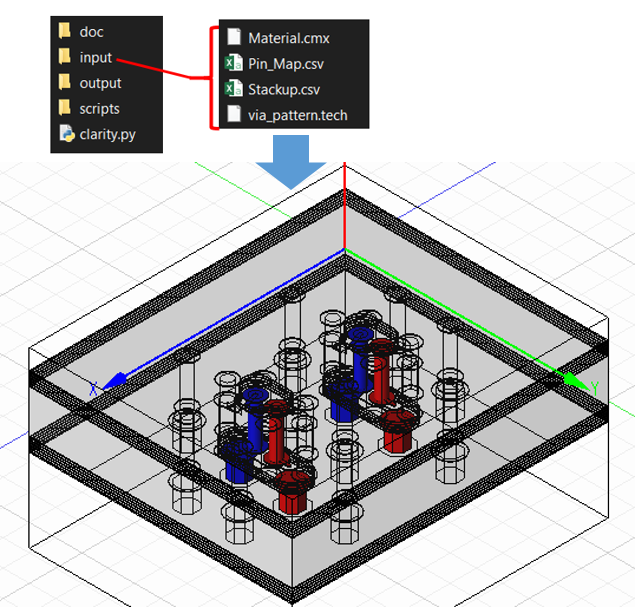

筆者的(de)做(zuò)法是利用(yòng)模擬工具強大(dà)的(de)參數運算(suàn)式功能,編寫 Python 腳本,讀入 PadStack、疊層材料、Pin Map 等資訊,自動創建封裝過孔優化(huà)工程,把上述各種參數,包括過孔間距、挖空區域大(dà)小、挖空層數、回流過孔方式、回流過孔距離、挖空區域走線線寬等,都在模型中做(zuò)成可(kě)掃描的(de)參數。這樣,調整參數時隻要在模擬工具中修改數值,整個模擬結構也(yě)會跟著改動,不需要返回封裝設計工具進行調整,更加方便快(kuài)捷。而且,不管疊層、材料、管腳排布等如何變化(huà),隻要簡單修改輸入設定檔,十分(fēn)鐘就能完成新的(de)模擬工程建模。

設計參數自動化(huà) / 智慧化(huà)調整

完成模擬工程建模後,下(xià)一步就是要調整設計樣式的(de)選擇和(hé)各設計參數的(de)取值,以優化(huà)阻抗連續性和(hé)串擾大(dà)小。這裡會遇到一個問題,就是由於參數數量多(duō),每個參數還有各自的(de)取值範圍,即便 SI 工程師根據經驗固定某些參數的(de)數值或者綁定不同參數同步變化(huà)進行簡化(huà),各參數排列組合後的(de)取值空間很可(kě)能依然是巨大(dà)的(de)。以 5 個獨立變數,每個變數 10 個掃描數值來計算(suàn),排列組合的(de)取值空間就達到 10^5 = 100,000 個,這個數量級根本不可(kě)能在實際項目交付過程中去遍歷。即使是每個變數隻有 5 個掃描數值,排列組合的(de)取值空間也(yě)達到 5^5 = 3125 個,很難遍歷完成。因此,一般的(de)做(zuò)法還是需要 SI 工程師手動進行「調整參數」->「模擬」->「分(fēn)析結果」->「調整參數」->「模擬」的(de)反覆運算(suàn),受到項目交付週期和(hé)有效模擬 / 分(fēn)析時間的(de)限制,實際能完成的(de)反覆運算(suàn)次數非常有限,通(tōng)常都不見得(de)能找到最優解。

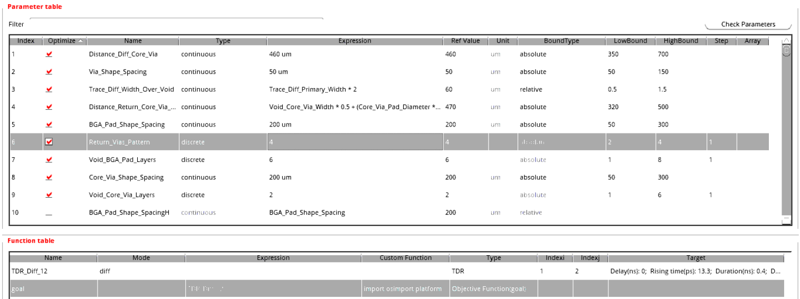

隨著模擬工具的(de)發展,現在調參這個難題可(kě)以交給 AI 引擎來自動實現。這裡我們利用(yòng) Cadence 最新推出的(de) Optimality Intelligent System Explorer 智慧優化(huà)引擎來完成封裝過孔優化(huà)。在 Cadence Clarity 3D Solver 模擬工具中打開透過腳本創建出來的(de)模擬工程,透過功能表列命令打開 Optimality Explorer 優化(huà)引擎,接下(xià)來隻需要設置好需要調整哪些參數、每個參數的(de)取值範圍,然後定義好我們要優化(huà)的(de)目標、設置並行跑的(de)任務數量和(hé)模擬伺服器資源,剩下(xià)的(de)就是等 Optimality Explorer 根據機器學習演算(suàn)法自動完成「調整參數」->「模擬」->「分(fēn)析結果」->「調整參數」->「模擬」的(de)反覆運算(suàn),最終得(de)到我們想要的(de)優化(huà)結果了(le)。

值得(de)一提的(de)是,Optimality Explorer 除了(le)官方給出的(de)一些常用(yòng)的(de)插損、回損、串擾、TDR 等優化(huà)目標,還支援 Python 介面,可(kě)以用(yòng) Python 自訂任意的(de)目標函數,比如本例我們用(yòng)了(le)自訂的(de) TDR 指標作為優化(huà)目標,綜合考慮了(le) TDR 結果中的(de)阻抗偏差最大(dà)值、阻抗偏差峰峰值、偏差阻抗長度等指標。

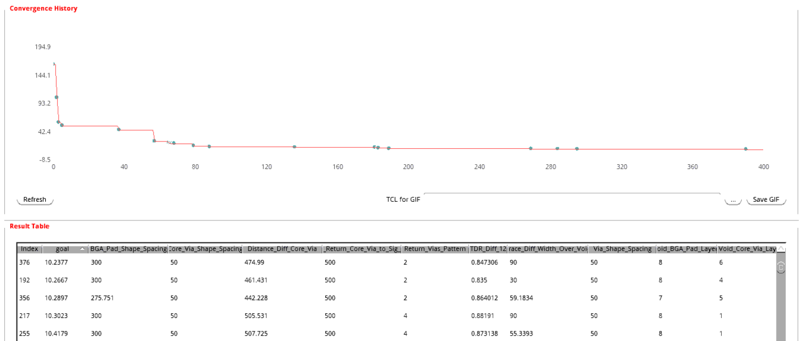

Optimality Explorer 的(de)收斂曲線如下(xià)。經過幾十次反覆運算(suàn)後,得(de)到的(de)模擬結果 TDR 指標就已經優於工程師手動反覆運算(suàn)的(de)結果。因為是工具自動調參,不需要工程師幹預,我們可(kě)以按原定設置最大(dà)反覆運算(suàn)次數繼續進行優化(huà),進一步得(de)到更優化(huà)的(de)結果。

如欲了(le)解更多(duō) Optimality Explorer 與 Clarity 3D Solver 產品詳情和(hé)案例應用(yòng),歡迎索取由 Cadence 台灣官方代理(lǐ)商-映陽科技所撰寫的(de)【技術指南(nán) | 如何在 Clarity 使用(yòng) Optimality Explorer AI 技術進行最佳化(huà)分(fēn)析 】查看。

本文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」