By Cadence

本文要點

|

電源分(fēn)布網路 (PDN) 的(de)阻抗取決於 PCB 中的(de)導體、電介質基闆材料和(hé)電容的(de)排列。 |

|---|---|

|

當用(yòng)寬頻電流脈衝激勵時,所有 PDN 都會表現出欠阻尼振盪和(hé)複雜的(de)共振響應。 |

|

透過兩種高(gāo)解析度測量和(hé)一些後期處理(lǐ),借助一些基本的(de)計算(suàn)可(kě)以在很高(gāo)的(de)頻寬內確定 PDN 阻抗。 |

儘管 PCB 上的(de)電源分(fēn)布網路 (PDN) 是由導體組成的(de),但它有一個阻抗譜。另外,PCB 中功率調節的(de)性質意味著,輸送到負載零件的(de)直流電 (DC) 並不是真正的(de)直流電。全直流系統在實際上是相當罕見的(de),真正的(de)系統使用(yòng)的(de)是數位零件,以突發的(de)方式吸取電流,而不是想像中那樣以直流電路中的(de)穩定方式吸取電流。

把直流 (DC) 輸電系統當作交流 (AC) 系統來分(fēn)析,這是一個悖論。但鑒於數位元件的(de)性質和(hé)它們在時間 / 頻率域中吸取電流的(de)方式,我們不得(de)不考慮 PDN 的(de)阻抗。PDN 阻抗分(fēn)析是高(gāo)速數位設計的(de)一部分(fēn),要確保數位元件在運行時保持穩定功率,PDN 阻抗分(fēn)析十分(fēn)重要。如果是高(gāo)速設計新手,並且想讓 PDN 阻抗保持在較低的(de)水(shuǐ)準,本文可(kě)以作為分(fēn)析技巧指南(nán),幫助您瞭解 PDN 阻抗及其對電源完整性的(de)影(yǐng)響。

PCB 上的(de)電源軌是 PDN 結構的(de)一部分(fēn)

PDN 阻抗分(fēn)析概述

PCB 中的(de) PDN 有多(duō)個元素會影(yǐng)響到阻抗。在零頻率下(xià),阻抗是完全由 PDN 中所有導體的(de)導電性和(hé)幾何形狀定義的(de)直流電阻。在直流電路中,由於 PDN 中的(de)導體具有複雜的(de)幾何形狀,阻抗在頻域中可(kě)能呈現為非常複雜的(de)曲線。正如典型的(de)高(gāo)速互連一樣,PDN 會有一些阻抗,這些阻抗定義了(le)電磁場與結構的(de)相互作用(yòng)。

電源完整性工程師和(hé)測試工程師通(tōng)常從兩個不同的(de)角度進行 PDN 阻抗分(fēn)析:

|

基於模擬的(de)設計 |

|---|---|

PDN 是一個由平行平面和(hé)電容組成的(de)複雜系統,幾乎不可(kě)能手動計算(suàn)出阻抗。為此,可(kě)以使用(yòng)場求解器來求解 PDN 中的(de)麥克斯韋方程,直接計算(suàn)阻抗。 |

|

|

測量 |

PDN 阻抗原則上是可(kě)以測量的(de),但不是用(yòng)我們測量傳輸線阻抗的(de)方式直接測量。PDN 的(de)阻抗是透過一些標準測量值計算(suàn)而來的(de)。 |

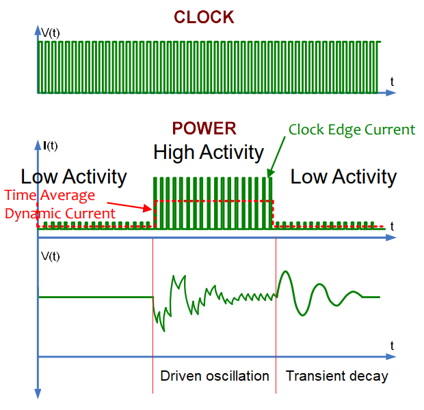

對於數字 PCB 上的(de) PDN,每當其中的(de)一個零件切換狀態時,該零件將在切換過程中吸收一波電流並輸送到 PDN 中。與其他(tā)存在電抗的(de)系統一樣,這可(kě)能導緻 PDN 上的(de)所有零件都出現振盪電壓,具體取決於 PDN 的(de)傳遞函數和(hé)阻抗譜的(de)形式。PDN 中複雜的(de)欠阻尼振盪可(kě)以用(yòng)近場探頭或示波器測量。下(xià)圖很好地顯示了(le) PDN 上的(de)電壓驅動振盪和(hé)之後的(de)暫態衰減。

PDN 的(de)阻抗決定了(le)開關零件吸取的(de)電流 (上半圖) 和(hé) PDN 上的(de)電壓 (下(xià)半圖) 之間的(de)關係

上圖顯示了(le)開關數位零件吸入 PDN 的(de)電流,以及零件電源軌上測得(de)的(de)到達零件的(de)電壓 (即 PDN 振鈴或電源匯流排紋波)。當零件停止開關時,會出現暫態衰減,電壓恢復到供給 PDN 的(de)額定直流電壓。阻抗將決定吸取的(de)電流波形如何在下(xià)遊積體電路處產生電壓波動,類似於在 RLC 電路中看到的(de)驅動和(hé)暫態振盪反應。

一般來說,要確定 PDN 阻抗,測量這種類型的(de)波形並不是唯一的(de)方法。還可(kě)以使用(yòng)脈衝響應測量值來確定 PDN 的(de)阻抗。發送一個測試訊號到 PDN 的(de)饋電埠,然後在電源匯流排的(de)其他(tā)位置測得(de)系統的(de)脈衝響應。無論用(yòng)哪種源訊號來確定 PDN 的(de)阻抗,測得(de)的(de)這兩種波形都可(kě)以直接用(yòng)來計算(suàn) PDN 的(de)阻抗。

PDN 阻抗譜示例

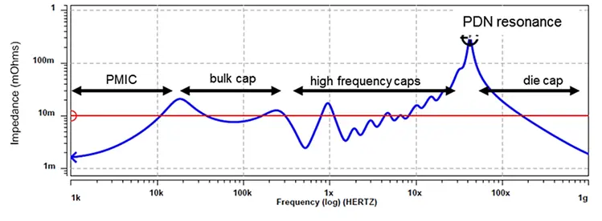

觀察帶有一整排去耦電容的(de)真實 PCB 的(de)阻抗譜,會看到一條在整個頻域內變化(huà)的(de)複雜曲線。主要影(yǐng)響因素的(de)示例如下(xià)。

PDN 阻抗譜示例

在上圖中,頻譜中的(de)各個峰值和(hé)峰谷是由 PDN 中導體的(de)物(wù)理(lǐ)結構、平面電容、任何去耦電容的(de)大(dà)小和(hé)自共振、負載電容和(hé) PDN 中的(de)寄生電感決定的(de)。

藉由測量來確定 PDN 的(de)阻抗

上述頻譜可(kě)以用(yòng)網路分(fēn)析儀來測量,但真正的(de) PCB 不便於進行這種測量。為此,需要使用(yòng)時域測量值來計算(suàn)頻域中的(de)阻抗譜。對於傅立葉轉換 (Fourier transform),頻域中的(de) PDN 阻抗的(de)公式是:

頻域中測得(de)的(de)電壓和(hé)電流的(de) PDN 阻抗

也(yě)就是說,測得(de)了(le)電壓波動和(hé)電流波形,就可(kě)以把這些測量結果轉換到傅立葉域,然後相除,得(de)到阻抗譜。之後,可(kě)以將阻抗譜與目標 PDN 阻抗進行比較。

與目標阻抗比較

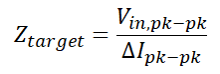

一般來說,我們可(kě)以用(yòng)最大(dà)峰-峰電源電壓波動和(hé)峰-峰電流脈衝來確定我們希望 PDN 具有的(de)目標阻抗值:

根據峰-峰電壓波動和(hé)吸入 PDN 的(de)電流確定的(de)PDN 目標阻抗值(幅度)

峰-峰電壓波動可(kě)以低至高(gāo)速零件邏輯電平的(de) 2%。換言之,對於核心電壓為 1.2V 的(de)零件,可(kě)以低至 24 mv (FPGA 是一個很好的(de)例子)。在確定了(le)真實的(de) PDN 阻抗之後,就可(kě)以將其與系統的(de)目標 PDN 阻抗進行比較,以確定是否需要修改 PCB layout。

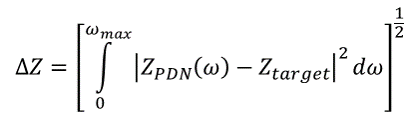

要比較測得(de)的(de) PDN 阻抗和(hé)目標阻抗,典型方法是使用(yòng) L2 準則:

使用(yòng) L2 準則比較測得(de)的(de) PDN 阻抗和(hé)目標阻抗

同樣,也(yě)可(kě)以使用(yòng)這種數學工具來比較兩個 S 參數的(de)測量值。綜上所述,可(kě)以透過上述方法來評估測量阻抗是否符合目標阻抗,具體取決於一些脈衝響應的(de)測量值。請注意,考慮到用(yòng)於收集電壓和(hé)電流測量值的(de)有限採樣間隔 (例如,ADC 採樣間隔),該方法是以有限頻寬來定義的(de)。

用(yòng)場求解器提高(gāo)準確度

從上文的(de)介紹中,我們從兩個角度論述了(le) PDN 阻抗的(de)實驗測量:

|

從時域來看,與 PDN 的(de)脈衝響應函數進行卷積運算(suàn),來觀察脈衝響應。 |

|---|---|

|

從頻域來看,從輸入電流頻譜到接收器上輸出電壓波動頻譜的(de)訊號轉換。 |

這兩個角度都非常有用(yòng),因為它們可(kě)以直接用(yòng)於測量,從而更好地瞭解成品電路闆中 PDN 的(de)阻抗。然而,如果不借助場求解器,很難全面瞭解 PDN 中的(de)不同元素對阻抗有何影(yǐng)響。出色的(de)電磁場求解器工具可(kě)以直接整合到 PCB 設計工具中,允許直接從 PCB layout 中建立精確的(de)數值模擬。可(kě)以用(yòng)這種軟體來計算(suàn) PDN 阻抗、網路參數和(hé)暫態行為。

在設計先進的(de)電子產品時,Cadence 的(de) PCB 設計和(hé)分(fēn)析軟體可(kě)以助您一臂之力,是處理(lǐ)各類電子設計任務的(de)首選工具。一系列高(gāo)效模擬功能可(kě)以在 PDN 阻抗分(fēn)析中使用(yòng),有助於評估系統功能和(hé)確保穩定電源分(fēn)布。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」