By Chen Yun, Graser

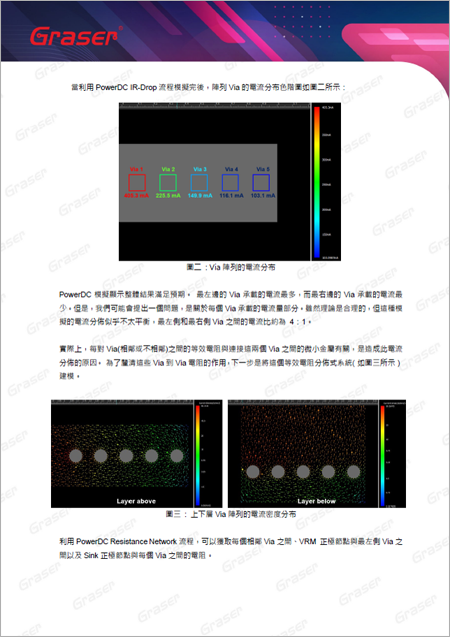

了(le)解 Via (貫孔) 陣列的(de)電流分(fēn)布是降低局部 DC (直流)電流的(de)關鍵步驟,PI (電源完整性) 工程師通(tōng)常會在設計中遇到電流熱點集中的(de)問題,因此必須找到方法來降低局部的(de) DC 電流值。

而一個常見的(de)電流分(fēn)布問題就是來自於 Via 陣列。

本指南(nán)為 PDF 版本,共 8 頁,將說明(míng)如何利用(yòng) PowerDC 分(fēn)析 Via 陣列的(de)電流分(fēn)布,並與 Via 陣列的(de)萃取等效電阻模型模擬結果進行比對,以便能更好地了(le)解 Via 陣列的(de)直流分(fēn)布,以及透過兩案例解析也(yě)能更清楚知道為何 Via 之間的(de)微小金屬電阻容易導緻電流分(fēn)佈不平衡。

本書重點

|

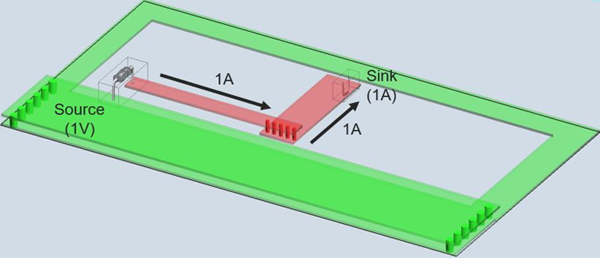

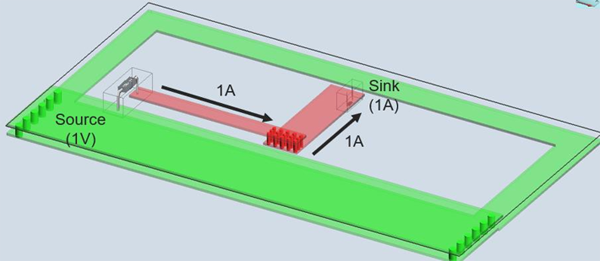

簡單案例解析:一行連續五個 Via 和(hé)一個固定的(de) 1A DC 電流 |

|---|

|

複雜案例解析:一個 5 x 3 的(de)陣列 Via 和(hé)一個固定的(de) 1A DC 電流 |

|---|

中文版授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」