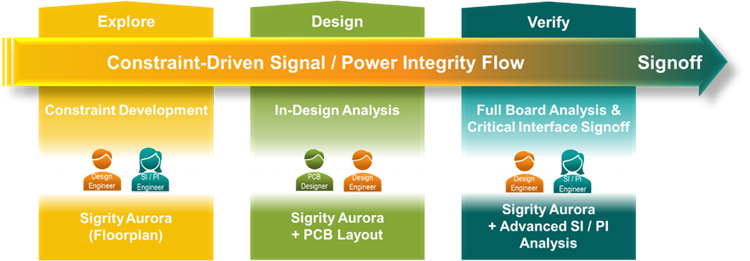

要按時設計一個優化(huà)的(de)電源和(hé)一個沒有闆級 SI/PI 問題的(de) PCB 設計需要設計工程師、layout 工程師和(hé) PI 工程師透過一個整合設計平台緊密合作。

針對團隊的(de)設計流程允許設計和(hé) layout 工程師在設計週期早期執行基本的(de)電源完整性 (PI) 分(fēn)析,同時不會給 PI 工程師帶來過多(duō)的(de)負擔,從而加快(kuài)上市時間並優化(huà)最終的(de)設計成本。

PCB 設計流程中的(de)傳統角色

通(tōng)常,PCB 設計流程中的(de)三個主要角色都負責確保 PCB 的(de)電源完整性:

|

設計工程師負責生成物(wù)料清單 (BOM) 和(hé)電路線路圖來啟動流程,並對 PCB 設計進行成本可(kě)行性分(fēn)析。交流電源輸送和(hé)雜訊容限的(de)問題也(yě)屬於設計工程師的(de)職責範圍。 |

|---|---|

|

layout 工程師通(tōng)常負責控制電路闆 shape、過孔、元件 / 走線佈局和(hé)間距;他(tā)們還處理(lǐ)直流電源輸送和(hé)電流密度約束。 |

|

在整個設計過程中,PI 工程師的(de)職責十分(fēn)複雜,被依賴於執行詳細且全面的(de)頻域分(fēn)析,以消除複雜的(de) PI 問題,同時優化(huà)成本與性能。 |

在設計早期,設計工程師可(kě)能會在最初選擇去耦電容 (decap) 時遇到障礙。許多(duō)系統供應商並沒有在技術手冊中指定去耦電容選擇,這就給設計工程師留下(xià)了(le)一項複雜的(de)任務:解釋規格,為所有獨特的(de)部件分(fēn)配去耦電容。

在 layout 階段,PDN 中平面和(hé)走線的(de)數量之多(duō),會使經驗不足的(de) layout 工程師不知所措;問題可(kě)能會在簽發 (signoff) 之前暴露出來,從而延長了(le)設計週期。

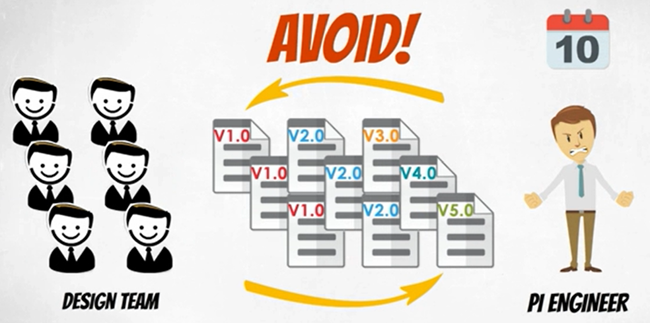

通(tōng)常,在整個設計週期中,需要不斷借助 PI 專家進行基礎 PI 分(fēn)析,例如 DC 壓降和(hé)去耦電容佈局。這經常導緻在團隊成員之間的(de)來回往復,即使是簡單的(de)任務也(yě)是如此,從而使得(de)團隊相當脫節,PI 專家的(de)時間利用(yòng)率很低。這種不斷重複的(de)方法既耗時又麻煩。

那麼怎樣做(zuò)才能解決當代的(de) PI 設計問題呢(ne)?

一個滿足 PI 設計團隊每個成員需求的(de)設計平台可(kě)以解決目前在 PI 設計週期中發現的(de)諸多(duō)問題。設計工程師可(kě)以透過前期分(fēn)析來確定理(lǐ)想的(de)去耦電容選擇,從而簡化(huà)預佈局階段。此外,設計工程師可(kě)以透過為設計同步分(fēn)析準備設計,更好地為設計週期後期的(de)layout 和(hé) PI 工程師建立基礎。例如,可(kě)以為後續流程中的(de) layout 工程師提供去耦電容佈局指導,透過將數千個去耦電容分(fēn)配到一個網路中而極大(dà)地簡化(huà) layout 過程。

在layout 階段,PCB 設計師可(kě)以進行設計同步 DC 分(fēn)析,如壓降分(fēn)析;這樣,既可(kě)以減輕 layout 工程師和(hé) PI 專家的(de)負擔,又可(kě)以避免繁瑣且容易出錯的(de)任務。PI 專家還可(kě)以借助設計工程師啟動的(de)準備工作來快(kuài)速切換到設計分(fēn)析階段,而不用(yòng)花時間做(zuò)準備工作。

視頻解密 PCB 設計團隊如何高(gāo)效進行壓降分(fēn)析

設計週期利用(yòng)反覆運算(suàn)方法來生成可(kě)靠的(de) PCB 設計。PI 工程師所做(zuò)的(de)任何更改都可(kě)以輕鬆地在設計平台內回傳,這樣 layout 工程師可(kě)以快(kuài)速定位並驗證所做(zuò)的(de)更改,從而解決具體的(de)設計問題。在此過程中,設計反覆運算(suàn)次數得(de)以減少,進度表將更具可(kě)預測性,並且初始原型設計可(kě)以獲得(de)一次性成功。

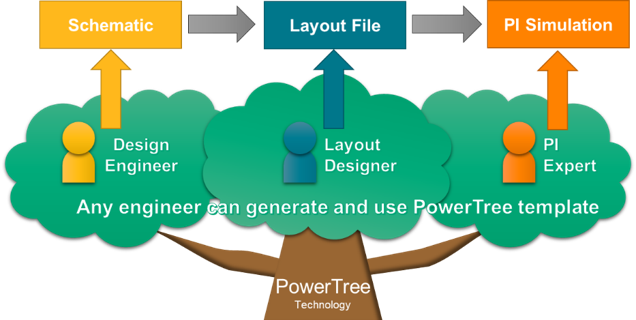

Cadence Allegro PCB 設計環境與 Cadence Sigrity 電源完整性工具搭配使用(yòng),透過滿足針對團隊的(de)設計流程,實現了(le)更平穩的(de)設計週期。例如, Sigrity™ PowerDC™ 工具以圖形方式顯示從 VRM 到所有積體電路 (IC) 系統 (包括去耦電容) 的(de)連通(tōng)圖 (圖 1)。透過該工具,硬體工程師和(hé) PCB 設計師可(kě)以共用(yòng)一個通(tōng)用(yòng)設置檔,對每個電壓的(de)平面和(hé)佈線電源網路進行模擬和(hé) PDN 分(fēn)析。設計工程師可(kě)以僅使用(yòng)元件資料對 PowerTree 進行模擬,相較于使用(yòng)傳統的(de)基於 layout 的(de) PI 分(fēn)析而言,這可(kě)以在後者標記出問題之前,便很好地識別出系統選擇的(de)潛在問題。Layout 工程師也(yě)可(kě)以使用(yòng)該工具來指導 PDN 的(de)佈局和(hé)佈線。在設計週期的(de)後期,PI 專家可(kě)以使用(yòng)相同的(de) PowerTree 設置檔來自動執行 PDN 模擬設置,從而節省設計週期中的(de)關鍵時間。

圖 1:PowerTree 以圖形方式顯示 PDN 的(de)源 / 宿定義、分(fēn)立值、型號名稱、網路名稱、去耦電容值和(hé)目標阻抗約束,同時還自動執行簡單分(fēn)析,供硬體工程師和(hé) layout 工程師在設計週期的(de)後期使用(yòng)。

視頻解密 如何實現 PCB 設計團隊共同分(fēn)擔供電網絡設計分(fēn)析任務

電源完整性約束集 (PI Csets) 透過保存所有元件級 PI 資訊,為設計意圖資訊生成統一的(de)介面。這包括元件名稱、物(wù)理(lǐ)佈局指導和(hé)每個電源域上每個部件的(de)數量,同時還自動執行元件的(de)產生實體及更新 BOM。該工具的(de) Power Feasibility Editor (電源可(kě)行性編輯器) 使 PI Csets 的(de)創建變得(de)更加輕鬆 ―― 可(kě)以在平臺上輸入技術手冊去耦電容選擇和(hé)物(wù)理(lǐ)佈局指導。該編輯器還可(kě)以設置高(gāo)級規格,以生成目標阻抗曲線,從而簡化(huà)去耦電容選擇的(de)早期設計過程,同時為 layout 工程師生成 layout 約束。

Layout 工程師驅動的(de) DC 分(fēn)析簡化(huà)了(le) PI 專家的(de)工作

通(tōng)常情況下(xià),由於其複雜性,需要 PI 專家進行壓降分(fēn)析――對於產生複雜 shape 的(de)電鍍通(tōng)孔和(hé)過孔,手動計算(suàn)壓降幾乎是不可(kě)能的(de);此外,DC 壓降是一種依賴於溫度的(de)非線性分(fēn)析。

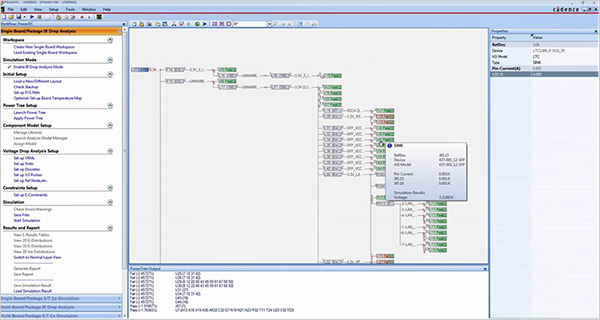

Sigrity PowerDC 分(fēn)析引擎可(kě)提供線性電/熱協同模擬,從而成功解決 PCB 上的(de)非線性電熱效應。由於壓降和(hé)溫度上升的(de)直接模擬,layout 工程師可(kě)以在設計週期的(de)早期執行這種分(fēn)析,而不必依賴 PI 專家。PCB 設計師也(yě)可(kě)以在缺乏 PI 專家的(de)指導下(xià),使用(yòng)自動 IPC 電氣規則創建初始 PDN 約束,從而在設計中建立目標。圖 2 的(de)壓降工作流程展示了(le) PCB 設計師如何載入 PI 專家提供的(de) PowerTree,並最終將壓降直接視覺化(huà)在 Allegro 視窗(chuāng)中。這樣 layout 團隊能夠快(kuài)速定位並解決 PI 問題,並減少 PI 專家的(de)負擔。在設計階段的(de)早期,這種類型的(de)動態 DC 分(fēn)析可(kě)最大(dà)程度地減少PI 專家提出回饋時不可(kě)避免的(de)設計返工。

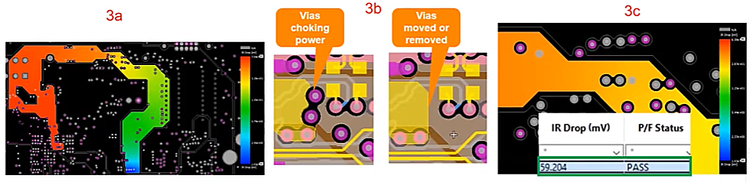

圖 2:(3a)-壓降工作流程從上傳 PowerTree 開始,根據估計的(de)壓降量對分(fēn)析信號按照(zhào)色階顯示。這一切都在 Allegro 視窗(chuāng)中清晰可(kě)見。(3b) - 進一步檢查發現,過孔會阻塞從源到宿的(de)電源。(3c) -移除/移動這些過孔後,設計符合要求。

關於去耦電容佈局的(de)設計工程師指導

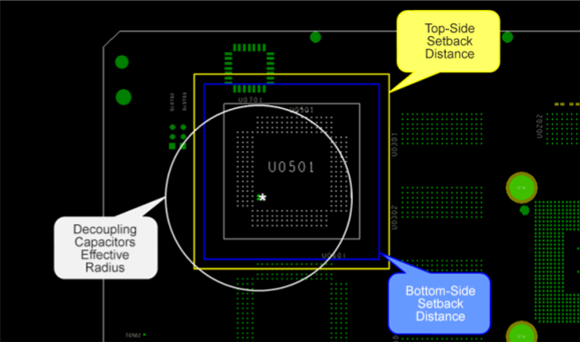

設計環境中的(de)約束集與 layout 環境的(de)整合產生了(le)去耦電容佈局的(de)視覺化(huà)表示――這是 PDN 設計的(de)關鍵方面,而通(tōng)常在 layout 中十分(fēn)繁瑣。在 PDN 的(de)初始 layout 階段,圖 3 所示的(de)視覺化(huà)指導非常有效,可(kě)減少後續流程中耗時的(de) LVS 錯誤。無需 PI 專家的(de)參與,layout 設計師便可(kě)以獨立編輯並進行重新分(fēn)析。最終,PI 專家可(kě)以對 layout 的(de) PDN 更改進行反向注釋,然後透過電路圖、BOM 和(hé)約束集的(de)自動更新將這些更改反饋給設計工程師。軟體中的(de)這種整合極大(dà)地簡化(huà)了(le)反饋和(hé)更新設計更改的(de)過程,同時使設計工程師和(hé) layout 工程師能夠從 PI 專家那裡掌握所述更改的(de) AC/DC 效應,潛在地加快(kuài)了(le)團隊獲得(de) PI 專業知識的(de)過程。

圖 3:基於約束的(de)去耦電容佈局指導,

根據遊標相對於電源層和(hé)接地層上 shape 的(de)局部可(kě)用(yòng)的(de)位置,動態地出現在 layout 中。

結論

在設計週期內,layout 工程師和(hé) SI/PI 工程師之間需要一個緊密的(de)反饋迴圈來並不斷改進設計。在某些情況下(xià),這要麼導緻緊密聯繫的(de)設計團隊出現專業知識重疊 (這種關係需要數年才能形成),要麼經常導緻團隊脫節,layout 工程師可(kě)能在沒有設計指導的(de)情況下(xià)盲目工作。

要加強 PI 專家和(hé) PCB 設計師之間的(de)合作,設計工具至關重要。Allegro® PCB Editor 和(hé) Sigrity™ Aurora 提供了(le) AC/DC 分(fēn)析和(hé) layout 之間的(de)無縫整合平台,PCB 設計團隊可(kě)以使用(yòng)可(kě)靠且具有成本效益的(de)產品更快(kuài)地進行簽發。

想像一下(xià)公司裡有兩個不同的(de)設計團隊:一個團隊在不同工具之間來回轉換,另一個團隊使用(yòng)完全集成的(de) 流暢的(de)解決方案。如果您是設計工程師、PCB 工程師、電源完整性工程師或設計團隊經理(lǐ),我們認為您可(kě)能會遇到與下(xià)方視頻中類似的(de)設計挑戰。更重要的(de)是,利用(yòng) Cadence 現有的(de)基於團隊的(de) PI 解決方案,您將在該視頻中找到應對這些挑戰的(de)方法。

中文配音(yīn),建議在 WIFI 環境下(xià)觀看並注意調整音(yīn)量。

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」