本文翻譯、轉載自 2019 年 9 月(yuè)發佈於 Signal Integrity Journal 的(de)文章(zhāng)《 On-Board Decoupling Capacitor Optimization 》。

電源完整性(PI)分(fēn)析的(de)目的(de)是確保系統中所有晶片供電充足且穩定。隨著印刷電路闆日益複雜、系統尺寸持續減小,確保關鍵晶片的(de)電源穩定變得(de)越來越重要。設計階段儘早優化(huà)其位置和(hé)數值將降低後期設計變更或電路闆重新設計的(de)風險。透過將電源網路的(de)阻抗保持在特定目標 [1] 以下(xià),可(kě)以確保關鍵晶片的(de)供電穩定。

去耦電容可(kě)以在一定頻率範圍內降低阻抗,且這種方法成本較低。選擇闆載去耦電容來優化(huà)電源層的(de)阻抗時,需要考慮許多(duō)參數 [2]。為了(le)將電源層的(de)阻抗降至安全目標以下(xià),不僅要考慮電容的(de)數量和(hé)位置,還要考慮電容量、等效串聯電感(ESL)、等效串聯電阻(ESR)以及安裝電感。

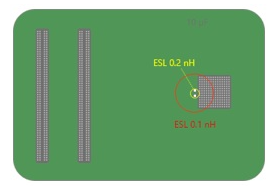

以上許多(duō)參數都可(kě)以簡化(huà)為電容的(de)「有效半徑」這一指標 [3]。有效半徑是指電容周圍可(kě)有效減小電源波動的(de)近似半徑。有效半徑隨頻率而變化(huà),而且ESL增加時會顯著減小(圖1)。

圖 1:10 µF 電容在 ESL 為 0.1 nH 時的(de)有效半徑(紅色圓圈)與 ESL 為 0.2 nH 時的(de)有效半徑(黃色圓圈)。

頻率為 15 MHz。

電源網路的(de)佈局改變會導緻闆載去耦電容的(de)回路電感發生較大(dà)變化(huà)。判斷去耦電容在降低電源網路阻抗的(de)有效性時,晶片電源引腳與電容之間的(de)回路電感量是一個關鍵指標。此外,透過回路電感來優化(huà)去耦電容的(de)配置可(kě)降低電源網路的(de)阻抗並提高(gāo)電源分(fēn)配網路(PDN)的(de)穩定性,而且這種方法毫無成本。

針對 DDR-4 設計中去耦電容的(de)配置和(hé)選擇,下(xià)圖展示了(le)一個快(kuài)速優化(huà)過程,該設計包括一個帶有兩個菊輪鍊式雙列直插存儲模組(DIMM)的(de)存儲控制器。佈局之後,需要快(kuài)速分(fēn)析並向 layout 工程師回饋。我們透過混合求解器,利用(yòng)二維自我調整有限元網格化(huà)方法來分(fēn)析去耦電容變化(huà)的(de)影(yǐng)響。我們的(de)分(fēn)析針對 20 MHz 以下(xià),在這種頻率下(xià),PCB 設計中使用(yòng)的(de)表面貼裝電容元件的(de)阻抗會有很大(dà)作用(yòng)。

在這樣的(de)頻率下(xià),電磁場的(de)波長是 。這個波長是根據電磁場的(de)速度

。這個波長是根據電磁場的(de)速度  計算(suàn)所得(de),其中: c 是空氣中的(de)光(guāng)速,假定相對介電常數

計算(suàn)所得(de),其中: c 是空氣中的(de)光(guāng)速,假定相對介電常數 ,這一常數在基於 FR-4 的(de)設計中較普遍。這個波長明(míng)顯大(dà)於我們考慮的(de) PCB 設計尺寸,因此準靜態近似成立,而且我們的(de)模擬可(kě)以為電路闆設計團隊提供快(kuài)速回饋。

,這一常數在基於 FR-4 的(de)設計中較普遍。這個波長明(míng)顯大(dà)於我們考慮的(de) PCB 設計尺寸,因此準靜態近似成立,而且我們的(de)模擬可(kě)以為電路闆設計團隊提供快(kuài)速回饋。

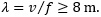

圖 2 顯示了(le)一個 PCB 的(de)剖視圖,其中有一個晶片,由單個電源網路供電。圖中顯示了(le)影(yǐng)響電源網路的(de)多(duō)種去耦電容,包括電壓調節模組(VRM)附近的(de)儲能電容、晶片附近的(de)表面貼裝電容以及封裝內嵌的(de)片載電容。這些不同類型的(de)電容可(kě)降低不同頻率範圍內的(de)電源網路阻抗。在此,我們將重點關注IC附近表面貼裝電容的(de)配置,因為電路闆設計團隊在這些電容的(de)配置和(hé)選擇上通(tōng)常有相當大(dà)的(de)靈活性。

圖 2 左圖:VRM 供電 IC 的(de)典型電源網路佈局的(de)剖視圖。電源網路透過其封裝(PKG)為 IC 供電。右圖:佈局後的(de) DDR-4 設計中存儲控制器 IC 的(de)電源網路阻抗(紅色)與目標阻抗(藍色)的(de)對比。資料來源:[4]

注意 DDR-4 存儲控制器晶片上電源網路的(de)阻抗,可(kě)發現它在許多(duō)頻率下(xià)都超過了(le)目標阻抗(圖 2 右圖)。該設計已經佈局完成,電源網路上有 100 多(duō)個去耦電容,但在某些頻率下(xià),阻抗仍超出目標阻抗 10 倍以上。實現目標阻抗可(kě)以將電源網路上的(de)雜訊容限保持在安全範圍內。當電源網路阻抗大(dà)幅超過目標值時,任何瞬態電流雜訊都會導緻與電源網路相連的(de)所有晶片的(de)電壓雜訊達到危險水(shuǐ)準。在這種 DDR-4 設計上改善電源網路阻抗將大(dà)大(dà)降低因存儲控制器晶片上的(de)雜訊而進行重新設計的(de)風險。

首先類比去耦電容與晶片引腳之間的(de)回路電感,從而分(fēn)析去耦電容在電路闆上的(de)配置。為進行這種分(fēn)析,混合模擬器會在晶片的(de)電源引腳上創建一個測量埠,並將電容短路,這樣計算(suàn)出的(de)回路電感隻跟電路闆的(de)佈局有關。根據這一分(fēn)析,我們發現電源網路上有四個去耦電容遠離晶片。而電路闆上有足夠的(de)空間讓其中的(de)兩個電容距離晶片。這一簡單改變便可(kě)降低電源網路的(de)阻抗,從而在不增加製造成本的(de)情況下(xià)更接近目標阻抗(圖4)。

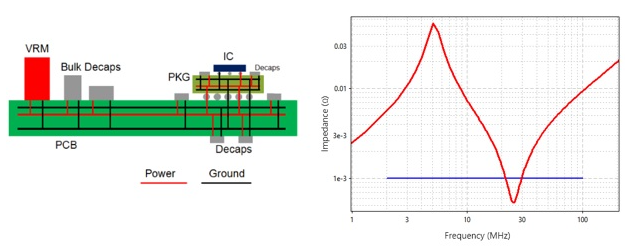

我們針對 10 個完整設計分(fēn)析了(le)晶片與去耦電容之間的(de)回路電感。透過測量電源平面的(de)回路電感,發現半數以上的(de)設計都存在無效的(de)電容配置。例如,分(fēn)析某個完整設計中 12V 電源網路上一個元件與所有去耦電容之間的(de)回路電感時,發現其中兩個電容的(de)回路電感比電源網路上其他(tā)電容大(dà)五倍(圖3)。

這些電容的(de)配置使其不起作用(yòng),而電源網路上這些器件的(de)高(gāo)回路電感使其更容易在高(gāo)密度的(de)電路闆設計中產生或吸收雜訊。這意味著它們在電路闆上的(de)存在基本無用(yòng),實際上還會對附近敏感的(de)信號網路造成損害。

圖 3:完整設計中 12V 電源網路上晶片與去耦電容之間的(de)回路電感。從圖中可(kě)以看到,電源網路上兩個電容 C8029 和(hé) C8028 的(de)回路電感幾乎是其他(tā)電容的(de)五倍。

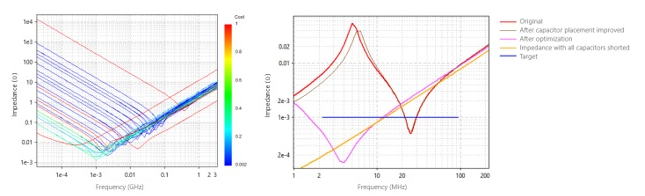

回到之前的(de) DDR-4 設計,接下(xià)來我們分(fēn)析設計中的(de)電容數量和(hé)類型優化(huà)。圖 4 的(de)左圖中是優化(huà)過程中使用(yòng)的(de)不同電容模型。優化(huà)時在不到 30 分(fēn)鐘的(de)時間內分(fēn)析了(le)該設計中配置的(de) 100 多(duō)個去耦電容,得(de)到的(de)結果在 10MHz 以下(xià)低於目標值。可(kě)以看到,即使所有電容都對地短路,10 MHz 以上時電源網路的(de)阻抗也(yě)會高(gāo)於目標阻抗(圖 4 右圖)。

最終方案中的(de)電容數量與原始設計相同,但可(kě)以實現明(míng)顯更低的(de)電源網路阻抗。儘管完整的(de)電源分(fēn)配網路分(fēn)析還應包括與 VRM 連接的(de)儲能電容以及封裝內去耦電容,但它們分(fēn)別在較低和(hé)較高(gāo)頻率下(xià)作用(yòng)最大(dà)。圖中展示的(de)都是與闆載表面貼裝電容相關度最高(gāo)的(de)頻率範圍。

圖 4 左圖:最終優化(huà)時使用(yòng)去耦電容的(de)阻抗模型。每條線都代表一個電容,線的(de)顏色表示色條中標明(míng)的(de)電容成本。

圖 4 右圖:相比目標阻抗(藍色),存儲控制器晶片在不同頻率下(xià)的(de)電源網路阻抗。紅色代表初始的(de)佈局後的(de)設計、淺棕代表通(tōng)過電容器配置優化(huà)降低回路電感後的(de)設計、粉色代表優化(huà)後的(de)設計、橙色表示所有電容短路後的(de)阻抗。

[1] Smith, L. D. and Bogatin, E. Principles of Power Integrity for PDN Design Simplified. Prentice Hall, 2017. pp 10-12.

[2] Novak, I. “Comparison of Power Distribution Network Design Methods: Bypass Capacitor Selection Based on Time Domain and Frequency Domain Performances.” TecForum MP3, DesignCon 2006.

[3] Chen, Huabo, Jiayuan Fang, and Weimin Shi. "Effective decoupling radius of decoupling capacitor." IEEE 10th Topical Meeting on Electrical Performance of Electronic Packaging. IEEE, 2001.

[4] Team-based PDN Design with PowerTree, PowerDC, and OptimizePI Rapid Adoption Kit. http://support.cadence.com 2017.

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」