當今電子產品的(de)設計中常常包含了(le)多(duō)個互連的(de)印刷電路闆(PCB)。要使多(duō)闆系統中的(de)所有元器件整合為一個的(de)成品工作,關鍵在於設計時選擇正確的(de)連接器。

在這篇文章(zhāng)中,我們將深入探討不同類型的(de) PCB 互連方式以及最佳實踐方式,以便在今後的(de) PCB 項目中進行實踐。

多(duō)闆 PCB 的(de)互連類型

無論想要創建互相堆疊的(de)垂直塔式 PCB 闆,還是需要將多(duō)個電路闆裝入機架後再放入伺服器,設計人(rén)員在連接器類型方面都有多(duō)種選擇。

|

標準電路闆互連: |

|---|---|

排針/排座(公/母)是最常見的(de)闆對闆連接器。這些互連設備價格低廉,在摸擬闆實驗和(hé) Arduino 套件中很常用(yòng)。 |

|

|

背闆連接器: |

典型的(de)背闆是沒有有源元件的(de) PCB。其主要目的(de)有兩個:保證多(duō)闆系統的(de)結構完整性,以及作為多(duō)個子闆連接的(de)表面。 |

|

|

卡緣連接器: |

卡緣連接器通(tōng)常用(yòng)作主機闆、背闆或擴展卡上的(de)擴充槽,適配其他(tā)闆的(de)闆邊導電走線(例如,PCI-e 插槽)。 |

圖片來源:知乎

|

線對闆: |

|---|---|

需要將電纜或電線連接到闆上時可(kě)選用(yòng)以下(xià)連接器:軟性薄膜電纜(FFC)、軟性印刷電纜(FPC)、高(gāo)速內部電纜互連和(hé)帶狀連接器。 |

|

|

直接焊接: |

將小型無線模組連接到更大(dà)的(de)電路闆上時,齒形孔是製造易於焊接到其他(tā)闆上的(de) PCB 模組的(de)常用(yòng)方法。請務必遵循焊接標準,如 IPC-A-610 或 J-STD-001。 |

多(duō)闆 PCB 互連設計考量

現在我們已經瞭解不同類型的(de) PCB 互連方式,接下(xià)來是實現多(duō)闆 PCB 設計時需要考慮的(de)通(tōng)用(yòng)設計技巧。

1. 電磁相容 / 電磁幹擾

對於單闆需要考慮的(de)串擾、阻抗和(hé)其他(tā)電磁幹擾因素也(yě)必須延伸到多(duō)闆系統。在開始將這些電路闆堆疊成 PCB 塔之前,需要考慮以下(xià)幾點:

|

注意共模模式。當差分(fēn)對的(de)兩根線長度不同時,這種差異會在共模下(xià)產生縱向訊號,使系統成為一根有效的(de)天線。 |

|---|---|

|

避免意外產生的(de)天線。在不可(kě)避免會產生天線的(de)情況下(xià),保持訊號和(hé)返回電流緊密耦合,從而減少輻射。總之,要使疊構中的(de)所有訊號層與一個不間斷的(de)參考平面緊密耦合。 |

|

使訊號保持分(fēn)離。類比(直流)電路和(hé)數位(交流)電路、高(gāo)速電路和(hé)低速電路應始終保持分(fēn)離,在多(duō)闆疊構中也(yě)是如此。注意哪些走線需要穿過電路闆。 |

請記住,將電路闆連接起來所採用(yòng)的(de)互連方式和(hé)過孔會改變系統的(de)整體訊號。

2. 腐蝕

腐蝕對連通(tōng)性構成直接風險。銅、鉛和(hé)電鍍錫極易受到腐蝕。另一方面,金、銀、石墨和(hé)銅鎳合金非常耐腐蝕。瞭解導緻腐蝕的(de)環境有助於在選擇連接器和(hé)元器件的(de)用(yòng)料類型時做(zuò)出明(míng)智的(de)決定:

|

空氣: |

|---|---|

當金屬接觸到氧氣和(hé)水(shuǐ)時,會發生氧化(huà)。空氣中的(de)水(shuǐ)分(fēn)即可(kě)導緻銅觸點腐蝕,從而降低導電性。 |

|

|

微動磨損: |

眾所周知,活動部件的(de)頻繁磨損,例如錫焊開關中的(de)擦拭動作,會因去除表面氧化(huà)層並使下(xià)面的(de)材料氧化(huà)而導緻腐蝕。 |

|

|

電解: |

異種金屬採用(yòng)同一標準(MIL-STD-889)是有原因的(de)。當電解液(例如,來自電池的(de)電解液)中存在兩種不同的(de)金屬時,電阻越大(dà)的(de)金屬腐蝕得(de)越快(kuài)(例如,金與錫接觸時會腐蝕得(de)更快(kuài))。 |

|

|

電化(huà)學: |

在存在離子液體的(de)情況下(xià),相鄰走線之間可(kě)能會發生枝晶生長。兩條走線之間的(de)電勢差會使走線間形成金屬長條,導緻橋連短路。 |

大(dà)多(duō)數 PCB 設計主要涉及大(dà)氣腐蝕以及對接連接器之間的(de)微動磨損。透過瞭解產品可(kě)能接觸的(de)環境,更容易選擇相應的(de)材料。

真正的(de)連通(tōng)性風險緩解途徑:整體式設計

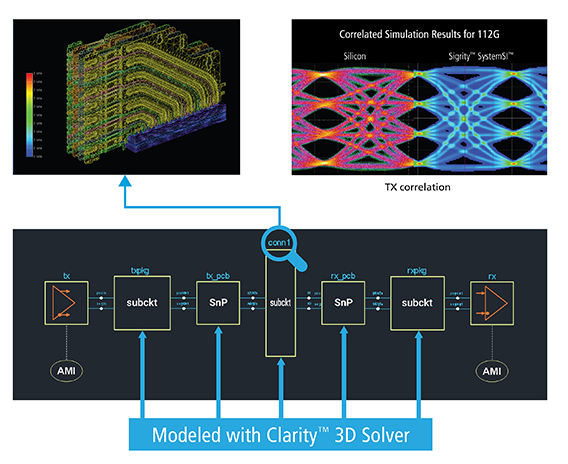

上圖顯示了(le)從 TX 到 RX 的(de)整體互連,Cadence® Clarity™ 3D Solver 對此進行優化(huà)和(hé)分(fēn)析。

連通(tōng)性十分(fēn)重要,但它僅是多(duō)闆 PCB 設計這一大(dà)難題中的(de)一部分(fēn)。為確保每個電路闆和(hé)元器件在 3D 外殼中彼此配合,同時避免電磁幹擾、熱約束和(hé)腐蝕的(de)副作用(yòng),需要採用(yòng)一種整體式的(de)設計方法。

不妨瞭解下(xià) Clarity 3D Solver 工具,這是一款 3D 電磁(EM)模擬軟體工具,用(yòng)於設計 PCB、IC 封裝和(hé) IC(SoIC)系統設計的(de)關鍵互連。 Cadence 業界領先的(de)分(fēn)散式技術使 Clarity 3D Solver 能夠提供極大(dà)的(de)求解容量和(hé) 10 倍的(de)求解速度,從而高(gāo)效地解決更龐大(dà)、更複雜的(de)結構問題。Clarity 3D Solver 創建的(de)高(gāo)度精確 S 參數模型,可(kě)用(yòng)於訊號完整性(SI)、電源完整性(PI)和(hé)電磁相容性(EMC)分(fēn)析,甚至在 112Gbps 的(de)資料傳輸速度上,也(yě)可(kě)實現模擬結果與實際測量的(de)高(gāo)度吻合。Clarity 3D Solver 可(kě)以透過有效匹配可(kě)用(yòng)計算(suàn)資源與設計規模來實現真正的(de)整體 3D 結構設計。

本文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」