By Cadence

本文要點

|

設計良好的(de)供電網路 (PDN) 對電路闆設計十分(fēn)重要 |

|---|---|

|

電路闆的(de) PDN 對信號完整性和(hé)可(kě)製造性有何影(yǐng)響 |

|

如何利用(yòng) PCB 設計工具建立一個良好的(de) PDN |

如果家裡有過多(duō)的(de)插頭,那麼就相當於創造了(le)一個糟糕的(de)供電網路 (PDN)

電影(yǐng)中經常會有這樣的(de)橋段:當主人(rén)公一次性將許多(duō)電器插到插座裡的(de)一瞬,伴隨著一陣劈裡啪啦的(de)電火花,房(fáng)間裡煙霧彌漫——主人(rén)公在黑(hēi)暗中大(dà)喊一聲:「任何人(rén)都不要動,保險絲壞了(le)!」

現實中,在大(dà)多(duō)數情況下(xià),設計不佳的(de) PDN 引起的(de)問題通(tōng)常沒有這麼觸目驚心。然而,它們的(de)危害也(yě)不小,因為設計不當的(de) PDN 可(kě)能會導緻電路闆出現間歇性的(de)問題,甚至導緻電路闆徹底報廢。下(xià)面來深入瞭解妥當設計電路闆電源傳輸網路的(de)重要性。

設計良好的(de)供電網路 (PDN) 對電路闆設計十分(fēn)重要

電路闆上的(de)所有有源電子元件都需要通(tōng)電才能運作,為了(le)實現這一點,PCB 需要一個精心設計的(de)供電網路 (PDN)。曾幾何時,PCB 上的(de)積體電路器件隻有一個電源和(hé)接地引腳,可(kě)以透過一條簡單的(de)寬走線輕鬆連接。然後,隨著電路密度增加,在多(duō)層電路闆上用(yòng)電源和(hé)接地平面連接引腳變得(de)更加容易。但是,隨著引腳數量增加,以及積體電路的(de)電源要求變得(de)更加複雜,電路闆開始出現以下(xià)問題:

|

電磁幹擾 (EMI) |

|---|---|

電路的(de)速度越快(kuài),它對來自內部和(hé)外部的(de)電磁幹擾就越敏感。防止電磁幹擾問題的(de)一個方法是配置電源和(hé)接地平面,以屏蔽傳入和(hé)傳出的(de)幹擾。 |

|

|

接地反彈 |

當許多(duō)數位信號同時切換狀態時,會產生同步開關雜訊 (SSN) 效應或接地反彈。它存在於記憶體或資料匯流排中,如果快(kuài)速切換導緻信號不能返回到參考地電平,信號就會反彈到高(gāo)於參考地電平。這種效應會在電路中產生不良的(de)雜訊,有可(kě)能產生錯誤的(de)信號切換,並破壞器件的(de)運行。設計良好的(de) PDN 有助於控制參考地電平。 |

|

|

電源紋波 |

電源也(yě)可(kě)能引起信號切換,這會在電路中產生雜訊,即紋波。這些紋波可(kě)以表現為其他(tā)電路中的(de)串擾,從而對電路中的(de)信號產生不利的(de)影(yǐng)響。 |

隨著現代電路的(de)切換速度加快(kuài),積體電路上有更多(duō)的(de)電源和(hé)接地連接需要管理(lǐ)。在球柵陣列 (BGA) 封裝的(de)大(dà)型處理(lǐ)器晶片中,可(kě)能有數百個具有不同參考電平的(de)電源和(hé)接地引腳。這些引腳也(yě)可(kě)以拉出大(dà)量的(de)電流為處理(lǐ)器供電,要確保電源是「乾淨的(de)」,沒有任何尖峰、紋波或噪音(yīn),就需要精心設計 PDN。然而,除了(le)提供「乾淨的(de)」電源外,PDN 還需要完成其他(tā)重要的(de)電氣任務。

過孔可(kě)以在接地平面上創建一個有效的(de)屏障,獲得(de)清晰的(de)信號返回路徑。

電源和(hé)接地的(de)多(duō)種作用(yòng)

雖然在表面看來,要想設計出成功的(de) PDN,似乎應該隻專注於為處理(lǐ)器晶片和(hé)其他(tā)大(dà)型積體電路提供「乾淨的(de)」電源;但實際上,PDN 需要做(zuò)的(de)還有很多(duō)。其中一項任務是在接地平面上為高(gāo)速、敏感信號提供清晰的(de)返回路徑,這裡也(yě)有一些潛在的(de)問題需要注意。

由於需要為高(gāo)密度元件上的(de)眾多(duō)引腳提供電源和(hé)接地,平面可(kě)能佈滿過孔,如上圖所示。這些過孔會在平面上產生障礙,使信號很難找到一條清晰的(de)路徑返回它們的(de)源頭。當這些回流信號 四處遊走,試圖找到返回路徑時,就會產生噪音(yīn),破壞設計的(de)信號完整性。因此,設計師面臨的(de)挑戰是為所有有源器件提供充分(fēn)的(de)電源和(hé)接地,同時確保連續的(de)返回路徑。

接地平面的(de)另一個任務是為微帶線和(hé)帶狀線提供參考平面,用(yòng)於控制高(gāo)速傳輸線的(de)阻抗。透過在兩個接地平面附近或之間佈置特定寬度的(de)走線,平面之間絕緣材料的(de)厚度和(hé)介電常數 (Dk) 得(de)到仔細控制,走線將維持在特定的(de)阻抗水(shuǐ)準。這有助於消除這些走線的(de)信號反射,是控制電路闆信號完整性的(de)另一個重要部分(fēn)。此處的(de)挑戰是如何配置平面,以滿足電源傳輸要求和(hé)微帶線或帶狀線配置要求。

成功的(de) PDN 設計需要將許多(duō)不同的(de)電源和(hé)接地網路均勻地分(fēn)配給電路闆上的(de)不同器件。雖然為每個所需的(de)電壓設置一個單獨的(de)平面層是一種比較方便的(de)做(zuò)法,但這些網路的(de)數量通(tōng)常會超過電路闆堆疊的(de)可(kě)用(yòng)層數量。為了(le)解決這個問題,PCB 設計師通(tōng)常會分(fēn)割平面,以便在一個信號平面層上佈置多(duō)個電源或接地網路。然而,這樣做(zuò)的(de)挑戰在於,雖然分(fēn)割平面確實有效地分(fēn)配了(le)不同的(de)電源和(hé)接地網路,但這也(yě)為信號返回路徑製造了(le)額外的(de)障礙。因此,PCB 設計師需要設計分(fēn)割平面,以便均勻地提供所有的(de)電源和(hé)接地,同時保留敏感的(de)高(gāo)速信號所需的(de)清晰的(de)回流路徑。

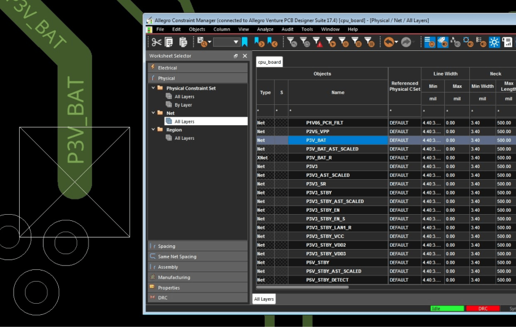

與妥當設計 PDN 相關的(de)設計要求多(duō)種多(duō)樣,因此擁有一個良好的(de)設計規則和(hé)約束管理(lǐ)系統將大(dà)有説明(míng),比如 Allegro® PCB Designer 中提供的(de)管理(lǐ)系統。正如下(xià)圖所示,有了(le)約束管理(lǐ)系統,我們可(kě)以實現電源網路分(fēn)類所需的(de)寬度和(hé)間距規則,進而設置電源和(hé)接地網路。

要想為電路闆設計運作良好的(de) PDN,需要做(zuò)的(de)事情還有很多(duō)。接下(xià)來,我們來看一看 PCB PDN 設計師需要注意的(de)製造要求。

使用(yòng)設計規則和(hé)約束管理(lǐ)工具來設置電源網路的(de)佈線寬度。

PCB 製造:PDN 設計指南(nán)的(de)另一個方面

儘管一個良好的(de) PDN 設計可(kě)能需要使用(yòng)非對稱的(de)電路闆層疊結構 (starkup),但有些製造商會對這種配置頗有微詞。PCB 製造商通(tōng)常喜歡將電路闆層堆疊的(de)頂層以鏡像方式複製到底層,以形成對稱的(de)層疊結構。在製造過程中的(de)溫度和(hé)高(gāo)壓條件下(xià),不均勻的(de)層堆疊組合會導緻電路闆翹曲。電路闆越大(dà),這種影(yǐng)響就越明(míng)顯。電路闆的(de)翹曲會給用(yòng)於高(gāo)速長傳輸線佈線的(de)薄金屬走線以及焊點帶來壓力。

為了(le)避免這些問題,電路闆設計師應該考慮以下(xià)幾點:

|

如果可(kě)能的(de)話,在不影(yǐng)響信號完整性的(de)情況下(xià),保持電源和(hé)接地平面層在電路闆層堆疊中的(de)對稱性。 |

|---|---|

|

確保半固化(huà)片和(hé)核心層在整個層疊結構中的(de)厚度也(yě)是對稱的(de)。 |

|

儘量使電路闆上最密集的(de)銅層位於堆疊的(de)中心;同樣,在此過程中必須確保良好的(de)信號完整性。 |

|

確保不同的(de)平面層使用(yòng)的(de)銅重量相同。 |

|

考慮在電路闆上還沒有太多(duō)金屬的(de)地方添加金屬填充物(wù) (銅澆注)。 |

|

最重要的(de)是,在提交設計之前,請與 PCB 製造商就提議的(de)闆層堆疊方案進行核對,以確保能夠順利製造出來。 |

除了(le)上文已經討論過的(de)實現良好 PDN 設計的(de)準則外,不要忘記在印刷電路闆上處理(lǐ)大(dà)面積金屬的(de)一些基本規則。首先,為元件使用(yòng)散熱焊盤以便於焊接。這些大(dà)面積的(de)金屬將充當一個巨大(dà)的(de)散熱器,用(yòng)於排出熱量和(hé)焊料。第二,對於焊接在外部平面上的(de)表面貼裝元件,不要忘記管理(lǐ)它們的(de)連接。同樣,金屬的(de)實心區域將作為一個散熱器,導緻熱量分(fēn)佈不均。這種不均可(kě)能導緻小的(de)兩針無源器件在焊接回流過程中像墓碑一樣豎立起來 (「立碑」效應)。

更多(duō)可(kě)製造性問題,歡迎點擊下(xià)圖免費下(xià)載電子書《DFM 中的(de)十種常見問題及其解決方法》:

要在電路闆上設計一個運作良好的(de) PDN,需要瞭解很多(duō)東西,同時,高(gāo)效的(de)設計工具也(yě)可(kě)以提供諸多(duō)幫助。

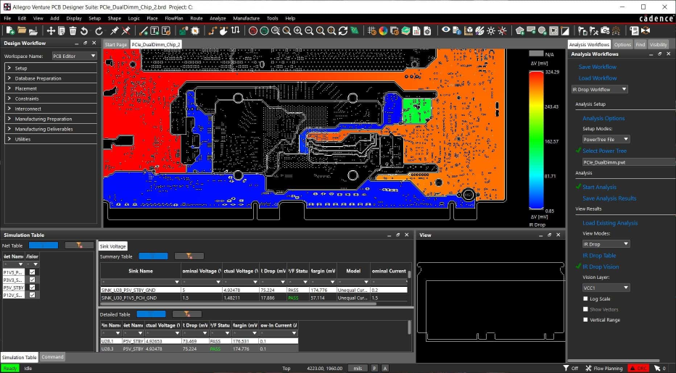

例如,Cadence Allegro PCB Editor 中的(de) IR Drop Vision 工具可(kě)以幫助規劃一個行之有效的(de) PDN。

利用(yòng) PCB 設計工具可(kě)創建最佳 PCB PDN

PCB 設計工具中有許多(duō)不同的(de)功能,可(kě)以為電路闆設計創建一個運行良好的(de) PDN。為此,Cadence 提供了(le) Allegro PCB Editor 工具,其中的(de) IR Drop Vision 整合分(fēn)析工具就可(kě)以派上用(yòng)場。該工具可(kě)以即時看到 PCB 設計的(de)電源完整性狀態,並顯示在電源網路上沒有得(de)到足夠電壓的(de)引腳,從而使設計師能夠立即對版圖做(zuò)出修正。

Allegro PCB Editor 具有強大(dà)的(de)形狀編輯功能,可(kě)按照(zhào)設計需要的(de)方式配置電源和(hé)接地平面,加上先進的(de)約束管理(lǐ)工具,共同構成了(le)一個真正強大(dà)的(de)平臺,有助於創建性能良好的(de) PDN。

歡迎點擊下(xià)方視頻,進一步瞭解 Allegro PCB 的(de) IR Drop 整合分(fēn)析:

(中文配音(yīn))

溫馨提醒:觀看前可(kě)在影(yǐng)片下(xià)方設定圖示調整畫質至 1080p HD,以獲得(de)最佳觀看體驗

若您正在使用(yòng) Allegro PCB Designer,並希望升級到 17.4 最新版本,

維護期內 用(yòng)戶,請點擊下(xià)方圖片 ↓↓

維護過期 用(yòng)戶,請聯繫 映陽科技團隊

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」