By Ken Willis, Cadence

啟用(yòng)約束驅動設計

透過構建預佈局測試平臺,填入相關模型,生成結果逼真的(de)模擬結果,這時候正適合啟用(yòng)約束來驅動和(hé)控制串列鏈路的(de)物(wù)理(lǐ)佈局。這可(kě)能會導緻測試平臺需要一些改進和(hé)反覆運算(suàn),來添加更多(duō)的(de)細節,這是可(kě)預期的(de)。此時的(de)方法是參數化(huà)測試平臺的(de)關鍵元素,掃描它們以量化(huà)其對整個介面性能的(de)影(yǐng)響,並限制那些參數以確保我們的(de)設計在完成時滿足合規要求。在 PCI Express Gen 4 的(de)情況下(xià),核心要求是眼圖高(gāo)度至少為 15mV,眼圖寬度為0.3UI(對於 16Gbps 的(de)資料速率而言約為 19ps),目標誤碼率(BER)為 1e-12。

那麼掃描哪些類型的(de)參數是有意義的(de)?我們從 SerDes 器件開始,他(tā)們的(de)電路模型中通(tōng)常含有矽工藝 / 溫度 / 電壓(PVT)的(de)快(kuài)速和(hé)慢(màn)速 Corner 係數,所以這方面應該被覆蓋。如果您是 PCB 的(de)設計人(rén)員,可(kě)能不一定會修改或控制它們,但是它們的(de)影(yǐng)響應該在掃描模擬中加以考慮,因為您的(de) PCB 需要在那些條件下(xià)工作。另外,如果您能夠獲得(de) SerDes 的(de)封裝模型,涵蓋互連寄生效應的(de)最小 / 最大(dà)範圍,那麼也(yě)應被包括進去。連接器和(hé) AC 耦合電容模型也(yě)是如此。

PCB 互連從發射器開始工作,一直到接收器。如今的(de)器件具有精細的(de)引腳間距,為了(le)從這些器件順利出線,通(tōng)常需要縮小差分(fēn)對的(de)線寬和(hé)間距。因此這些變窄的(de)幾何結構一般會比電路闆的(de)主要部分(fēn)產生更高(gāo)的(de)阻抗,因此會產生阻抗不連續性。扇出線應該走多(duō)長才不會出現問題?這也(yě)需要在鏈路的(de)接收端考慮。

一旦輸出到電路闆的(de)主要部分(fēn),就應掃描差分(fēn)對的(de)線寬和(hé)間距,以達到 PCB 預期的(de)阻抗容差範圍(通(tōng)常+/- 10%)。而且,始終保持電路闆上差分(fēn)走線的(de)間距不變可(kě)能是不切實際的(de)。他(tā)們可(kě)能需要彼此分(fēn)開,並短暫解耦以繞過障礙,甚至連接到 AC 耦合電容。這將改變差分(fēn)對的(de)特性阻抗。解耦線可(kě)以走多(duō)長?電容引腳的(de) escape 走線可(kě)以走多(duō)長?這對結果有嚴重影(yǐng)響嗎?

在哪裡放置電容?發射端附近?接收端附近?位置有影(yǐng)響嗎?掃描位置資訊可(kě)以量化(huà)這些影(yǐng)響。差分(fēn)對正負引腳之間可(kě)以走多(duō)長的(de)線?佈線長度是否需要在 layout 中匹配到 +/- 1 mil 範圍內?還是可(kě)以允許 10 或 20mils 的(de)容差?請記住,弄清楚什(shén)麼是無關緊要的(de)與什(shén)麼是緊要的(de)同樣重要。

串擾可(kě)能會對串列鏈路介面產生很大(dà)的(de)影(yǐng)響。如果電路闆上有足夠的(de)空間,則可(kě)以方便地將約束用(yòng)於差分(fēn)對周圍,以產生足夠的(de)間距,來解決串擾問題。但是許多(duō)設計太密集以至於這種方法無法適用(yòng),這意味著其他(tā)信號到差分(fēn)串列鏈路的(de)間隔和(hé)耦合長度也(yě)需要考慮並掃描。

鏈路的(de)總長度也(yě)是一個基本要素。 SerDes 器件的(de)均衡設計是為了(le)抵制有損互連,但是它們能夠做(zuò)到的(de)效果是有限的(de)。需要確定的(de)一個很重要的(de)參數是:整個佈線達到多(duō)長時仍然可(kě)以生成符合規範的(de)結果。

以下(xià)這些因素可(kě)能並不是需要考慮的(de)約束的(de)全部清單,但提供了(le)一個好的(de)開始:

|

扇出佈線寬度、間距、長度 |

|---|---|

|

主要佈線層分(fēn)配 |

|

額定的(de)差分(fēn)線寬度和(hé)間距 |

|

阻抗容差 |

|

最大(dà)非耦合長度 |

|

最大(dà)過孔數 |

|

差分(fēn)相位容差 |

|

AC 耦合電容到發射端或接收端的(de)最大(dà)長度 |

|

整個串列鏈路佈線的(de)最大(dà)長度 |

|

與其他(tā)信號的(de)最小間距和(hé)最大(dà)耦合長度(平行狀態) |

|

過孔結構定義 |

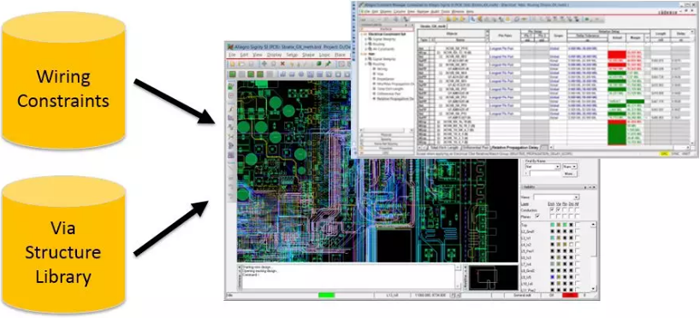

將這些參數加入預佈局測試平臺中,可(kě)以掃描這些參數,並對其影(yǐng)響進行量化(huà)。這項工作所交付的(de)是一套現實的(de)、可(kě)執行的(de)、量化(huà)的(de)約束,可(kě)以導入到物(wù)理(lǐ)佈局過程,並由 layout 設計人(rén)員使用(yòng)自動設計規則和(hé)電氣規則檢查( DRC / ERC )來控制關鍵串列鏈路介面的(de)佈局和(hé)佈線。

Layout 設計人(rén)員通(tōng)常要求放鬆或修改初始的(de)佈線規則。這是很平常的(de),因為有時候一些細微的(de)修改可(kě)以使設計更加整潔和(hé)高(gāo)效。而在預佈局的(de)測試平臺中,應該可(kě)以很直接地調整一些參數,重新掃描,並評估所需的(de)改變是否會大(dà)大(dà)影(yǐng)響 Margin。這個「協商」過程可(kě)能會經歷幾個反覆運算(suàn)迴圈,才能產生更好的(de)成品。從 SI 的(de)角度來看,最終目標仍然是透過佈線設計來完成最後的(de)驗證和(hé)合規性檢查,並產生可(kě)接受的(de) Margin。

圖 1:將約束加入 layout 以啟用(yòng)約束驅動設計

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」