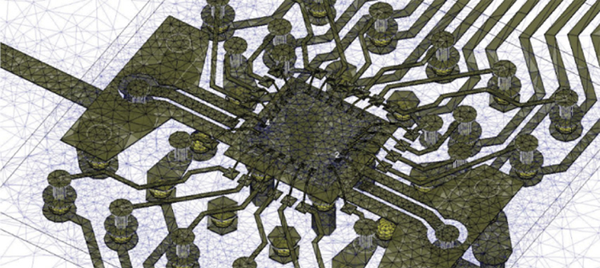

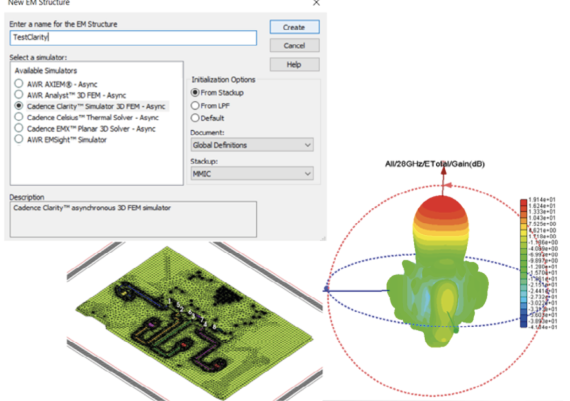

Cadence AWR V16 提供完整全面的(de)RF工作流程,並具備突破性的(de)跨平台互通(tōng)性,支援高(gāo)頻射頻 (RF) 到毫米波 (mmWave) IP 異質技術開發。此外,更導入了(le)與 Clarity™ 3D 求解器的(de)無縫整合,為大(dà)規模複雜 RF 系統的(de)電磁分(fēn)析提供不受拘束的(de)處理(lǐ)量!

AWR V16 平台和(hé)求解器整合之後再與其他(tā)工作流程相比,所減少的(de)周轉時間 (TAT) 高(gāo)達 50%,得(de)以更高(gāo)效地為汽車、雷達和(hé)半導體設計5G無線與連結系統,且更快(kuài)上市。

本次視頻將傳授 AWR V16 功能應用(yòng)於 RF PCB 設計的(de)心法訣竅。

| 視頻 節點 | 課程內容 |

|---|---|

00 : 01 |

本場議題介紹 |

00 : 15 |

議程大(dà)綱說明(míng) |

00 : 24 |

RF 設計挑戰 |

03 : 42 |

Cadence AWR 設計環境與 Clarity 3D Solver 特點概述 |

11 : 22 |

針對 PCB Layout 的(de) EM 驗證設計流程 |

21 : 49 |

實例分(fēn)享 (1) – 10 層 Serdes 設計 |

22 : 21 |

實例分(fēn)享 (2) – 封裝模組 |

23 : 07 |

實例分(fēn)享 (3) – PCB 版 + 連接器 |

24 : 21 |

各式 PCB 測試案例效能比較 |

25 : 14 |

各式 IC Package 測試案例效能比較 |

25 : 40 |

優化(huà) RF 設計方法 |

33 : 31 |

總結 |