By Scott Liu, Graser

在現行射頻(RF) PCB 設計中,我們常面臨在極有限的(de)空間限制下(xià)進行設計,尤其 PCB 闆內互連的(de)RF路徑常需要與 PCB 闆上外部元件或是其他(tā)高(gāo)速訊號線同時考慮。另外,還需考量 RF 路徑在設計上是否會受到闆材和(hé)疊層、元器件放置與其他(tā)高(gāo)速佈線電路的(de)影(yǐng)響。

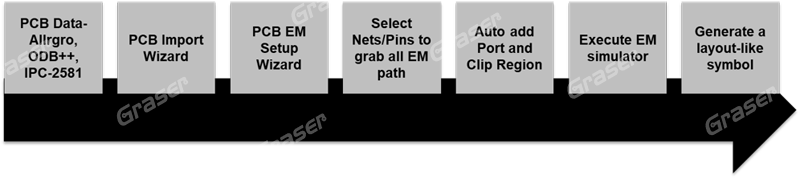

為了(le)能更有效了(le)解以上種種因素對於RF路徑的(de)影(yǐng)響來找出問題, AWR 提供了(le)一系列的(de) Wizard (精靈)功能和(hé)強大(dà)的(de)電磁場求解器 - AXIEM 3D planar MoM EM simulator,幫助使用(yòng)者隻需藉由幾個步驟就能快(kuài)速進行電磁場分(fēn)析。

本文將解析各項 Wizard 功能要點和(hé)運用(yòng)時機。

AWR Microwave Office 設計環境平台提供了(le) PCB Import Wizard (PCB 匯入精靈) 和(hé) PCB EM Setup Wizard (PCB 電磁設置精靈),使用(yòng)者能夠透過這二項便利的(de) Wizard 對需要驗證的(de)訊號線與布局區域,加速訊號路徑的(de)提取,並且可(kě)對取出來的(de)布局區域做(zuò)適時的(de)簡化(huà)來減少電磁 (EM) 分(fēn)析時的(de)網格 (Mesh) 計算(suàn),然後再帶入至 AWR AXIEM Simulator 中做(zuò) EM 分(fēn)析。最終,你可(kě)以將 EM 的(de)結果轉換為布局式的(de)元件符號 (Symbol),使其易於與 Lump 或 TLine 等元件連結進行阻抗設計以實現最佳阻抗設計。甚至也(yě)可(kě)結合 AWR Visual System Simulator (VSS),進一步去觀察訊號線的(de)阻抗或是相位可(kě)能對通(tōng)道品質,如相鄰通(tōng)道功率比 (ACPR) 或是誤差向量幅度 (EVM)… 的(de)影(yǐng)響,進而找出改善方式。

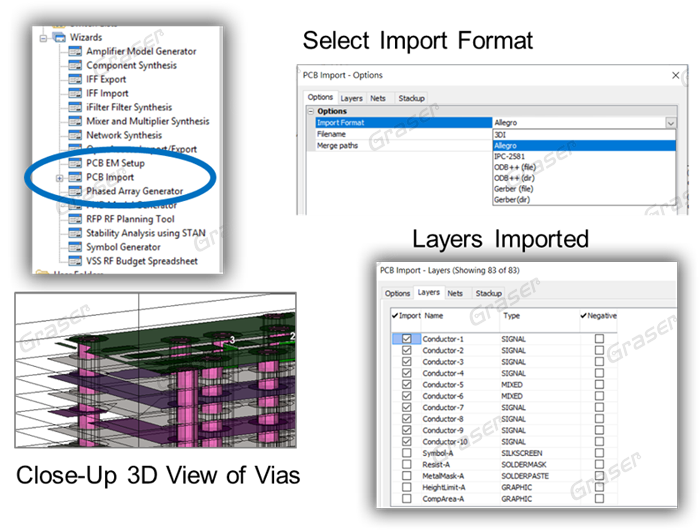

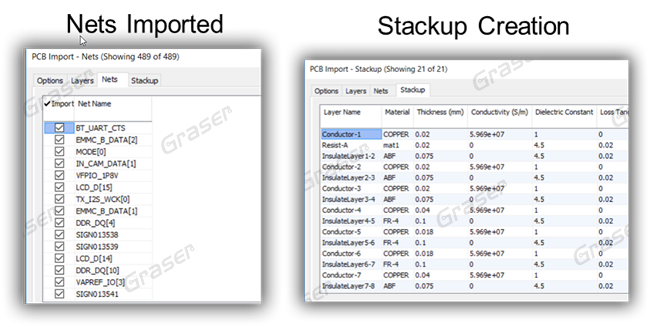

PCB 匯入精靈 (PCB Import Wizard)

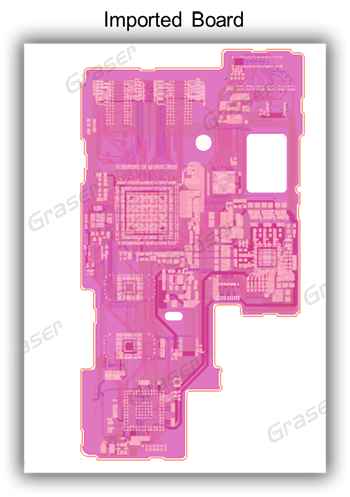

PCB Import Wizard 提供快(kuài)速匯入 PCB 設計格式的(de)介面,可(kě)支援導入 3DI / Allegro / IPC-2581 / ODB++ / Gerber 等格式,可(kě)藉由 Layers 與 Nets 的(de)設置決定是否要過濾掉匯入的(de) layer 與 net 資訊, 更方便的(de)是你可(kě)以將原本已經定義好的(de)材料如 DK/DF 與厚度… 直接藉由 Wizard 導入進到 AWR 中, 以便後續進行電磁模擬的(de)分(fēn)析,且現已可(kě)以直接導入 Allegro 的(de) Layout 格式。

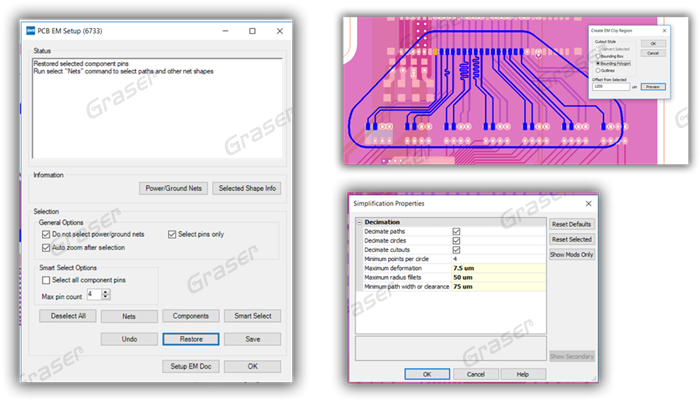

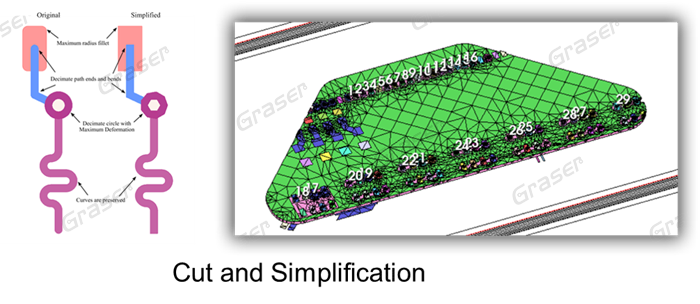

PCB 電磁設置精靈 (PCB EM SetUp Wizard)

PCB EM SetUp Wizard 用(yòng)於快(kuài)速提取需要做(zuò)電磁場分(fēn)析的(de)線路與區域。 Wizard 的(de)操作非常容易便捷,點選表單中的(de) Smart Select 就可(kě)以快(kuài)速將整路需要做(zuò)電磁場分(fēn)析的(de)線徑一次選取。 你僅需要選擇 Pin 或是 Net,如此 AWR 就可(kě)以使用(yòng)紀錄在線路上 Net 與 Pin 的(de)資訊一次性的(de)將整條路徑選取。 然後 Wizard 將自動識別出 Pin 的(de)位置,並自動加上 Port,最後進行電磁場分(fēn)析區域的(de)裁切。 你可(kě)再依照(zhào)自己電腦的(de)能力或是依計算(suàn)精度與效能的(de)權衡決定是否要對其結構簡化(huà),如此就完成了(le)電磁場分(fēn)析的(de)前置準備。然後,你就可(kě)以開始直接運行 AXIEM 電磁模擬。

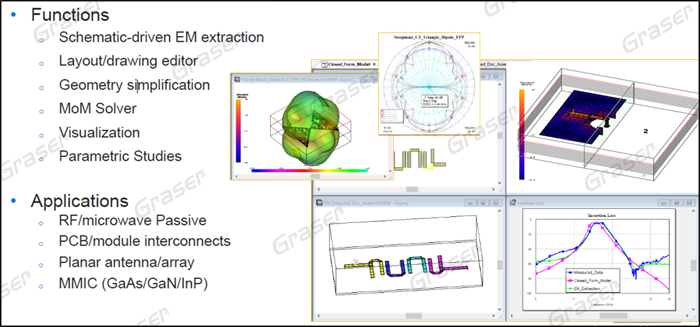

EM 分(fēn)析 (AXIEM)

AWR 的(de) AXIEM 為三維平面式電磁分(fēn)析工具。 無論是針對射頻印刷電路闆 (RF PCB)、模組、低溫共燒陶瓷封裝 (LTCC)、單晶微波積體電路 (MMIC)、射頻積體電路 (RFIC) 或天線的(de)特性分(fēn)析或是最佳化(huà), AXIEM 的(de)模擬準確度、性能和(hé)速度無庸置疑,助力縮短設計周期,為您節省寶貴的(de)時間和(hé)金錢。

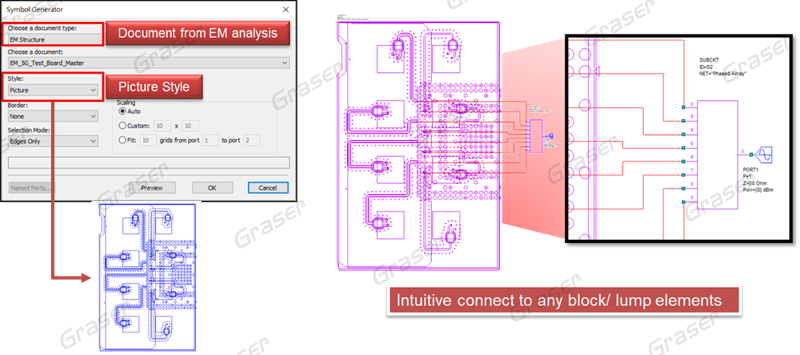

元件符號產生器精靈 (Symbol Generator Wizard)

在電磁 (EM) 分(fēn)析後,為了(le)使 EM 的(de) S 參數模型與元器件更容易的(de)去混合設計在搭配不同廠牌、尺寸 / 規格的(de)元件,或是使用(yòng)傳輸線模型進行阻抗設計或是最佳化(huà),AWR 的(de) Symbol Generator Wizard 能夠將 EM Layout 的(de) Pattern 直接產生出一樣的(de)符號視圖 (Symbol View),使得(de)可(kě)以在電路視圖 (Schematic View) 當中選用(yòng)並直接在原本 Pin 的(de)位置上連結元器件,讓混合設計更加容易進行與驗證。

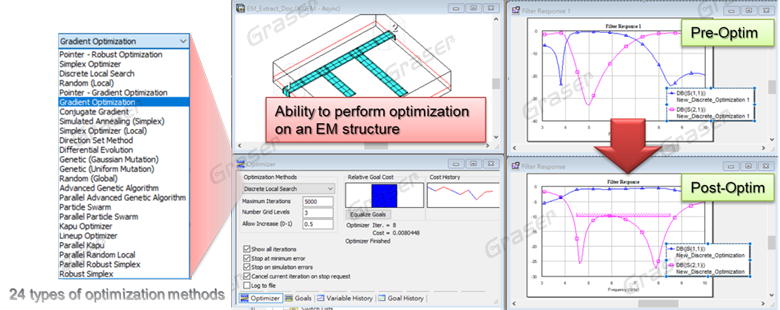

最佳化(huà)設計

AWR 提供最佳化(huà)設計方法,具有自動調整電路元件參數,如電路元件值、傳輸線長度或是對傳輸線或 Layout 結構做(zuò)參數化(huà)設置,使其最佳化(huà)分(fēn)析時可(kě)以自動疊代參數化(huà)的(de)長度進行電磁分(fēn)析,以實現用(yòng)戶指定的(de)目標性能。

AWR V16 已於日前發佈,最重要的(de)幾項包括:

|

與 Allegro 整合:確保與 PCB 和(hé) IC 封裝設計流程的(de)製造相容性和(hé)射頻整合 |

|---|---|

|

與 Virtuoso 整合:利用(yòng) AWR Microwave Office 完成射頻前端設計 IP,並將其與 Virtuoso Layout Suite 結合使用(yòng),以進行積體電路和(hé)模組整合 |

|

與 Clarity 3D Solver 整合:支援 EM 分(fēn)析,用(yòng)於大(dà)型射頻結構的(de)設計驗證,例如模組封裝和(hé)相控陣饋電網路 |

|

與 Celsius Thermal Solver 整合:為單片微波 IC (MMIC) 和(hé) PCB 高(gāo)功率射頻應用(yòng)提供熱分(fēn)析 |

|

AWR 增強功能:利用(yòng)設計自動化(huà)和(hé)有限元分(fēn)析 (FEA) 求解器性能的(de)增強,加速射頻 IP 的(de)創建 |