By Paul McLellan, Cadence

現在 DRAM 市場上的(de)談論熱點是 DDR5。很多(duō)人(rén)可(kě)能以為 JEDEC 已經確定了(le)其標準,但實際上它在技術上仍處於開發階段。我認為最終的(de) DDR5 標準有望在 2018 年底前出來。

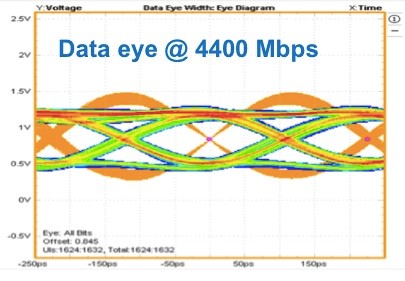

在台積電的(de) OIP 生態系統論壇上,Cadence 的(de) Marc Greenberg 和(hé) Micron(美(měi)光(guāng))的(de) Ryan Baxter 就 DDR5 的(de)挑戰和(hé)解決方案發表了(le)演講。由於工程耗時較長,兩家公司決定不再等待 DDR5 標準發佈而共同制定了(le)一個與他(tā)們所預期的(de)最終標準相接近的(de)詳細規格。其中,Cadence 開發 DDR5 的(de)介面 IP,Micron 則開發 DDR5 DRAM 的(de)原型。此舉的(de)另一動機也(yě)是以此證明(míng)互通(tōng)性是證明(míng)標準合規性的(de)唯一真實可(kě)行的(de)方法。從下(xià)方的(de)結果的(de)資料眼圖可(kě)以看到數據 4400Mbps 都可(kě)以正常工作。

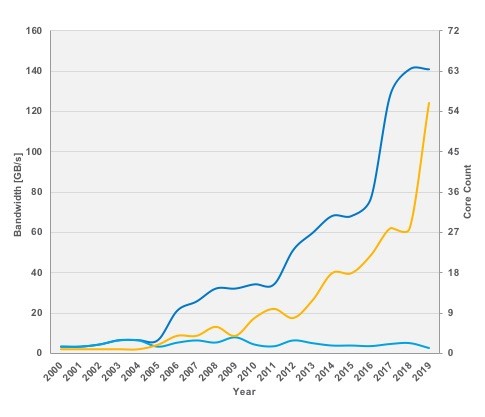

DDR3 和(hé) DDR4 轉換的(de)最大(dà)驅動力是客戶及移動設備,而 DDR5 的(de)主要驅動因素則是對頻寬的(de)需求。由於系統記憶體頻寬跟不上伺服器 CPU 核心數量的(de)增長,伺服器因此需要更大(dà)的(de)記憶體頻寬。更嚴格來說,記憶體頻寬在很多(duō)年前就已不是由處理(lǐ)器速度的(de)增長所驅動,而是所需要的(de)相應記憶體頻寬的(de)增長驅動。現在,矽片空間被用(yòng)於為每個晶片添加更多(duō)的(de)內核。從密度的(de)角度來看,DRAM 的(de)擴展越來越具有挑戰性從而導緻了(le)不匹配。下(xià)方的(de)圖表以圖形方式展示了(le)這一點,最底部的(de)淺藍色線代表每個內核的(de)頻寬(基本不變),黃線代表 CPU 內核的(de)數量,深藍色線則代表系統記憶體的(de)頻寬。

今年早些時候,Marc 向我解釋說:

「由於物(wù)理(lǐ)學的(de)規律,隨著記憶體晶片越來越大(dà),它們變得(de)越來越慢(màn)。當在 1X 記憶體技術中構建 16Gb 晶片時,距離會變得(de)非常長,使得(de)很多(duō)核心時序參數問題變得(de)更加嚴重。這導緻了(le)記憶體跟不上 CPU 發展,於是不得(de)不對其進行過度設計使其變得(de)更大(dà),如此形成了(le)惡性循環。但是為了(le)能擁有更多(duō)的(de)資料集、更大(dà)的(de)資料庫和(hé)更大(dà)的(de)設計容量,所有人(rén)都希望每個伺服器裡能有更多(duō)的(de)記憶體。內核的(de)速度保持不變,I/O 的(de)速度卻越來越快(kuài)。」

上表顯示了(le)三個主要市場中 DDR5(包括 LPDDR5)的(de)預期採用(yòng)趨勢:伺服器、PC 和(hé)消費/工業設備(我認為移動設備歸於此類)。第四列進程節點代表的(de)是 SoCs 與 DDR5 IP 結合的(de)工藝節點。記憶體技術有其自身的(de)發展路線和(hé)命名慣例。

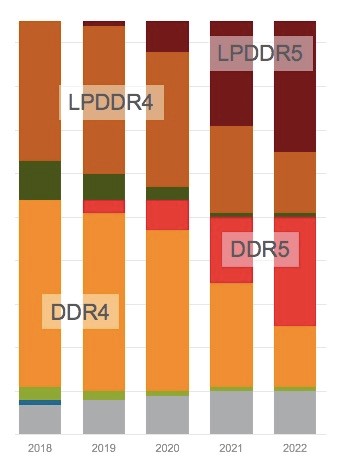

下(xià)方圖表顯示了(le)市場的(de)細分(fēn)狀況,隨著中間紅色代表的(de) DDR5 不斷增長,頂部棕色代表的(de) LPDDR5 也(yě)在同期增長,並預計在 2022 年共同佔據市場份額的(de)三分(fēn)之一。

DDR5 不僅僅可(kě)以比之前的(de)技術以更快(kuài)的(de)速度實現,它還具有:

|

更快(kuài)的(de)資料速率 |

|---|---|

|

更高(gāo)的(de)指令匯流排效率 |

|

改進的(de) bank group 以提高(gāo)性能 |

|

改進的(de)刷新方案 |

|

可(kě)擴展的(de)超過 16Gb 的(de)單片密度 |

|

每個模組 2 個獨立的(de) 40 位通(tōng)道 |

考慮除速度增加以外的(de)所有因素的(de)話, DDR5 3200 的(de)頻寬已經比 DDR4 3200 提高(gāo)了(le) 1.36 倍。再加上提速的(de)影(yǐng)響,DDR5 4800 比 DDR4 3200 的(de)頻寬就提高(gāo)了(le) 1.87 倍,接近 2 倍。

Ryan 表示在明(míng)年的(de)晚些時候,市場將推出以亞 18nm 工藝節點製造的(de) 16Gb 生產設備。DDR5 允許未來擴展,但當 DRAM 製造達到 10-12nm 時,由於對晶片的(de)要求大(dà)幅增加(可(kě)變的(de)滯留時間及其他(tā)原子級現象),我們仍需對其擴展的(de)可(kě)能性投入大(dà)量工作。

Marc 進而表示 Cadence 已經擁有使用(yòng) 7nm 和(hé) 7nm+ IP 的(de)設計作為開端,未來將繼續開發更先進的(de)技術。儘管目前仍專注於伺服器和(hé)用(yòng)戶端,消費和(hé)工業領域的(de)發展會緊隨其後。

結語:

DDR5 具有革命性的(de)性能優勢。2022 年,人(rén)人(rén)都將使用(yòng)它。

本文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」