Paul McLellan, Cadence

上一篇文章(zhāng) 介紹了(le) IBIS 和(hé) AMI,並提到了(le)行業內正在發生的(de)一個重大(dà)變化(huà): DDR5 標準將 (間接) 授權使用(yòng) AMI 模型。

DDR5

在預計將於今年夏季發佈的(de) DDR5 標準中,DRAM 將被指定涵蓋 DFE (判決回饋均衡) 能力。 而在實踐中,DFE 建模就意味著創建和(hé)使用(yòng) AMI 模型。 實際上,近十年來用(yòng)於分(fēn)析串列鏈路的(de)技術正在擴展應用(yòng)到並行記憶體介面領域。

然而,SerDes 和(hé) DRAM 在本質上存在著一些差異。 串列鏈路通(tōng)常很長且有損耗,而 DRAM 則較短且損耗較少。低損耗貌似值得(de)稱讚,在某些方面它確實如此,但是反射會在低損耗鏈路中持續長時間的(de)反彈,而在較長的(de)串列鏈路中則由於高(gāo)損耗而迅速衰減。 這就是 DRAM 需要使用(yòng) DFE 的(de)原因:DFE 會消除錯誤並解決反射問題。 SerDes 中僅有一個發射器和(hé)一個接收器; 但是像 PC 和(hé)伺服器這樣的(de)系統通(tōng)常在同一條匯流排上有多(duō)個 DIMM,有時還會有未插入的(de)插槽,以上這些都會使反射問題變得(de)更加棘手。

雖然 JEDEC 尚未最終完成 DDR5 標準,但是不論是智慧財產權設計團隊、DRAM 供應商,還是我們在全力開發新一代信號完整性 (SI) 方案的(de) Sigrity 產品線團隊,都不希望耗時在等待上。 開發進展刻不容緩,我們需要及時地做(zuò)出必要的(de)改變和(hé)調整,以在最終標準出臺時滿足用(yòng)戶要求。

AMI Builder

AMI Builder 的(de)目標是使使用(yòng)者能夠從已知、良好的(de) AMI 模組庫中快(kuài)速構建符合 IBIS 的(de) AMI 模型,而不是從頭開始在空白文字編輯器上費力編寫容易出錯的(de)代碼。 如果使用(yòng)者不具備類似 C 語言的(de)良好的(de)軟體發展專業知識,那麼應用(yòng)難度無疑會陡然增加。

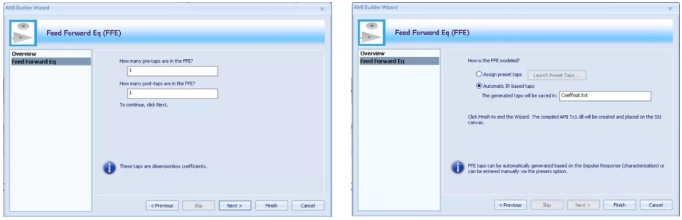

AMI Builder 的(de)基本方法是為發射器配置諸如 FFE (前饋均衡) 等構件。然後嚮導器會令用(yòng)戶對參數進行設置,某些情況下(xià)也(yě)會對參數進行自動計算(suàn)。 例如,上圖顯示的(de)是為 FFE 設置參數,然後令其計算(suàn)抽頭值。圖表可(kě)以直接從嚮導器中繪製,而無需執行模擬。

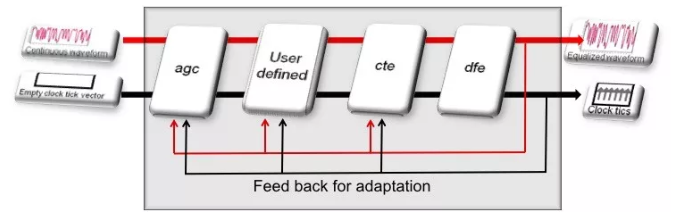

接收器路徑如上圖所示。AGC 表示自動增益控制,CTE (或 CTLE) 是連續時間 (線性) 等化(huà)器,DFE 代表判決回饋均衡。信號從通(tōng)道左側進入,在右側則輸出資料和(hé)已恢復的(de)時鐘。

一旦在嚮導器中設置好選項,模型就會立即被編譯成 DLL 並可(kě)進行模擬和(hé)測試。在測試過程中,模組可(kě)以根據需要被啟用(yòng)、禁用(yòng)、編輯或刪除。該流程的(de)一大(dà)優勢是可(kě)以令用(yòng)戶專注於架構而無需費心編碼,同時為使用(yòng)者提供輕鬆迅捷地按鈕式模型創建方式。

AMI 建模和(hé) AMI Builder 技術最初為 SerDes 應用(yòng)程式而開發,現已擴展到 DDR 應用(yòng)領域。

針對 DDR4 的(de) AMI

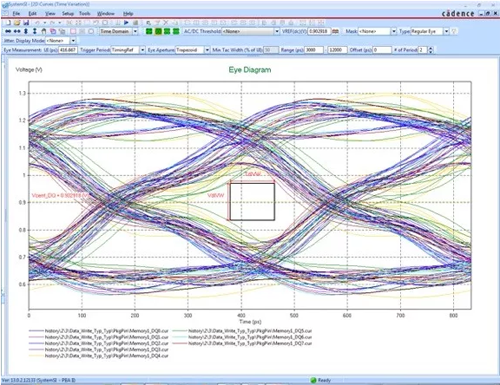

DDR4 已經帶來了(le)一些新挑戰,特別是 DQ 掩膜一緻性檢查。該功能可(kě)確保眼睛保持在掩膜之外,從而保證系統正常工作。 如上圖所示,掩膜是中間的(de)矩形框,而信號則成功地圍繞其周遭,這意味著眼睛已睜開到足以符合標準的(de)程度。

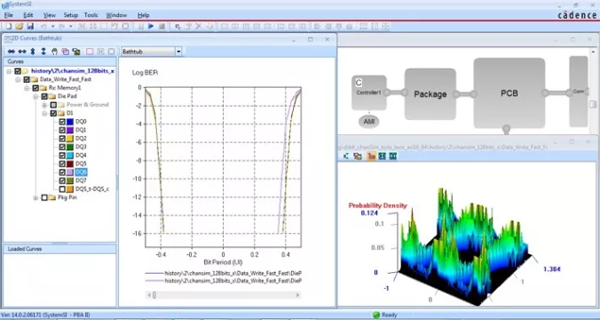

誤碼率 (BER) 分(fēn)析也(yě)必不可(kě)少,因此我們需要通(tōng)道模擬和(hé)浴盆曲線。這裡的(de)浴盆曲線和(hé)與其同名的(de)可(kě)靠性浴盆曲線毫無關係,後者用(yòng)於在半導體使用(yòng)壽命的(de)開始和(hé)結束時顯示高(gāo)故障率 (即早期故障期和(hé)後期老化(huà)期)。信號完整性浴盆曲線是通(tōng)過給輸入信號添加抖動和(hé)雜訊來得(de)到的(de)。上圖的(de)中心窗(chuāng)格即顯示浴盆曲線。其中有兩個浴盆,一個是使用(yòng)抖動來獲得(de)水(shuǐ)準的(de) (時間角度) 浴盆,另一個則是使用(yòng)雜訊來獲得(de)垂直的(de) (信號角度) 浴盆。

由於需要的(de)比特數量極大(dà) (數十萬甚至數百萬),使用(yòng) IBIS-AMI 模型估算(suàn)BER模擬是唯一真正可(kě)行的(de)方法。去年夏季,Cadence 為 DDR4 提供了(le)第一款 IBIS-AMI 模型,並於今年初在 DesignCon 上進行展示。

與串列鏈路相比,DDR 的(de)另一個變化(huà)是:由於它是一個平行介面,因而存在碼間幹擾和(hé)同步開關雜訊,這些都需要在匯流排特性模擬中捕獲。

針對 DDR5 的(de) AMI

首先請注意,JEDEC 還沒有最終確定 DDR5 標準,因而任何改變都有可(kě)能發生。但是既然已經臨近發佈,那麼關鍵問題如數據速率的(de)改變機率則非常之低。如下(xià)是相關描述:

|

基於掩膜的(de)合規性檢查 (應用(yòng)於 DDR4 中,前文已做(zuò)討論) 將繼續進行 |

|---|---|

|

電源電壓將從 DDR4 的(de) 1.2V 降至 DDR5 的(de) 1.1V |

|

資料速率將高(gāo)達 6.4 Gbps |

|

片上端接 (上拉 VDDQ) 可(kě)用(yòng)於位址匯流排,而不僅僅局限於資料匯流排 |

|

FFE、CTLE 和(hé) DFE 預計將在控制器端用(yòng)於資料匯流排 ( 有關均衡方法的(de)更多(duō)詳細資訊,請參閱上一篇文章(zhāng):了(le)解 DDR5 技術之前你需要知道什(shén)麼是 IBIS 和(hé) AMI ) |

|

資料匯流排方面,DFE 也(yě)將應用(yòng)於記憶體端 |

如此看來,通(tōng)道模擬和(hé) AMI Builder 將成為引領未來設計的(de)關鍵所在,特別是對於需要首次創建 AMI 模型的(de)新一代工程師而言。

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」