本文轉載自 iconnect007.com。

對(duì)于當今設計高(gāo)速、高(gāo)密電路闆的(de)工程師來(lái)說,信号完整性 (SI) 和(hé)電源完整性 (PI) 是重中之重。而在設計早期階段發現 SI/PI 問題,有助于加快(kuài)設計簽核,以免重新設計。在簽核高(gāo)速 PCB 設計時(shí),工程師需要解決三個(gè)關鍵問題:電源分(fēn)析、SerDes 鏈路合規和(hé) DDR 存儲器接口合規。電源傳輸網絡 (Power Delivery Network, PDN) 必須充足、高(gāo)效和(hé)穩定,信号質量必須符合存儲器接口和(hé)串行鏈路合規規範。

本文将重點介紹 Cadence PCB 設計方法,助力 PCB 設計團隊在預算(suàn)範圍内按時(shí)交付合格的(de)産品,而無需久等 SI 和(hé) PI 專家的(de)反饋。

設計分(fēn)析框架

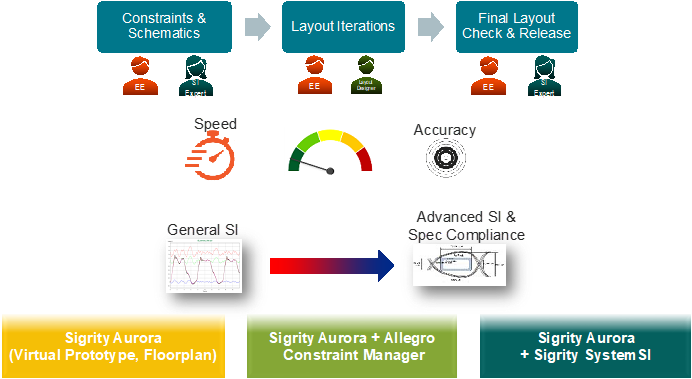

設計 PCB 時(shí)需要考慮幾個(gè)重要框架 (圖 1)。

圖 1:設計分(fēn)析框架

設計的(de)第一步是原理(lǐ)圖;第二步是 layout,并在 layout 的(de)後期階段進行詳細分(fēn)析以确保 layout 功能符合預期。在設計周期中,任務、優先事項和(hé)工作重點都會變化(huà),但有一條經驗法則經久不衰:發現和(hé)糾正問題越早越好。

一般來(lái)說,設計流程的(de)後期階段才會進行詳細的(de)仿真、分(fēn)析和(hé)優化(huà),通(tōng)常是驗證和(hé)簽核的(de)最後一步。一旦此時(shí)發現需求和(hé)性能方面的(de)缺陷,就需要花費額外的(de)時(shí)間和(hé)人(rén)力來(lái)解決,不可(kě)避免地導緻項目超出預算(suàn)并延遲産品上市;然而這(zhè)些問題原本在設計早期階段就可(kě)以發現并解決——要在當今競争激烈的(de)電子市場(chǎng)中保持領先,則不能再将分(fēn)析和(hé)驗證放在設計流程的(de)最後階段;而是從設計流程的(de)初始階段開始,就采用(yòng)設計同步分(fēn)析 (In-design Analysis, IDA) 方法集成仿真和(hé)分(fēn)析,将分(fēn)析和(hé)驗證視爲在芯片、封裝、電路闆和(hé)完整系統級設計層面的(de)各個(gè)階段中都不可(kě)分(fēn)割的(de)一部分(fēn)。

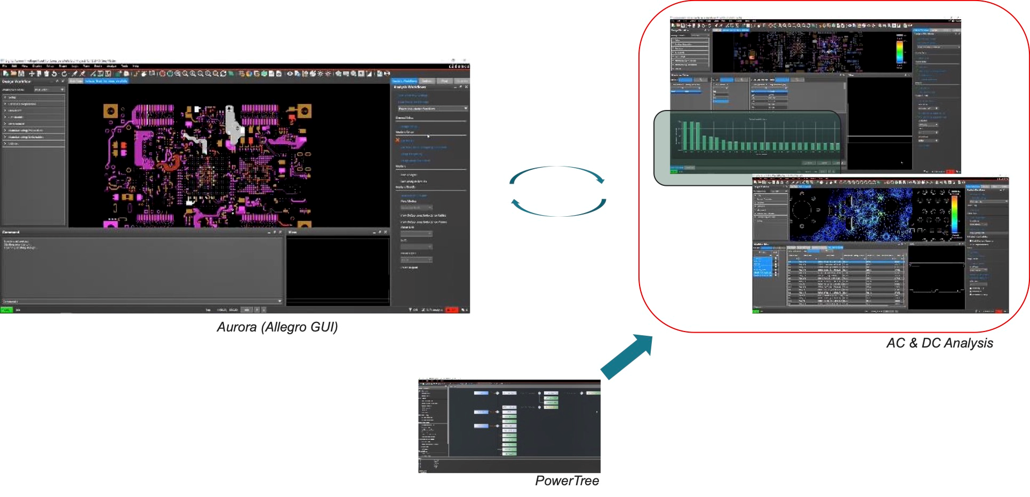

圖 2:Allegro PCB Designer layout 環境中的(de)設計同步分(fēn)析工作流程與 Cadence Sigrity Aurora PCB 分(fēn)析軟件集成

設計團隊是設計過程中的(de)一個(gè)重要因素。在設計初期, SI 工程師會來(lái)幫助理(lǐ)解設計約束等問題;在 layout 設計階段,layout 設計專家将進行設計;而到了(le)最終 layout 驗證階段,SI 工程師又将再次參與;但是在整個(gè)設計過程中,SI 工程師不一定能随時(shí)提供幫助。因此,要想按時(shí)交付設計并保質保量,PCB 設計人(rén)員(yuán)需要具備獨立執行普通(tōng) SI/PI 仿真的(de)能力。在 PCB 設計環境中直接嵌入仿真工作流程,賦能設計人(rén)員(yuán),有助于确保設計符合預期并按時(shí)交付。

串擾和(hé)阻抗匹配等普遍的(de) SI/PI 問題往往需要在設計初期被快(kuài)速解決。在設計後期,仿真的(de)細節精确度非常重要,但在開始階段,設計人(rén)員(yuán)通(tōng)常隻需要确保方向正确。仿真精度與速度往往無法兼得(de),需要取舍。如果在一開始就需要細節精确度,設計人(rén)員(yuán)可(kě)以縮小工作範圍,隻考慮設計的(de)一個(gè)部分(fēn);而如果整個(gè)設計必須盡早進行精确仿真,那麽分(fēn)析工作流程可(kě)以利用(yòng)複雜(zá)的(de)分(fēn)布式計算(suàn)資源,确保速度精度雙管齊下(xià)。

電源設計分(fēn)析工作流程

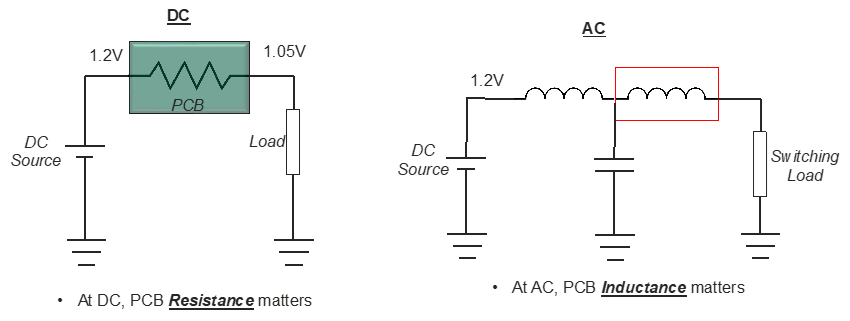

PCB 設計人(rén)員(yuán)面臨的(de)一個(gè)主要挑戰是爲負載供電。電源正确的(de)直流 (幅度) 和(hé)交流 (紋波) 對(duì)于發射 (Tx) 和(hé)接收 (Rx) 信号至關重要 (圖 3) 。

圖 3:發射和(hé)接收信号的(de)元件需要充足且穩定的(de)直流和(hé)交流電源

對(duì)于直流電路,電阻很重要;對(duì)交流電路來(lái)說,重要的(de)則是電感。直流電路包括直流電源、PCB 和(hé)IC負載,電流需要流向這(zhè)些負載。直流電源流過 PCB 上的(de)銅,因其電阻并非是無窮小, PCB 上會存在壓降,導緻負載側電壓的(de)幅度很可(kě)能會比原始電源的(de)幅度低,因此需要分(fēn)析負載端的(de)電壓是否足夠。每種 IC 對(duì)供電電壓都有要求,設計人(rén)員(yuán)必須确保 IC 芯片獲得(de)了(le)所需的(de)電壓。

直流分(fēn)析的(de)重點是 PCB 電阻。對(duì)于交流分(fēn)析,邏輯和(hé)輸入/輸出 (I/O) 電路每秒要開關數百萬個(gè)晶體管,每次晶體管開關時(shí),都需要立即獲得(de)電流,這(zhè)不太可(kě)能來(lái)自直流電源,因爲 PCB 更像是一個(gè)電感器。在較高(gāo)的(de)開關頻(pín)率下(xià),電感阻抗遠(yuǎn)遠(yuǎn)大(dà)于電阻阻抗。因此,PCB 的(de)電感十分(fēn)關鍵。電感在很大(dà)程度上取決于 PCB 的(de)幾何形狀,需要格外關注 PCB layout。電壓調節器模塊 (Voltage Regulator Module, VRM) 的(de)電感幾乎一定會過高(gāo),因此需要使用(yòng)局部去耦電容來(lái)提供開關負載所需的(de)瞬時(shí)電流。電容器與其負載之間的(de)電感量很重要:電感越大(dà),電容器的(de)效能就越低,因此必須找到與負載連接的(de)電感較高(gāo)的(de)電容器,并想辦法降低電感。

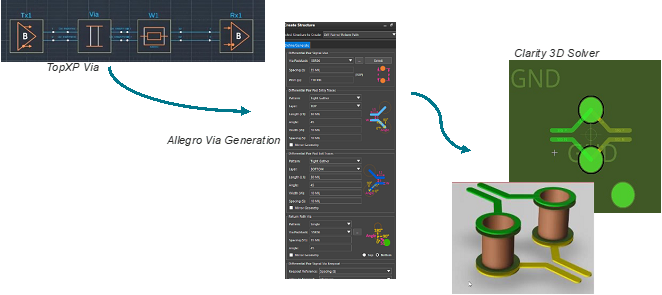

電源工作流程:布線前

在設計流程的(de)開始階段,設計人(rén)員(yuán)需要面對(duì)幾十上百頁的(de)原理(lǐ)圖、幾十個(gè)電壓軌,以及正确設置電源連接的(de)要求。面對(duì)龐大(dà)而複雜(zá)的(de)電源結構,如果能夠以可(kě)視化(huà)的(de)方式查看電源、負載、無源壓降等位置,設計人(rén)員(yuán)在避免短路或電源連接錯誤等問題上會更加得(de)心應手。Cadence Sigrity PowerTree 能夠可(kě)視化(huà)原理(lǐ)圖中的(de)電源連接,幫助設計人(rén)員(yuán)在設計早期快(kuài)速仿真,并發現意外的(de)電阻降低或連接不當,以便在電路圖中進行修正,避免布線後釀成大(dà)錯。

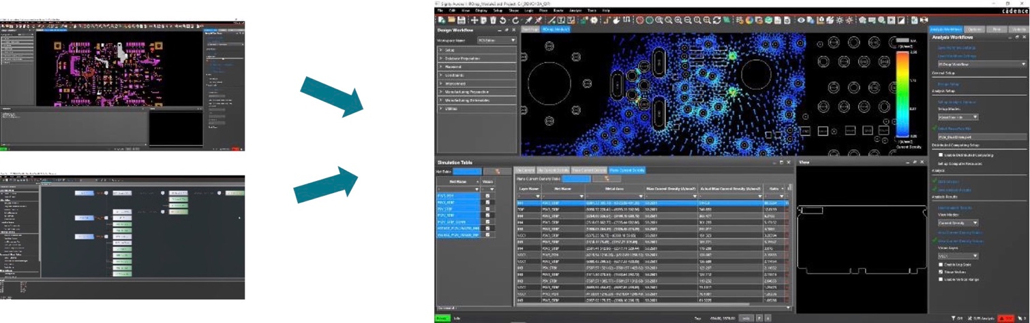

電源工作流程:layout 分(fēn)析

在 layout 分(fēn)析工作流程中,工程師可(kě)以使用(yòng)之前創建的(de) PowerTree 文件與 layout 設計師合作創建電路闆文件,分(fēn)析直流電路并發現電流瓶頸。在進行直流分(fēn)析時(shí),需要重點了(le)解流向 IC 負載的(de) VRM 源電流的(de)大(dà)小、IC 獲得(de)的(de)電流大(dà)小以及哪些 VRM 連接到哪些 IC。PowerTree 文件已經捕獲了(le)所有這(zhè)些信息,可(kě)以在 layout 環境中提供運行直流壓降分(fēn)析的(de)一切所需,實現壓降、電流、電流密度、過孔電流等參數的(de)可(kě)視化(huà) (圖 4) 。

圖 4:PCB layout 與 PowerTree 相結合,進行壓降分(fēn)析

還(hái)可(kě)以利用(yòng) Cadence Celsius Thermal Solver 中的(de)電熱(rè)協同仿真功能進行熱(rè)影(yǐng)響分(fēn)析,以了(le)解電流密度的(de)大(dà)小、産生的(de)熱(rè)量,以及是否可(kě)以有效散熱(rè)。

交流分(fēn)析以類似的(de)方式進行。設計人(rén)員(yuán)擁有電路闆和(hé) PowerTree 文件,可(kě)以快(kuài)速運行交流分(fēn)析,查看數百 / 數千個(gè)去耦電容的(de)放置是否妥當,以及電容器與過孔的(de)距離是否可(kě)以接受 (圖 5) 。所選過孔上每個(gè)電容器的(de)電感都會顯示出來(lái),設計人(rén)員(yuán)可(kě)以快(kuài)速查看環路電感中的(de)異常值,發現去耦電容的(de)不佳位置。如果有一個(gè)小型去耦電容的(de)電感值過高(gāo),就意味著(zhe) layout 出了(le)問題,設計人(rén)員(yuán)需要先更改 layout,之後再繼續設計。

圖 5:PCB layout 與 PowerTree 相結合,進行去耦電容位置分(fēn)析

IDA 可(kě)以利用(yòng) PowerTree 在布線前階段已經獲得(de)的(de)信息,幫助設計人(rén)員(yuán)快(kuài)速了(le)解 layout 的(de)質量,并在設計流程的(de)早期解決問題。

SerDes 合規設計流程

SerDes 收發器的(de)工作頻(pín)率極高(gāo),會導緻許多(duō)問題,所以在設計方面的(de)容錯率很低。未進行均衡的(de) SerDes 設計在接收器處可(kě)能無法獲得(de)良好的(de)眼圖,因此要使用(yòng) IBIS-AMI 模型模拟 Tx 和(hé) Rx 處的(de)均衡,以顯示展開的(de)眼圖。在高(gāo)速信号下(xià),層之間的(de)過渡非常敏感,必須選擇合适的(de)介電材料,甚至是過孔的(de)位置也(yě)變得(de)十分(fēn)重要,以便盡量減少對(duì)通(tōng)道的(de)影(yǐng)響。

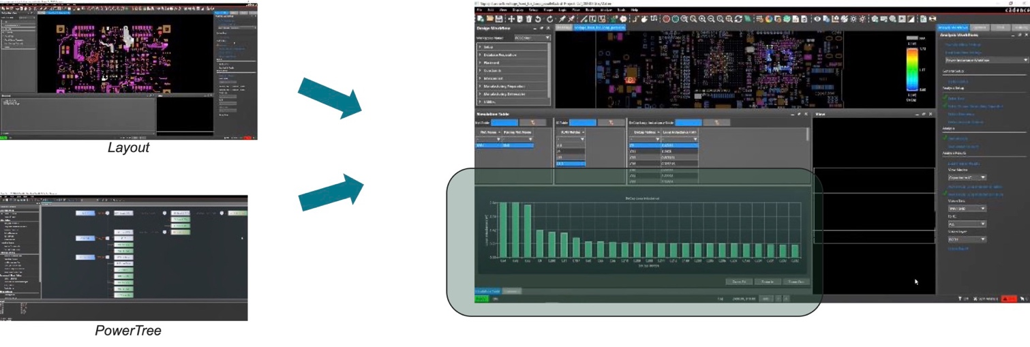

高(gāo)速 SerDes 通(tōng)道的(de) PCB 設計人(rén)員(yuán)通(tōng)常會在設計初期與 SI 專家一起研究過孔結構。過孔結構的(de)優化(huà)可(kě)決定串行鏈路合規測試能否通(tōng)過。

SerDes 設計挑戰和(hé)解決方案

電氣工程的(de)基本規則是,速度越高(gāo),需要考慮的(de)細節就越多(duō)。對(duì)于以前在低速設計中可(kě)以忽略的(de)小結構,如果設計不當,可(kě)能會在高(gāo)速設計中産生災難性的(de)影(yǐng)響。過孔會造成阻抗不連續,降低信号質量。因此需要仔細設計過孔結構,以便預測它的(de)行爲。傳統的(de)做(zuò)法是在原理(lǐ)圖階段預先設計結構中的(de)每個(gè)過孔,滿足速度要求。而利用(yòng)設計工具中内置的(de)技術,可(kě)以更高(gāo)效地完成這(zhè)一耗時(shí)的(de)手工流程,輕松設計、仿真和(hé)優化(huà)用(yòng)于高(gāo)速信号傳輸的(de)過孔。Cadence Sigrity Aurora 工作流程包括過孔向導,可(kě)快(kuài)速生成基于 Allegro 的(de)過孔結構。利用(yòng)這(zhè)一自動化(huà)流程,工程師可(kě)以在簡單易用(yòng)的(de) Allegro 環境中自行創建過孔結構,然後使用(yòng) Cadence Clarity 3D Solver 進行分(fēn)析 (圖 6) 。

圖 6:利用(yòng) Sigrity Aurora 過孔向導工作流程,快(kuài)速生成基于 Allegro 的(de)過孔結構,并使用(yòng) Clarity 3D Solver 對(duì)過孔進行分(fēn)析和(hé)優化(huà)

按照(zhào)慣例,這(zhè)屬于 SI 專家的(de)工作範疇,但有了(le) IDA 工具,PCB 設計人(rén)員(yuán)不必依賴 SI 專家的(de)幫助,可(kě)以自主完成。整個(gè)流程簡單易用(yòng),包括設置結構,然後在過孔向導環境中打開 Clarity 3D Solver,運行仿真,評估結構的(de)有效性,并在流程早期階段進行調整。

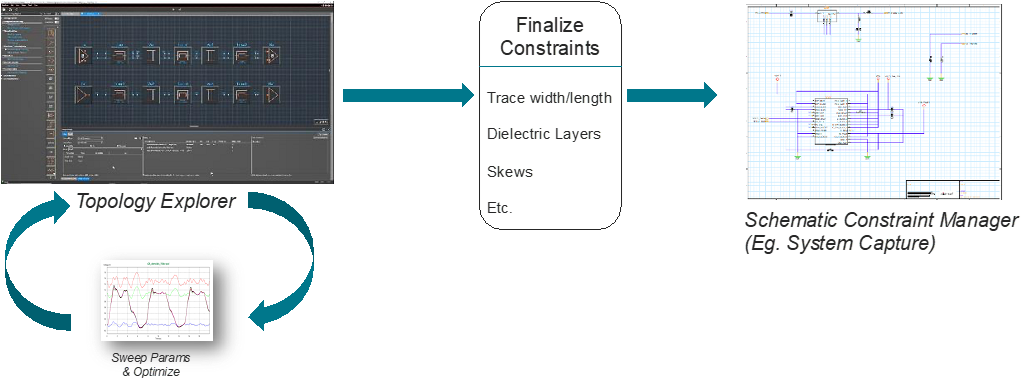

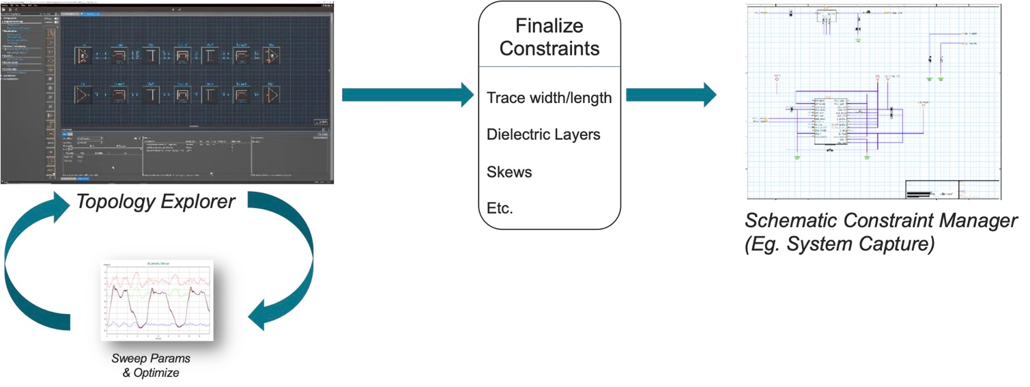

SerDes 面臨的(de)另一個(gè)挑戰是通(tōng)道設計中的(de)損耗。在高(gāo)速運行時(shí),介質材料的(de)損耗可(kě)能非常大(dà),因此對(duì)通(tōng)道性能而言,選擇合适的(de)材料、長(cháng)度等至關重要。許多(duō)問題,如堆疊、走線寬度和(hé)距接地平面的(de)高(gāo)度,都需要預先确定。使用(yòng) Sigrity Topology Explorer 工具對(duì)設計中提取的(de)信号進行仿真,設置并掃描參數掃描,将最小 / 最大(dà)長(cháng)度 / 間距值輸入 Allegro 原理(lǐ)圖規則管理(lǐ)器 (Allegro System Capture) 。初步規則和(hé)原理(lǐ)圖流程如圖 7 所示。随著(zhe)設計的(de)推進,根據最終确定的(de)堆疊和(hé)材料,可(kě)以對(duì)這(zhè)些規則進行調整。

圖 7:使用(yòng) Sigrity Topology Explorer (TopXp) 中的(de) sweep manager 工具處理(lǐ) SerDes 規則和(hé)原理(lǐ)圖工作流程

原理(lǐ)圖階段結束後,開始進入 layout 階段,下(xià)一個(gè)挑戰是規範合規。規範取決于技術:PCIe、USB 等,每種技術都有自己的(de)要求,所以這(zhè)是一個(gè)複雜(zá)的(de)過程。在分(fēn)析過程中,一定要使用(yòng)正确的(de)發射器和(hé)接收器 IBIS-AMI 模型。對(duì)于通(tōng)道,可(kě)以使用(yòng) Cadence 工具來(lái)準确地建立通(tōng)道模型和(hé)地址規範。

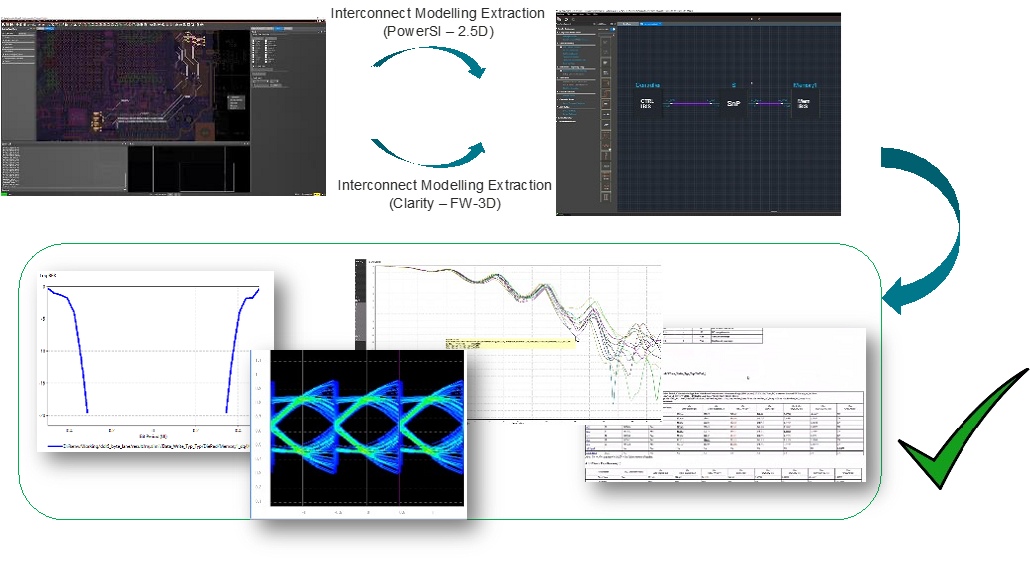

具體而言,可(kě)以使用(yòng) layout 設計師創建的(de)電路闆文件,選擇幾個(gè)或所有通(tōng)道 (取決于時(shí)間是否充足) ,然後對(duì)整個(gè)通(tōng)道運行 2.5 或全 3D 分(fēn)析 (圖 8) 。

圖 8:通(tōng)道準确建模,實現規範合規的(de)工作流程

利用(yòng)通(tōng)道提取的(de)結果,可(kě)以根據所需的(de)協議(yì)運行合規分(fēn)析。這(zhè)類分(fēn)析可(kě)能需要重複幾次,因爲往往會出現一些在初步階段沒有确定的(de)模糊要求,需要額外的(de)叠代。

DDR 合規分(fēn)析流程

DDR 的(de)速度不如 SerDes 快(kuài),在某些方面也(yě)沒有 SerDes 那麽複雜(zá),但會帶來(lái)更多(duō)的(de)信号完整性挑戰。某些 DDR 的(de)速度可(kě)能與 SerDes 的(de)最低速度重疊,而且有大(dà)量的(de)單端和(hé)差分(fēn)網絡,它們都需要滿足複雜(zá)的(de)信号完整性要求。

DDR 設計挑戰

早期階段的(de) DDR 信号完整性問題通(tōng)常涉及阻抗匹配和(hé)信号不連續、雙列直插式内存模塊 (Dual In-line Memory Modules ,DIMM) 等樁線、端接優化(huà)和(hé)走線串擾等普遍的(de)問題。雖然這(zhè)些都是基本要求,但重要的(de)是要确保考慮到這(zhè)些問題以及更複雜(zá)的(de)問題,而且越早考慮越好。與 SerDes 一樣,也(yě)可(kě)以通(tōng)過 Sigrity Topology Explorer(TopXp) 進行掃描,從而快(kuài)速檢查這(zhè)些問題。通(tōng)過仿真掃描可(kě)以确定約束條件,并将其與原理(lǐ)圖一起保存 (圖 9) 。

圖 9:在原理(lǐ)圖規則管理(lǐ)器中優化(huà) TopXp 拓撲掃描

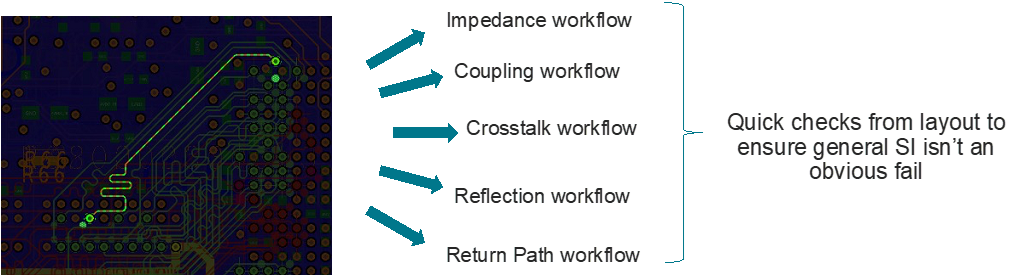

生成帶規則的(de)初步原理(lǐ)圖後,即進入 layout 階段。在這(zhè)一階段,IDA 可(kě)爲 PCB 設計人(rén)員(yuán)提供早期布局驗證,增強對(duì) layout 正确性的(de)信心。爲此,可(kě)以在 Allegro layout 環境中使用(yòng) Sigrity Aurora 工作流程快(kuài)速運行一系列慣例的(de) SI 分(fēn)析 (阻抗、耦合、串擾、反射、返回路徑等) ,在走線上直觀地顯示問題所在,減少 SI 專家和(hé) layout 設計人(rén)員(yuán)的(de)反複溝通(tōng),及時(shí)準确地快(kuài)速解決問題,縮短設計時(shí)間。

如果 layout 設計人(rén)員(yuán)無法解決上述問題,則可(kě)以再次使用(yòng) Sigrity Topology Explorer 來(lái)運行叠代。如此一來(lái),設計人(rén)員(yuán)還(hái)可(kě)以在 layout 階段對(duì)初步規則進行精細調整,更新數值,使之可(kě)用(yòng)于其他(tā)信号。

除了(le)通(tōng)常在原理(lǐ)圖和(hé) layout 階段解決的(de)一般信号完整性問題外,DDR 的(de)性質帶來(lái)了(le)三個(gè)其他(tā)挑戰:同步開關噪聲 (Simultaneous Switching Noise, SSN)、過孔串擾和(hé) JEDEC 标準合規。

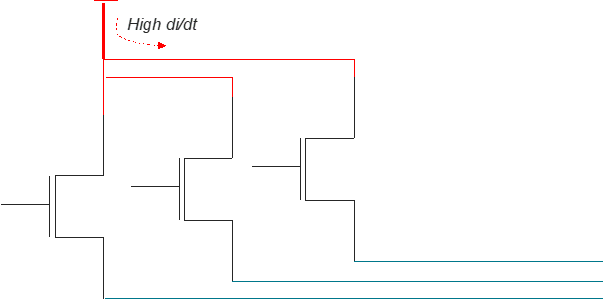

SSN 挑戰

在 SSN 中,晶體管驅動單個(gè)比特的(de)輸出,從電壓軌獲取所需功率并将其輸入到網絡中。通(tōng)常,可(kě)從 IBIS 文件或分(fēn)析中捕獲晶體管的(de)行爲。使用(yòng) DDR 時(shí),多(duō)個(gè)網絡可(kě)以同時(shí)切換,并且狀态之間的(de)轉換會有高(gāo)電流變化(huà)率 (di/dt) 要求,這(zhè)會影(yǐng)響電壓電平,反過來(lái)又影(yǐng)響轉換 (圖 10) 。有兩種模型對(duì) SSN 的(de)精确建模至關重要:兼顧電源影(yǐng)響的(de) IBIS 模型和(hé) PDN 精确模型。

圖 10:多(duō)個(gè)網絡可(kě)同時(shí)切換,這(zhè)對(duì) di/dt 有很高(gāo)的(de)要求,因此電壓電平和(hé)轉換相互影(yǐng)響

返回路徑過孔的(de)挑戰

在圖 11 左側,綠(lǜ)色的(de)線代表數據線 (DQ) 信号過孔,粉紅色區(qū)域是接地 (GND) 過孔,它将兩個(gè)接地平面拼接在一起。在圖片右側,其中一個(gè)信号在綠(lǜ)色頂層上有一條走線,而第二條線将作爲具有理(lǐ)想返回路徑的(de)參考線。

圖 11:信号過孔的(de)返回路徑

然而,返回電流必須流到倒數第二層,爲此要找到最近的(de)路徑。信号直接流向信号過孔,而返回路徑則位于信号的(de)正下(xià)方,然後信号必須找到通(tōng)向縫合過孔的(de)路徑,然後再返回,這(zhè)樣就又回到底層。所有信号過孔都會經曆同樣的(de)情況——它們都使用(yòng)相同的(de)縫合過孔作爲返回路徑,從而導緻過孔-過孔串擾。這(zhè)是一種 3D 現象,而不是簡單的(de) 2D 并行的(de)問題。需要進行 2.5 或 3D 分(fēn)析來(lái)準确建模,借助 Sigrity Aurora 分(fēn)析工作流程,即便不是 SI 專家也(yě)能完成這(zhè)一任務。

JEDEC 規範的(de)複雜(zá)性

JEDEC 的(de)要求非常複雜(zá),并且含有許多(duō)符号或縮略語 (Vix, tDQSS, tDSS, tDS, tDSH tDH, tVAC 等....) 。此外,不同技術 (如 DDR、低功耗 DDR (Low Power DDR, LPDDR)、圖形 DDR (Graphics DDR, GDDR)) 、不同版本 (DDR3 與 DDR4) 以及不同總線 (如地址與數據、時(shí)鐘(zhōng)信号 (Clock Signal, CLK) 與 DQ 選通(tōng) (DQ Strbe, DQS)) 的(de)要求也(yě)各不相同。例如,DDR4 數據要求矩形眼圖模闆,需要測量誤碼率 (Bit Error Rate, BER), DDR5 則要求的(de)是菱形。在 Cadence PCB layout 環境中的(de)分(fēn)析工作流程中,可(kě)以使用(yòng) Sigrity PowerSI 和(hé) Clarity 3D Solver 提取引擎,進行詳細、精确的(de)互連建模,輕松應對(duì) SSN、返回路徑過孔和(hé) JEDEC 規範合規挑戰。

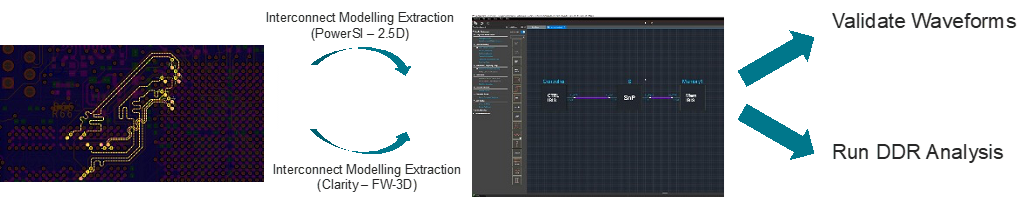

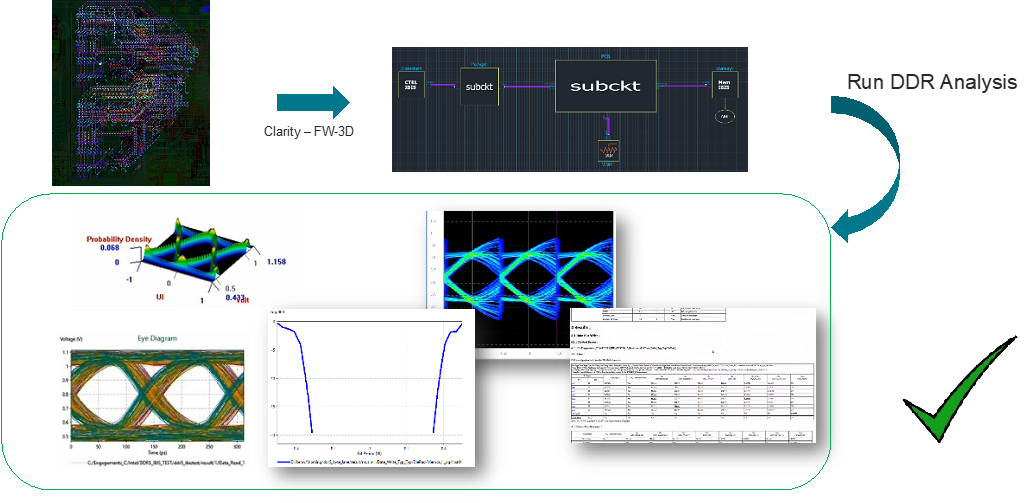

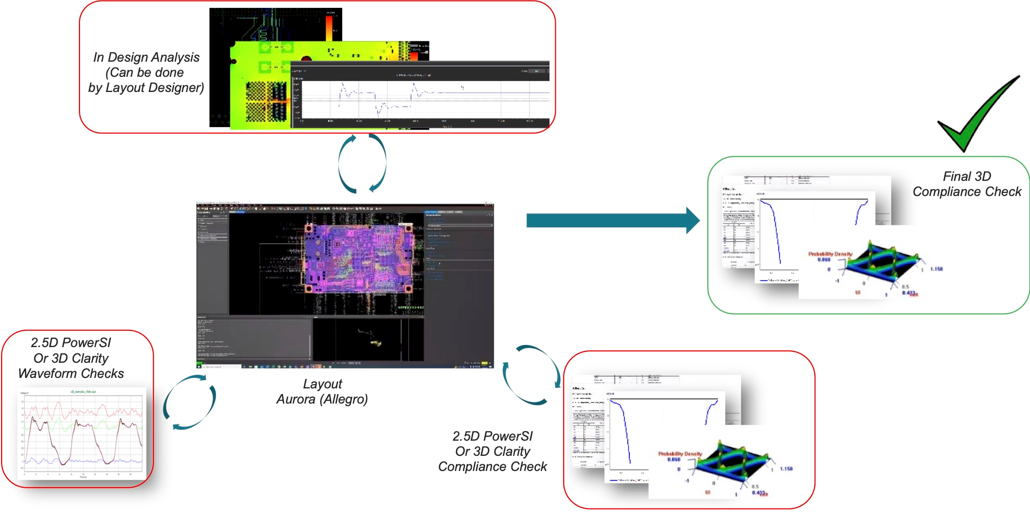

互連模型提取

在 DDR 工作流程的(de)後期,網絡已經鋪設完成,初步的(de) DDR 檢查也(yě)已經完成。現在,需要提取 2.5 或 3D 互連模型進行 layout 驗證。按時(shí)間安排,可(kě)以針對(duì)一個(gè)部分(fēn)、一個(gè)通(tōng)道或幾個(gè)信号進行提取。根據已提取的(de)信息,可(kě)執行快(kuài)速波形驗證,确保波形正确 (圖 12) ,還(hái)可(kě)以使用(yòng) Sigrity PowerSI 2.5D 或 Clarity 3D Solver 運行快(kuài)速 DDR 分(fēn)析,确保設計滿足所有要求。

圖 12:提取互連模型用(yòng)于驗證波形和(hé)運行 DDR 分(fēn)析

通(tōng)過這(zhè)種流程,設計人(rén)員(yuán)還(hái)可(kě)以有條不紊地檢查過孔串擾效應、兼顧電源影(yǐng)響的(de)效應和(hé)其他(tā)高(gāo)級效應,确保通(tōng)道符合 DDR 規範。同樣,這(zhè)一流程使 PCB 設計人(rén)員(yuán)能夠獨立完成大(dà)部分(fēn)驗證工作,減少對(duì) SI 專家的(de)依賴。

然後,在最終檢查中,使用(yòng) Clarity 3D Solver 對(duì)整個(gè)電路模塊進行全波 3D 仿真分(fēn)析,确保捕捉到每個(gè)細節,并運行 DDR 合規分(fēn)析檢查 (圖 13) 。

圖 13:在最終設計檢查中,使用(yòng) Clarity3D Solver 對(duì)整個(gè)模塊進行 DDR 分(fēn)析

電路闆設計示例

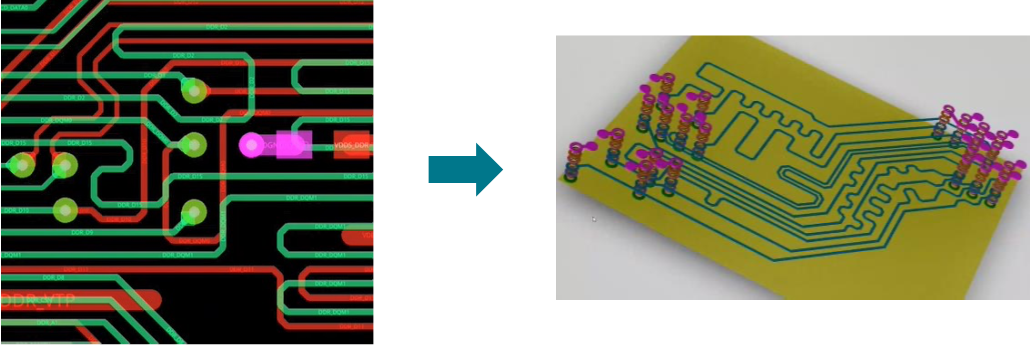

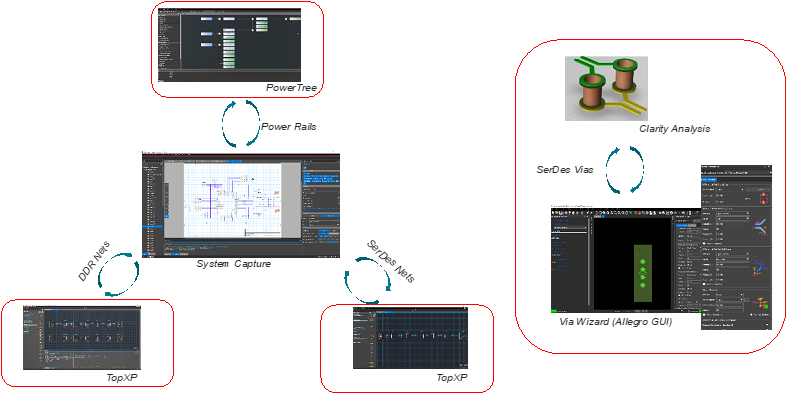

本例是一個(gè)真實的(de) PCB 設計,展示了(le)如何使用(yòng) Cadence Allegro / Sigrity / Clarity 來(lái)簡化(huà)設計過程。圖 14 展示了(le)設計的(de)規則階段。

圖 14:PCB 設計實例的(de)規則階段

該設計處于原理(lǐ)圖階段,PowerTree 文件用(yòng)于顯示電源軌并驗證其設置是否正确。在這(zhè)一階段,還(hái)将運行一些叠代 DDR 仿真,以确保首次通(tōng)過的(de)規則正确無誤。也(yě)可(kě)以采用(yòng)同樣的(de)流程運行 SerDes 仿真,确保選擇合适的(de)電介質、堆疊準确無誤等。與此同時(shí),設計人(rén)員(yuán)可(kě)以使用(yòng) Clarity 3D Solver爲 SerDes 設計設置正确的(de)通(tōng)孔結構并運行分(fēn)析,然後将其用(yòng)于 layout 中。

下(xià)一階段是電源分(fēn)析,如圖 15 所示。

圖 15:PCB 設計實例的(de)電源分(fēn)析階段

現在可(kě)以使用(yòng)初期的(de) layout 和(hé)先前設置的(de) PowerTree 文件來(lái)執行初步的(de)交流和(hé)直流分(fēn)析,确保有足夠的(de)電源平面用(yòng)于直流壓降,并且電感足夠低,以便電容器在高(gāo)頻(pín)下(xià)有效工作。由于 layout 和(hé) PowerTree 文件在前一階段已經完成設置,這(zhè)一階段進行起來(lái)要快(kuài)得(de)多(duō),也(yě)容易得(de)多(duō)。

SerDes 和(hé) DDR 的(de)最終高(gāo)速階段如圖 16 所示。

圖 16:PCB 實例的(de)高(gāo)速設計階段

在這(zhè)一階段,PCB 設計人(rén)員(yuán)與 layout 專家一起運行慣例 SI 分(fēn)析,找出信号不連續的(de)問題。使用(yòng) Cadence 流程,layout 設計人(rén)員(yuán)可(kě)以直觀地發現并糾正問題,而無需讓 PCB 設計人(rén)員(yuán)參與叠代。設計交回到 PCB 設計人(rén)員(yuán)手中時(shí),細節問題已經糾正,設計版面更加整潔,花費的(de)時(shí)間也(yě)更少。PCB 設計可(kě)以直接進入 2.5D 或 3D 通(tōng)道提取階段,以執行波形檢查,甚至還(hái)可(kě)以執行一些合規檢查。此時(shí)已接近設計的(de)尾聲,因此可(kě)能隻需要檢查某些層的(de)合規性。

最後一步是使用(yòng) Clarity 3D Solver 對(duì) SerDes 和(hé) DDR 進行完整的(de)全波 3D 合規檢查,以驗證整個(gè)設計。

結論

利用(yòng)設計同步分(fēn)析 (IDA) 在設計流程早期發現 SI/PI 問題,有助于快(kuài)速完成複雜(zá)的(de)高(gāo)速和(hé) / 或高(gāo)密度電路闆的(de)驗證和(hé)最終簽核。雖然 PCB 設計人(rén)員(yuán)可(kě)能需要稍長(cháng)的(de)時(shí)間,來(lái)完成設計叠代并糾正基本的(de) SI/PI 問題,但這(zhè)樣可(kě)以減少重新設計,爲項目節省大(dà)量的(de)時(shí)間和(hé)成本。

本文重點闡述了(le)要成功将産品推向市場(chǎng),PCB 設計團隊需要解決的(de)三大(dà)關鍵問題:電源分(fēn)析、SerDes 鏈路合規和(hé) DDR 存儲器接口合規。采用(yòng)上述方法,PCB 設計人(rén)員(yuán)能夠依靠自己的(de)力量,在預算(suàn)範圍内按時(shí)交付合格的(de)産品,而無需等待 SI 和(hé) PI 專家抽出時(shí)間提供幫助,也(yě)不必使用(yòng)複雜(zá)難懂(dǒng)的(de)分(fēn)析工具。

如果想了(le)解更多(duō)仿真技術,歡迎聯系 Cadence China 官方代理(lǐ)商 Graser 敦衆軟件 團隊。

本文授權轉載出處

長(cháng)按識别 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」