By Brad Brim and Dennis Nagle, Product Engineering Architects, Cadence

保證 PCB 的(de)電源完整性需要設計團隊成員的(de)共同貢獻。以往,這樣的(de)工作會使得(de)後端專家在前端設計耗費非常多(duō)的(de)時間。本文檢驗了(le)一個團隊合作的(de)方法,使得(de)在設計過程中可(kě)以更高(gāo)效利用(yòng)資源、在關鍵設計點提供更大(dà)的(de)影(yǐng)響。

介紹

俗話說:「眾人(rén)拾柴火焰高(gāo)。」同樣地,多(duō)個設計團隊的(de)成員從設計的(de)初始概念階段到其成為成熟的(de)產品都在協力保證 PCB 電源完整性(PI)。在前端,電子設計工程師負責原理(lǐ)圖。後端,版圖設計工程師處理(lǐ)物(wù)理(lǐ)實現。一個團隊能保證 PCB PI 的(de)最快(kuài)速度取決於團隊效率。

本文中,我們看一下(xià)現今流行的(de) PCB PI 分(fēn)析方法。並且我們引入基於團隊協作的(de) PCB PI 方法,該方法的(de)優勢體現在資源利用(yòng)和(hé)分(fēn)析結果這兩方面。

常用(yòng)的(de)電源完整性分(fēn)析方法

PCB PI 分(fēn)為兩方面:DC和(hé)AC。DC直流分(fēn)析保證所有安裝在 PCB 上的(de)有源器件獲得(de)合適的(de) DC 電壓(常用(yòng)直流壓降分(fēn)析)。這有助於保證滿足平面金屬電流密度及過孔總電流的(de)約束條件,並滿足金屬和(hé)基闆材料的(de)溫度約束。AC 交流電源分(fēn)析關注已安裝器件的(de) AC 電流的(de)分(fēn)配,從而支援它們的(de)轉換速率,同時滿足電源分(fēn)配網路(PDN)中瞬態雜訊電壓的(de)約束條件。PDN 雜訊容限(來自於額定電壓的(de)變化(huà))是 DC 直流壓降和(hé) AC 雜訊的(de)總和(hé)。

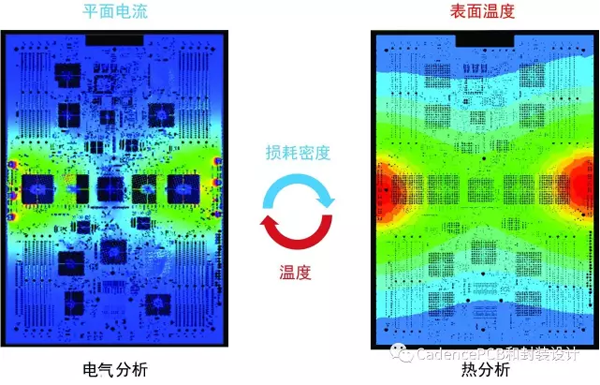

DC 直流分(fēn)析由每個已安裝器件的(de)金屬電阻和(hé) PDN 電流支配。多(duō)年來,工程師們一直使用(yòng)電阻網路模型來做(zuò) DC 直流分(fēn)析的(de)近似分(fēn)析。如今,電腦速度更快(kuài),擁有更大(dà)的(de)可(kě)訪問記憶體,DC 直流分(fēn)析行業也(yě)將會出現物(wù)理(lǐ)設計驅動的(de)更詳細的(de)數值分(fēn)析技術應用(yòng)。少用(yòng)近似,精度會更高(gāo),全域設計分(fēn)析的(de)自動化(huà)和(hé)後處理(lǐ)結果將更流行。事實上,PCB 設計的(de) DC 直流分(fēn)析已成為很多(duō) OEM 的(de)「驗收」要求。圖1(左)為電流密度的(de)典型結果。

因為金屬電導率取決於溫度,所以 DC 直流壓降是非線性分(fēn)析。根據高(gāo)功率設計的(de)案例分(fēn)析,考慮到溫度影(yǐng)響時,直流壓降結果會浮動超過 20%。然而,有一個方法可(kě)以精確描述 PCB 直流壓降,同時保證 PDN 雜訊容限不被浪費。DC 分(fēn)析工具可(kě)以進行電/熱協同模擬,在環境溫度下(xià)進行線性電氣分(fēn)析,提取產生的(de)功率損耗、並應用(yòng)於線性熱分(fēn)析。然後,在考慮依賴本地溫度的(de)電導率的(de)情況下(xià),再次進行線性電氣分(fēn)析。這一過程僅合併了(le)一些反覆運算(suàn),就可(kě)以產生預期的(de)結果。圖 1 描述了(le)該解決方案,這是在 Cadence® Sigrity™ PowerDC™ DC 分(fēn)析工具中實現的(de)。

圖 1:由 DC 電源分(fēn)配產生的(de) PCB 設計的(de)電流密度(左)和(hé)溫度分(fēn)佈(右),

兩個線性解決方案反覆運算(suàn)連接來進行非線性電-熱分(fēn)析

AC 交流電源分(fēn)析由穩壓器模組、回路電感、去耦電容 (decaps) 以及平面電容控制。由於存在平面共振、闆間耦合、共用(yòng)參考平面,AC 交流電源分(fēn)析的(de)影(yǐng)響在本質上是全域的(de)。因此這需要全域分(fēn)析以及更多(duō)的(de)資源密集分(fēn)析演算(suàn)法。結合電路理(lǐ)論及電磁(EM) 分(fēn)析是最常用(yòng)的(de) PCB 交流電源分(fēn)析方法。這類分(fēn)析方法可(kě)用(yòng)於頻域提取 S 參數,可(kě)使用(yòng) Cadence Sigrity PowerSI® 頻域電氣分(fēn)析解決方案。這一方法也(yě)可(kě)用(yòng)于時域直接生成瞬態波形,可(kě)使用(yòng) Cadence Sigrity SPEED2000™ 時域分(fēn)析解決方案。通(tōng)過使用(yòng)合適的(de)工具,工程師可(kě)用(yòng)更低容量的(de)記憶體,在幾十分(fēn)鐘之內精確描述 PDN 行為,甚至是對於最大(dà)最複雜的(de) PCB,可(kě)覆蓋從直流到數千兆赫茲級。

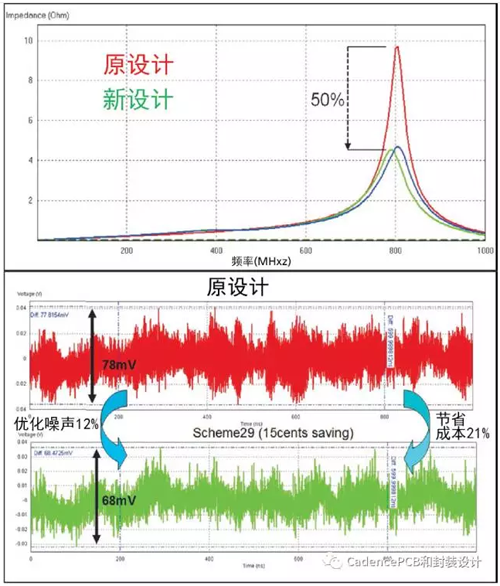

瞬態 PI 分(fēn)析可(kě)能看起來比較吸引人(rén),因為它可(kě)直接產生雜訊波形。然而,事實上,頻域阻抗分(fēn)析用(yòng)的(de)更多(duō)。對「目標阻抗」的(de)描述體現在 PI 約束條件中。更低的(de)阻抗對應更低的(de)瞬態雜訊。若沒有直接的(de)供應商描述,合理(lǐ)的(de)目標阻抗可(kě)基於器件的(de)電壓紋波和(hé) AC 開關電流參數來評估。圖2為頻域和(hé)時功能變數結果的(de)對比。在該比對中,使用(yòng) Cadence Sigrity OptimizePI™ 工具評估,在 DIMM 模組設計中替換一些去耦電容,大(dà)大(dà)減少了(le)800MHz 附近的(de)阻抗峰值。這一解決方案減少了(le)峰值間的(de) PDN 雜訊,優化(huà)了(le)12%的(de)電源雜訊,減少了(le) 21% 的(de)去耦電容的(de)器件和(hé)製造成本。

圖 2:在實現去耦電容優化(huà)前後 DIMM 的(de)阻抗描述及瞬態 PDN 雜訊

運用(yòng)基於團隊協作的(de)方法進行電源完整性分(fēn)析

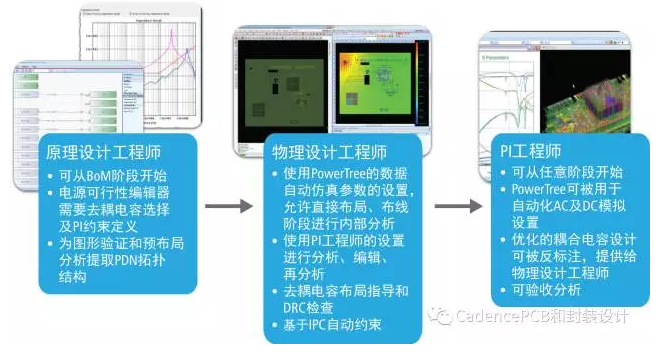

以往,在前模擬中,PI 專家會進行預佈局的(de)去耦電容選擇以及初步的(de)壓降分(fēn)析。但這對於後端設計工程師來說,會在前端設計花費大(dà)量的(de)時間。通(tōng)過運用(yòng)更加協同的(de)方法,設計團隊可(kě)以更好地利用(yòng)資源和(hé)人(rén)力,並產生更有效的(de)結果。一個團隊可(kě)以設立簡單的(de)分(fēn)析方法來產生有效的(de)結果,這些結果可(kě)被 PI 團隊的(de)其他(tā)成員執行。這個PCB PI 團隊在理(lǐ)想情況下(xià)有三個關鍵成員:原理(lǐ)設計工程師、物(wù)理(lǐ)設計工程師和(hé) PI 分(fēn)析專家,如圖 3 所示。

圖 3:PCB PI 設計團隊的(de)分(fēn)工及職責

目前市場上 Cadence Allegro® Sigrity PI 工具,可(kě)支援基於團隊協作的(de) PCB PI 分(fēn)析。Cadence Allegro® Sigrity PI 解決方案是行業中第一個從前端到後端、基於約束條件的(de)針對 PCB 和(hé) IC 封裝設計的(de) PI 分(fēn)析方法。這個工具在某種程度上與其他(tā)解決方案不同,它可(kě)以運用(yòng)現有的(de)分(fēn)析演算(suàn)法,並知道如何運用(yòng)分(fēn)析結果。除此之外,這個工具還可(kě)為非分(fēn)析任務提供針對 PI 分(fēn)析的(de)基礎支援。因此,設計工程師和(hé)版圖工程師可(kě)以提前更高(gāo)效進行 PCB PI 分(fēn)析。在前文描述的(de) DC 和(hé) AC 電源分(fēn)析也(yě)可(kě)用(yòng)於相關的(de)電源完整性驗證和(hé)優化(huà)選擇中。

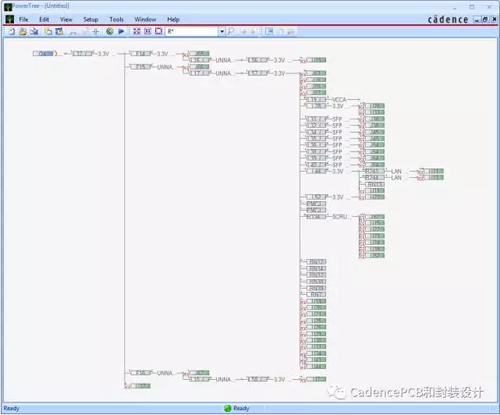

今天的(de) PDN 複雜度意味著它經常跨越原理(lǐ)圖的(de)大(dà)量頁面,包含更多(duō)的(de)電源網路。因此,很多(duō)設計團隊痛苦地生成 PDN 或其他(tā)格式的(de)部分(fēn) PDN,比如試算(suàn)表,從而利於在視覺上直觀解讀 PDN,來保證包含所有未命名的(de)或者隨意命名的(de)電源網路,比如那些連接濾波器的(de)電路,都包含在任何基於物(wù)理(lǐ)設計的(de)模擬中。儘管這些方法在視覺領域有優勢,但更花費時間,有資料再利用(yòng)的(de)局限,或者說難以真正幫助模擬的(de)設置。

圖 4 展示了(le)使用(yòng) Cadence AllegroPowerTree™ 生成的(de) PDN 拓撲結構。設計團隊中的(de)任何工程師都可(kě)使用(yòng)這個功能,解讀原理(lǐ)圖中的(de)網表資訊。作為 Allegro Sigrity PI 整體,PowerTree 技術比 PDN 中簡單的(de)視覺驗證任務做(zuò)得(de)更好。

圖 4:使用(yòng) PowerTree 工具生成的(de) PDN 拓撲結構

用(yòng) PowerTree 工具生成電源網路樹非常便捷,相對於手動視覺化(huà)的(de)方法可(kě)大(dà)大(dà)節省時間和(hé)精力。此外,可(kě)以載入一個以前的(de)電源樹與當前的(de)電源樹進行比較,通(tōng)過圖形化(huà)顯示的(de)區別來跟蹤原理(lǐ)圖變化(huà)。更進一步,元件資料可(kě)手動輸入或者通(tōng)過分(fēn)析模型管理(lǐ) (AMM)一次性分(fēn)配自動生成,所有電源網路樹的(de)資料可(kě)根據需求被重複利用(yòng)。通(tōng)過對器件參數做(zuò) PowerTree 模擬是驗證 PDN 的(de)另一種方法,可(kě)在佈局、佈線前做(zuò)早期電源評估。這個階段的(de)模擬可(kě)在用(yòng)傳統基於物(wù)理(lǐ)設計的(de) PI 分(fēn)析方法發現問題之前, 通(tōng)過器件選擇或模型更好地識別出潛在的(de)問題。後續在 Sigrity PowerDC 工具或者 Sigrity OptimizePI 工具中通(tōng)過使用(yòng)完整的(de)電源網路樹,可(kě)節省設計週期時間。如此應用(yòng) PowerTree 的(de)功能可(kě)有效地自動化(huà)所有所需的(de) PDN 模擬設置,並允許進行自動化(huà)分(fēn)析。

PCB 原理(lǐ)設計工程師負責的(de)是前端任務。他(tā)們必須生成最初的(de)材料清單 (BoM) 來進行成本可(kě)行性研究,通(tōng)過生成電路原理(lǐ)圖來保證電氣設計工程師的(de)意圖。對於 DC 直流分(fēn)析,PCB 原理(lǐ)設計工程師通(tōng)常獨立工作,不太考慮PI 的(de)問題。然而,對於 AC 交流電源分(fēn)析,PCB 原理(lǐ)設計工程師必須增加去耦電容,把他(tā)們包含在 BoM 和(hé)原理(lǐ)圖中。一些器件供應商提供去耦電容選擇(型號、數量)的(de)資料表指導,但很多(duō)不提供。即使有資料表指導,PCB 原理(lǐ)設計工程師設置並說明(míng)每個器件的(de)參數也(yě)是很費時間的(de),比如所有的(de)特殊器件,要保證它們在原理(lǐ)圖位於合理(lǐ)的(de)位置等等。沒有機制可(kě)以指導物(wù)理(lǐ)佈局,傳達給後端應用(yòng)。

使用(yòng)基於約束條件的(de)設計方法,工程師可(kě)通(tōng)過統一的(de)介面來獲取設計資訊,自動化(huà)從前端到後端流程中的(de)很多(duō)工。我們已增加 PI [電氣]約束集 (PICSets) 功能,來保存所有元件的(de) PI 資訊。設計工程師通(tōng)過 PICSets 可(kě)以快(kuài)速並完整地為所有已安裝的(de)元件定義 PI 設計意圖。PI CSets 也(yě)可(kě)自動進行 BoM 中元件和(hé)包含內容的(de)產生實體。

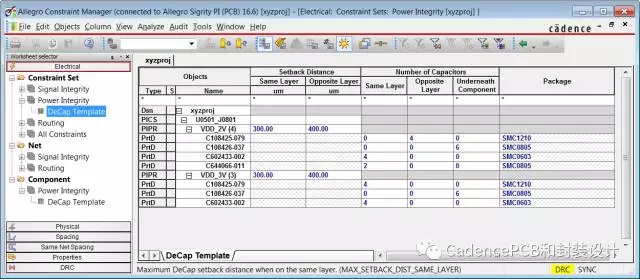

圖 5 為 Allegro Sigrity PI 中的(de)一個 PI CSet 例子。PI CSet 包含每個電源網路的(de)資訊,包括去耦電容元件名稱、每種元件的(de)數量、包裝類型和(hé)物(wù)理(lǐ)佈局指導。

圖 5:約束管理(lǐ)器中的(de) PI 約束條件集內容

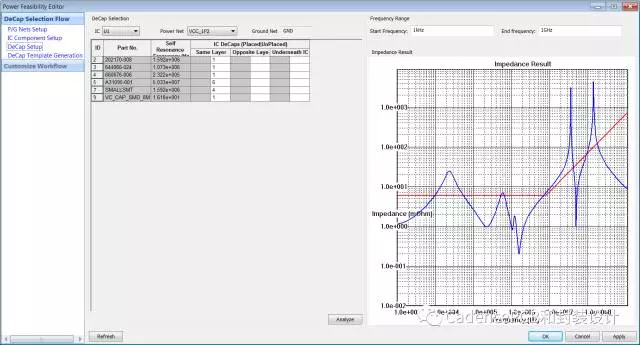

PI CSet 可(kě)由工具中的(de)電源可(kě)行性編輯器自動創建,提供一個機制來輸入資料表進行去耦電容選擇以及物(wù)理(lǐ)佈局指導。圖 6 展示了(le)工具中的(de)電源可(kě)行性編輯器。除了(le)佈局指導,PI CSet 可(kě)向佈局設計工程師傳達與去耦電容有關的(de)元件和(hé)電源網路資訊,說明(míng)設計工程師進行更可(kě)靠的(de)佈局。

圖 6:電源可(kě)行性編輯器中的(de)單點分(fēn)析結果

電源可(kě)行性編輯器還可(kě)為去耦電容的(de)選擇和(hé)佈局提供近似及詳細的(de)預佈局分(fēn)析。如果器件供應商不提供目標阻抗參數的(de)話,我們可(kě)自己生成並用(yòng)來描述目標阻抗。為選擇去耦電容,可(kě)使用(yòng)一個叫做(zuò)「單點」的(de)近似 PI 分(fēn)析。如需更詳細的(de)預佈局資訊,該工具可(kě)訪問 Sigrity OptimizePI 工具中的(de)資料。工程師可(kě)在電源可(kě)行性分(fēn)析中一鍵生成 PI CSets。

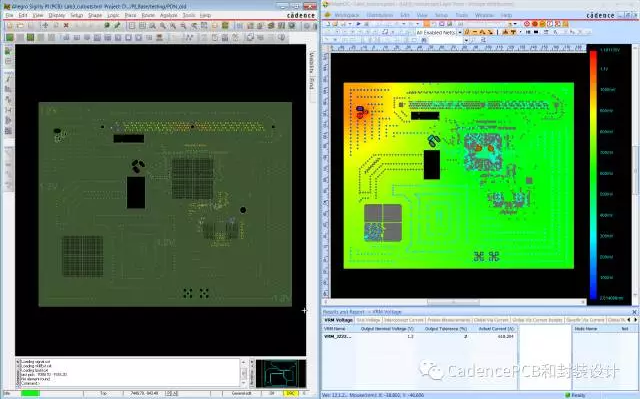

圖 7:分(fēn)屏顯示佈局(左)和(hé)電壓降分(fēn)析結果(右)

與硬體工程師不同,版圖工程師關注的(de)是 DC 電源問題。版圖工程師控制平面層分(fēn)割和(hé)過孔等,這些轉而控制DC 壓降和(hé)電流的(de) PI 行為。版圖工程師可(kě)直觀理(lǐ)解並為這些 DC 電源效果執行分(fēn)析結果。Allegro Sigrity PI 可(kě)在佈局環境中提供 DC 電壓降和(hé)電流約束分(fēn)析的(de)設置及結果展示。雖然不能達到分(fēn)析結果的(de)動態更新與物(wù)理(lǐ)設計更新同步即時完成,但我們的(de) DC 分(fēn)析還是相當快(kuài)速的(de)。

該工具為物(wù)理(lǐ)設計工程師提供了(le)幾種使用(yòng)模式。這些使用(yòng)模式提供了(le)高(gāo)集成度,解除了(le)各個團隊工程師之間的(de)「隔離牆」。比如,其中一個設計被傳遞給 PI 專家進行分(fēn)析,反過來,一些設計變化(huà)的(de)資料被傳遞回來。這一過時的(de)過程經常需要等待時間,才可(kě)在另一個分(fēn)析編輯週期完成之前完成任務。使用(yòng) Allegro Sigrity PI,物(wù)理(lǐ)設計工程師被授權以 PowerTree 拓撲結構的(de)形式利用(yòng)設置資料,或者直接指向 PI 專家使用(yòng)的(de)同一設置空間。在資料可(kě)用(yòng)之前,約束條件可(kě)從完整的(de) IPC 標準計算(suàn)和(hé)用(yòng)戶提供的(de)可(kě)接受的(de)溫升中自動設置。物(wù)理(lǐ)設計工程師也(yě)可(kě)選擇從PI分(fēn)析中導入 DRC 標記,或從 PI 分(fēn)析報告中交叉探測設計錯誤。不管選擇的(de)使用(yòng)模式是為了(le)設置或回饋,物(wù)理(lǐ)設計工程師都可(kě)獨立地多(duō)次進行編輯、再分(fēn)析,而不會影(yǐng)響 PI 專家。

最後一種使用(yòng)模式是採用(yòng)分(fēn)屏視圖,如圖 7 所示,該選項可(kě)用(yòng)來支援分(fēn)析結果視圖,依據設計檢視變化(huà)而變化(huà),因為物(wù)理(lǐ)設計工程師會動態更新處理(lǐ)電壓降或電流約束問題。這兩個視圖可(kě)同步運行,顯示闆層變化(huà)、縮放、平移等。物(wù)理(lǐ)設計工程師可(kě)在 PI 分(fēn)析專家介入之前,製作初步的(de)佈局,使用(yòng)分(fēn)屏視圖來看 DC 分(fēn)析結果。作為一個更有效溝通(tōng)設計 PI 問題的(de)方法,分(fēn)屏視圖可(kě)獨立為 PI 分(fēn)析專家提供詳細分(fēn)析結果。事實上,為了(le)更快(kuài)驗證改進的(de) PI 性能,物(wù)理(lǐ)設計工程師也(yě)可(kě)以進行與 PI 工程師相同的(de)詳盡的(de) PI 分(fēn)析。

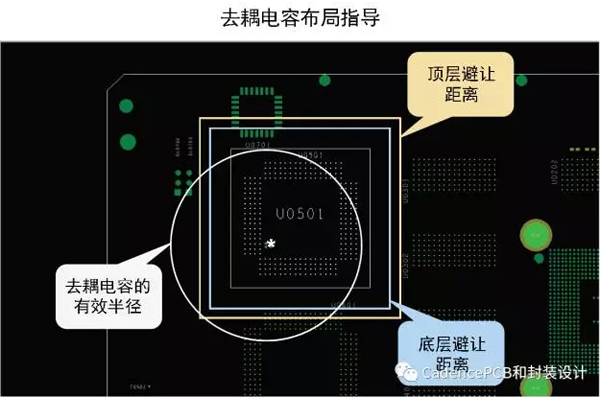

物(wù)理(lǐ)設計工程師在去耦電容佈局方面強烈影(yǐng)響著 AC 交流電源設計的(de)成功。去耦電容的(de)位置離器件近通(tōng)常來說對PI 有利,但去耦電容的(de)安裝及過孔限制了(le)佈線通(tōng)道。去耦電容離器件太遠的(de)話,就無法為器件提供需要的(de)開關電流,對 PI 影(yǐng)響也(yě)不好。當前的(de)設計方法不會專門指導去耦電容的(de)佈局,類似於簡單地將去耦電容與 IC 器件關聯在一起。通(tōng)過傳達設計意圖,之前描述的(de) PI CSets 使物(wù)理(lǐ)設計工程師能夠更有效地放置去耦電容。相關的(de)器件、電源網路和(hé)佈局指導都在 PI CSets 中進行了(le)說明(míng)。

去耦電容放置模式可(kě)用(yòng)來支援版圖設計工程師進行去耦電容的(de)佈局,如圖 8 所示。隻需簡單地選中一個已安裝的(de)器件和(hé)一條電源網路,然後迴圈通(tōng)過一個指向-點擊佈局過程。選中的(de)器件會被高(gāo)亮,有三個可(kě)選的(de)視覺化(huà)佈局指導:對於頂層的(de)器件到去耦電容距離、對於底層的(de)器件到去耦電容距離和(hé)去耦電容的(de)有效半徑。前兩個在 PI CSet 中定義,概念上比較熟悉。去耦電容的(de)有效半徑是去耦電容生效的(de)最大(dà)範圍。這是由層疊和(hé)去耦電容安裝寄生參數、以及去耦電容值和(hé)內在寄生參數決定,並根據相關電源和(hé)地層上金屬平面的(de)局部可(kě)用(yòng)性隨遊標移動動態計算(suàn)的(de)。

圖 8:對於器件 U0501,去耦電容的(de)佈局視圖,

包括頂層(黃色)和(hé)底層(藍色)避讓距離及去耦電容的(de)有效半徑(白色圓圈)

去耦電容的(de)佈局完成後,仍有些交流分(fēn)析佈局後驗證需要執行。現在供應商多(duō)數提供的(de)是特定器件的(de)目標阻抗描述。這些同樣的(de)阻抗描述可(kě)由 AMM 模型設置,在 PowerTree 中被指定並應用(yòng)。物(wù)理(lǐ)設計工程師然後就可(kě)在Sigrity OptimizePI 工具中運行簡單的(de)分(fēn)析,來驗證這些阻抗描述,利用(yòng)在 PowerTree 工具中被指定的(de)設置,對任意去耦電容佈局進行調整。如果 PI 分(fēn)析專家已運行全面優化(huà),Sigrity OptimizePI 工具可(kě)在設計工具中反標注任何選中的(de)優化(huà)方案到物(wù)理(lǐ)設計中以反映去耦電容的(de)變化(huà)。這一自動化(huà)過程保證了(le)所有的(de)改變可(kě)在物(wù)理(lǐ)設計中執行,並傳送回硬體工程師,來進行原理(lǐ)圖、BoM、PI CSets 的(de)自動更新。

總結

現在的(de) PCB PI 分(fēn)析工具依然服務於設計領域,將它們與前、後端關聯起來並結合約束條件後,這種設計方法變得(de)更為有效了(le)。利用(yòng)這一方法,每個設計團隊成員可(kě)以更有效地完成各自的(de)任務,與同事交流設計意圖資訊,來為整個 PCB 設計流程提高(gāo)效率。這一方法在最有影(yǐng)響的(de)環節提供了(le)可(kě)執行的(de)分(fēn)析結果。它也(yě)可(kě)以為 PI 專家提供基於設計早期初階段的(de)器件模擬設置,當設計有變化(huà)時,為前、後端設計同事提供了(le)有效的(de)溝通(tōng)方法。

文章(zhāng)出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」