如今,設計複雜(zá)性和(hé)空間限制迫使設計師采用(yòng)創新的(de)解決方案。将晶粒置于空腔内是一種最常見也(yě)最有效的(de)技術,如果您是爲汽車行業或微波 / 電信領域設計應用(yòng),那麽則很有可(kě)能也(yě)使用(yòng)過這(zhè)種技術。Allegro Package Designer Plus 提供一整套工具集,适用(yòng)于各個(gè)流程,從空腔設計到特定空腔的(de)設計規則檢查 (DRC),再到制造。

在本文中,我們将詳細探討(tǎo)體育場(chǎng)型開放空腔式封裝的(de)引線接合步驟:

1. |

将晶粒置于體育場(chǎng)型開放空腔内 |

|---|---|

2. |

定義“金手指”,并對(duì)晶粒進行引線接合 |

3. |

設置空腔組裝檢查,檢查組裝問題并查看 DRC |

4. |

查看 3D 模型并檢查 DRC |

步驟 1:将晶粒置于體育場(chǎng)型開放空腔内

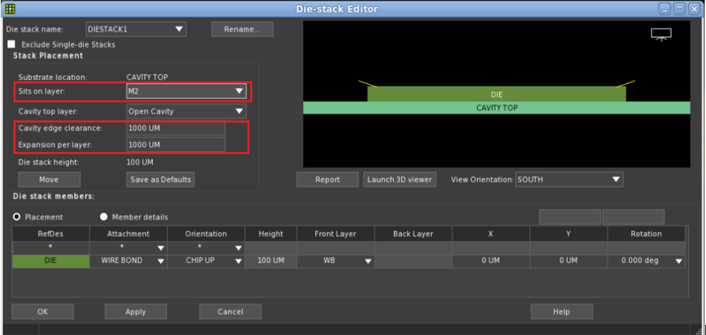

使用(yòng) Die-stack Editor 可(kě)以輕松将晶粒置于空腔内:

|

選擇 Edit – Die Stack,打開 Die-Stack Editor。 |

|---|---|

|

從下(xià)拉列表 Sits on layer 中選擇層。 |

|

設置空腔邊緣間隙和(hé)每層的(de)擴展值,制造體育場(chǎng)型開放空腔。 |

應用(yòng)這(zhè)些變更設置,可(kě)在設計中自動創建體育場(chǎng)型開放空腔。還(hái)會在創建空腔的(de)層上标明(míng)不允許布線的(de)區(qū)域,并在頂部基闆層标明(míng)不允許放置器件的(de)限制區(qū)。

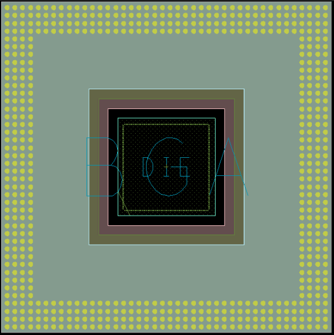

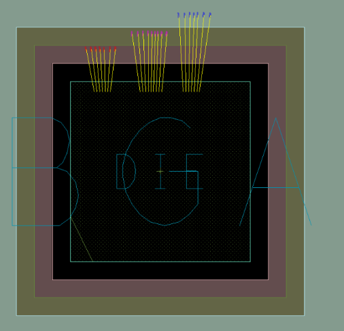

下(xià)圖展示了(le)在空腔中放置晶粒的(de)過程。根據間隙和(hé)擴展值創建體育場(chǎng)型開放空腔。Die-stack Editor 中的(de)報告也(yě)會更新,顯示與空腔有關的(de)變更。

步驟 2:晶粒引線接合

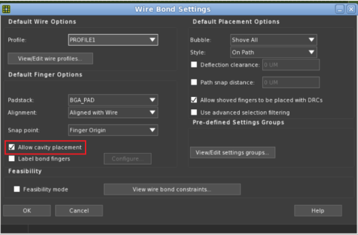

要開始引線接合,首先要在空腔内定義“金手指”:

|

選擇 Route – Wire Bond – Settings。 |

|---|---|

|

在 Wire Bond Settings 對(duì)話(huà)框中,選擇 Allow cavity placement 選項,再點擊 OK。 |

該選項允許在“内部”層創建“金手指”。 |

|

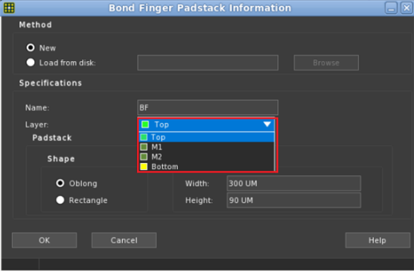

要開始引線接合,選擇 Route – Wire Bond – Add。 |

|---|---|

|

添加引線接合時(shí),在 Options 窗(chuāng)格中點擊 Add,以定義一個(gè)新的(de)金手指焊盤。 |

Bond Finger Padstack Information 表格随即打開,可(kě)在下(xià)拉列表中看到可(kě)選用(yòng)的(de)内部層。

|

選擇其他(tā)内部層,或是繼續使用(yòng)相同的(de)層,在 Bond Finger Padstack Information 表格中點擊 OK。 |

|---|---|

|

重複上述步驟,完成“金手指”放置。 |

下(xià)圖展示了(le) 放置在内部層上的(de)“金手指”。

步驟 3:設置空腔的(de)組裝規則

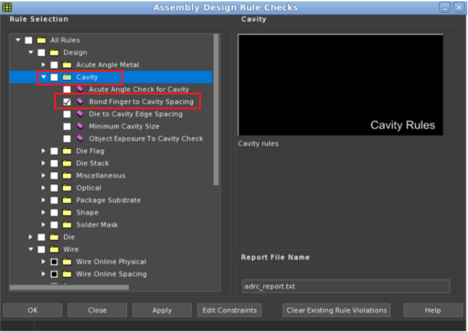

對(duì)于特定于引線接合的(de)空腔設計,有多(duō)種組裝規則。要選擇和(hé)應用(yòng)這(zhè)些規則,請通(tōng)過 Manufacture – Assembly Rules Checker 打開 Assembly Design Rules Checks 對(duì)話(huà)框。在 Cavity 類别下(xià)啓用(yòng) Bond Fingers to Cavity Spacing 約束條件,然後點擊 OK。

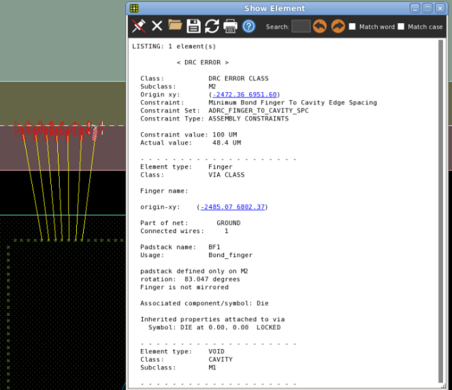

批處理(lǐ) DRC 流程會運行并生成報告。可(kě)以在設計中看到 DRC 标記,表示違反檢查規則。使用(yòng) show element 命令并選擇一個(gè)标記,查看違反約束的(de)細節。

對(duì)于特定于空腔的(de)引線接合設計,有更多(duō)組裝檢查,位于 Wire Spacing Assembly 規則選項下(xià)。

※ Note:需要搭配 Sip Layout Option

步驟 4:查看 3D 模型和(hé) DRC

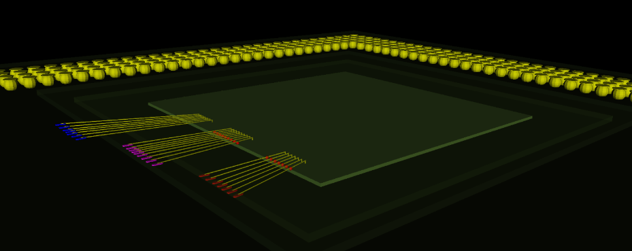

3D Viewer 支持空腔設計。運行 View ─ 3D Model,啓動 Cadence 3D Viewer。設置 3D DRC 規則,在設計中驗證 DRC。下(xià)圖展示了(le)空腔中的(de)晶粒,其中“金手指”是落在不同層上面。

結論

Allegro Package Designer Plus 提供了(le)一套全面的(de)功能,可(kě)成功創建帶空腔的(de)設計封裝。

如果想要進一步了(le)解 Allegro Package Designer Plus 的(de)功能與應用(yòng),歡迎聯系 Cadence China 授權代理(lǐ)商 - 蘇州敦衆軟件。

譯文授權轉載出處 (Graser 協同校閱)

長(cháng)按識别 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」