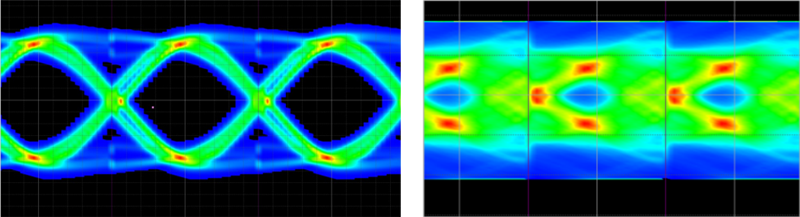

隨著產品設計的(de)多(duō)樣性,對高(gāo)速規格需求也(yě)不斷增加,我們可(kě)以利用(yòng) Cadence 所設計的(de) Workflow 以及實用(yòng)工具,輕鬆設定好端到端的(de)高(gāo)速訊號模擬,並藉由所生成的(de)眼圖和(hé)浴盆曲線快(kuài)速掌握傳輸通(tōng)道對訊號的(de)影(yǐng)響。

Cadence 新一代訊號完整性與電源完整性 (SI/PI) 解決方案 – Sigrity X 提供模擬速度和(hé)設計處理(lǐ)量高(gāo)達 10 倍的(de)效能,亦提供跨不同分(fēn)析工作流程的(de)無縫轉換,從而簡化(huà)詳細系統級 SI/PI 分(fēn)析之設置時間的(de)全新使用(yòng)者經驗,使得(de) PCB 與 IC 封裝工程師可(kě)合併端對端、多(duō)結構、多(duō)闆系統 (從傳送端到接收端,或供電端和(hé)受電端) 設計,追求 SI/PI 簽核成功。

本次 Workshop 視頻將傳授如何使用(yòng) Sigrity X 中的(de) Topology Workbench 工具分(fēn)析 SerDes 通(tōng)道模擬並優化(huà) EQ 參數以獲得(de)最佳通(tōng)道性能。

| 視頻 節點 | 課程內容 |

|---|---|

00 : 00 : 01 |

本場議題介紹和(hé)大(dà)綱說明(míng) |

00 : 01 : 48 |

Topology Workbench 介紹 |

00 : 03 : 00 |

Workbench 涵蓋功能說明(míng) |

00 : 05 : 25 |

Topology Explorer / SystemSI 高(gāo)速介面訊號模擬 |

00 : 07 : 17 |

SerDes 架構簡述 |

00 : 09 : 36 |

高(gāo)速序列傳輸範例 |

00 : 10 : 29 |

通(tōng)道模擬 : Pre-Sim / Post-Sim |

00 : 11 : 24 |

Pre–Sim 流程要點 |

00 : 15 : 10 |

Post–Sim 流程要點 |

00 : 20 : 00 |

完整 SI 方案 - Allegro + Clarity + SystemSI |

00 : 21 : 47 |

案例演示 : Pre-Sim 通(tōng)道模擬 |

00 : 49 : 49 |

案例演示 : Post-Sim 通(tōng)道模擬 |

00 : 59 : 03 |

總結 |