本文要點

|

PCB 走線的(de)電感決定了(le)接收的(de)串擾強度。 |

|---|---|

|

PCB 互連設計的(de)一大(dà)挑戰是保持系統阻抗,同時(shí)減少串擾,因此需要降低走線的(de)電感。 |

|

設計人(rén)員(yuán)需要使用(yòng)數值工具和(hé)合适的(de)分(fēn)析公式來(lái)計算(suàn) PCB 走線的(de)電感。 |

電路模型的(de)作用(yòng)

一流的(de) PCB 設計和(hé)分(fēn)析工具無需根據電路模型來(lái)檢查阻抗、噪聲和(hé)其他(tā)效應。不過,電路模型有助于描述 PCB layout 中各種複雜(zá)功能和(hé)電氣行爲。例如,基于基礎無源元件構建的(de)電路模型 (RLC 電路) 可(kě)以描述串擾造成的(de) EMI 、噪聲敏感性等一系列現象。

串擾通(tōng)過兩種機制耦合:電容和(hé)電感。如果想減少互連之間的(de)串擾,就需要知道各自的(de)電感值。計算(suàn)地平面上方走線有好幾種簡單的(de)方法,如微帶線或帶狀線的(de)電感計算(suàn)。若論更高(gāo)級、更精準的(de)方法,則需要用(yòng)到多(duō)種技術,尤其是考慮到系統中的(de)信号損耗時(shí)。

走線形成了(le)具有一定電感的(de)導體環路

地平面上方走線電感的(de)計算(suàn)公式

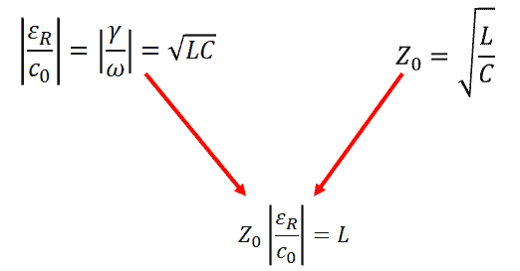

要計算(suàn)微帶線或帶狀線走線電感,首先要計算(suàn)走線特性阻抗和(hé)信号在走線上的(de)傳播延遲。這(zhè)兩個(gè)參數與地平面上方走線的(de)電感和(hé)電容直接相關。走線特性阻抗、傳播延遲、電感、電容和(hé)損耗之間的(de)關系可(kě)通(tōng)過電報方程确定。

以下(xià)兩個(gè)方程用(yòng)于計算(suàn)無損耗傳輸線的(de)電感和(hé)電容。隻需将方程相乘,即可(kě)得(de)出電感值:

地平面上方走線的(de)電感方程

需要注意的(de)是,該公式隻适用(yòng)于特定類型的(de)傳輸線,即沒有任何介質損耗、輻射損耗或趨膚效應損耗的(de)傳輸線。但這(zhè)一模型仍然有應用(yòng)價值,适用(yòng)于一切傳輸線或準 TEM 波導,包括:

|

地平面上方的(de)表層微帶線。 |

|---|---|

|

内層兩個(gè)地平面之間的(de)帶狀線。 |

|

共面波導和(hé)模式選擇波導。 |

所有上述形式的(de) PCB 互連都位于某些地平面之上或之間,可(kě)以測量或計算(suàn)其阻抗。隻要知道互連器件的(de)特性阻抗 Z0 和(hé)介電常數,就可(kě)以根據上述方程确定電感值 (忽略損耗)。

實際情況:數字信号是寬帶信号

上述 (計算(suàn)電感的(de)) 方法在客觀上存在問題:數字信号實際上是寬帶信号,但是 PCB 基闆中的(de)色散會導緻傳播延遲,阻抗也(yě)會成爲頻(pín)率的(de)函數,即使在可(kě)以忽略走線直流電阻的(de)高(gāo)頻(pín)下(xià)也(yě)是如此。此外,由于趨膚效應和(hé)粗糙度,銅也(yě)會産生損耗。因此,不能随意選擇一個(gè)頻(pín)率來(lái)計算(suàn)阻抗和(hé)電感。

如何獲得(de) Z0 值

如果隻選擇單一頻(pín)率,并且忽略損耗,我們仍然可(kě)以從以下(xià)來(lái)源獲得(de) Z0 關于結構的(de)函數:

|

IPC-2142 标準包含帶狀線和(hé)微帶線阻抗的(de)經驗公式。 |

|---|---|

|

教科書(shū)中列有使用(yòng)保角映射法确定的(de)标準公式。Brian C. Waddell 的(de)《輸電線路設計手冊》(Transmission Line Design Handbook) 中列出了(le)最全面的(de)走線阻抗公式。 |

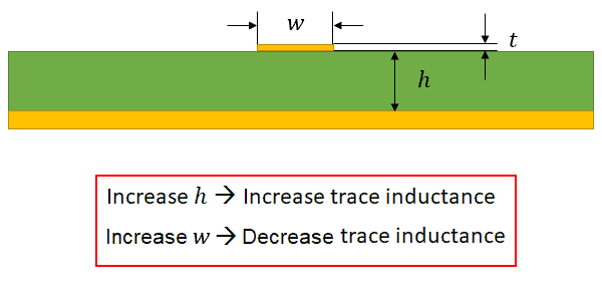

然後,可(kě)以使用(yòng)計算(suàn)出的(de)阻抗來(lái)得(de)出電感。對(duì)于 PCB 表層上的(de)走線,介電常數爲“有效”介電常數。該值通(tōng)常通(tōng)過用(yòng)于計算(suàn)阻抗的(de)公式給出。直觀地說,我們應該已經看到,走線離接地平面較遠(yuǎn)時(shí),走線和(hé)地平面形成的(de)環路就更大(dà),如下(xià)圖微帶線走線所示。改變走線的(de)寬度也(yě)會影(yǐng)響電感。

h 和(hé) w 的(de)值決定了(le)走線在地平面上方的(de)環路電感

這(zhè)些計算(suàn)公式針對(duì)的(de)是孤立的(de)傳輸線,并不考慮寄生效應。由于地平面上方走線的(de)阻抗和(hé)電感取決于走線的(de)幾何形狀和(hé)周圍的(de)寄生效應,我們需要更精确的(de)方法來(lái)确定阻抗和(hé)電感。

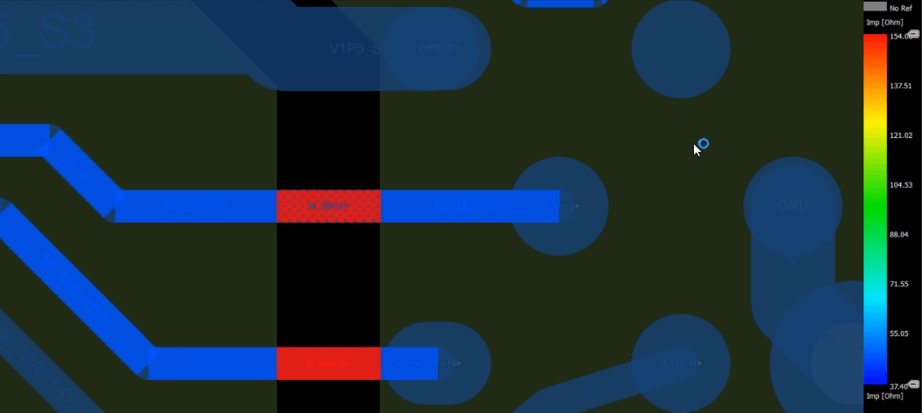

利用(yòng)場(chǎng)求解器計算(suàn)阻抗和(hé)電感

準确計算(suàn)阻抗和(hé)電感的(de)方法之一是使用(yòng)場(chǎng)求解器。這(zhè)些工具無需使用(yòng)電路模型,就能準确考慮到走線幾何形狀和(hé)周圍的(de)寄生效應。如今的(de)高(gāo)級 ECAD 應用(yòng)都包含一個(gè) 3D 場(chǎng)求解器,用(yòng)于計算(suàn)基本傳輸線和(hé)解決複雜(zá)的(de)多(duō)物(wù)理(lǐ)場(chǎng)問題。對(duì)于阻抗計算(suàn),結果通(tōng)常以熱(rè)圖的(de)形式顯示;下(xià)圖列出了(le)一些 DDR3 走線示例的(de)結果。

場(chǎng)求解器工具可(kě)以确定走線沿其長(cháng)度方向的(de)阻抗。然後,可(kě)以使用(yòng)該值和(hé)介電常數來(lái)确定接地平面上方走線的(de)電感

并非所有的(de)場(chǎng)求解器都能計算(suàn)高(gāo)達 GHz 頻(pín)率的(de)銅粗糙度,而這(zhè)一參數對(duì)于 PAM-4 互連、微波光(guāng)電子、汽車 / 無人(rén)機雷達等技術以及其他(tā)涉及極高(gāo)頻(pín)率的(de)領域非常重要。不過,随著(zhe)高(gāo)級産品的(de)功能不斷擴展,未來(lái)将使用(yòng)标準銅粗糙度模型來(lái)計算(suàn)高(gāo)頻(pín)下(xià)的(de)趨膚效應阻抗。

Cadence Sigrity PowerSI 可(kě)以計算(suàn)阻抗和(hé)電感,其提供了(le)完整 IC 封裝或 PCB 的(de)快(kuài)速、準确和(hé)詳細的(de)電氣分(fēn)析。使用(yòng) Sigrity PowerSI 電磁 (EM) 場(chǎng)解算(suàn)器技術,設計人(rén)員(yuán)可(kě)以輕松識别走線和(hé)通(tōng)孔耦合問題。

Cadence Clarity 3D Solver 是一款 3D 電磁 (EM) 仿真軟件工具,用(yòng)于設計 PCB、IC 封裝和(hé) IC (SoIC) 系統設計的(de)關鍵互連。采用(yòng)領先的(de)分(fēn)布式多(duō)重運算(suàn)技術,Clarity 3D Solver 能夠提供近乎無限制的(de)求解容量和(hé) 10 倍的(de)求解速度,從而高(gāo)效解決更龐大(dà)、複雜(zá)的(de)結構問題,讓設計人(rén)員(yuán)在設計 5G、汽車、高(gāo)性能計算(suàn) (HPC) 和(hé)機器學習(xí)應用(yòng)系統時(shí),以業界标準的(de)準确度解決最複雜(zá)的(de)電磁 (EM) 挑戰。

本文授權轉載出處

長(cháng)按識别 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」