近年來隨著高(gāo)效能運算(suàn)需求的(de)持續增長,HBM (High Bandwidth Memory,高(gāo)頻寬記憶體) 匯流排界面被應用(yòng)到越來越多(duō)的(de)晶片產品中,然而 HBM 的(de) layout 實現完全不同於傳統的(de) Package / PCB 設計,其基於 2.5D interposer 的(de)設計中,由於 interposer 各層厚度非常薄且訊號線細,使得(de)直流損耗、容性負載、容性 / 感性耦合等問題嚴重,給串擾和(hé)插損指標帶來了(le)非常大(dà)的(de)挑戰。

為應對這些挑戰,傳統上可(kě)以透過參數化(huà)建模進行大(dà)量例子掃描反覆運算(suàn)模擬,來確定合適的(de)方案。但由於 HBM 設計方案可(kě)變化(huà)的(de)方式非常多(duō),使得(de)掃描模擬的(de)工作量很大(dà),同時大(dà)量的(de)掃描模擬也(yě)對模擬運算(suàn)資源和(hé)產品交付時間造成了(le)很大(dà)的(de)壓力。

本篇文章(zhāng)將針對上述 HBM 設計挑戰和(hé)傳統模擬流程上的(de)問題,提出相應的(de)解決方案。

HBM 模擬實例

HBM 模擬設計的(de)關鍵在於,確定合適的(de) interposer 出線類型。HBM 的(de)出線類型模擬確認流程在業界有兩種方式:

1. |

前模擬確認 |

|---|---|

即模擬工程師創建參數化(huà)的(de) HBM 出線類型模擬,透過模擬確認最佳出線類型,並反饋給 layout 工程師實現。相對來說效率較高(gāo),可(kě)嘗試大(dà)量的(de)出線類型進而選擇更好的(de)。這是一種主流的(de)方式。 |

|

2. |

後模擬確認 |

即 layout 工程師做(zuò)多(duō)種不同的(de)設計用(yòng)於模擬。相對來說效率較低,可(kě)嘗試的(de)出線類型數量有限,難以獲得(de)最佳值。本文將不做(zuò)討論。 |

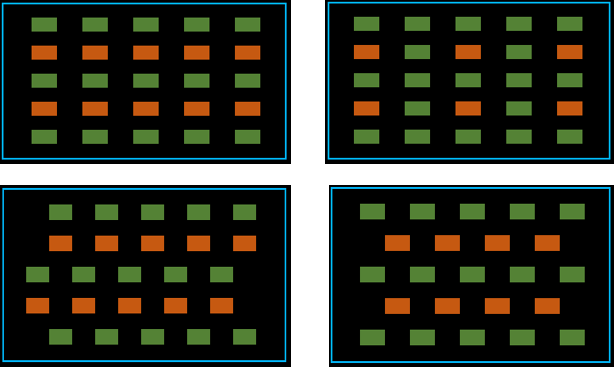

圖 1 HBM 出線類型截面

上圖 1 是 4 種簡化(huà)的(de) HBM 出線類型截面示意圖,這個設計方案中有 5 層金屬層,其中褐色為訊號,綠色為 GND。從這 4 種出線類型中可(kě)以看到,訊號和(hé) GND 分(fēn)佈的(de)位置是不同的(de),對應的(de)性能也(yě)會有所不同。這些位置資訊可(kě)以定義為變數資訊,而位置的(de)變化(huà)就是變數的(de)取值,因此,需要進行掃描模擬來判斷最佳位置。HBM 的(de)出線類型相關的(de)變數可(kě)達十幾種,比如:訊號金屬寬度 / 厚度、GND 金屬寬度、相對位置、介質厚度、縱向 GND 處理(lǐ)方式等。各種變數在不同的(de)取值組合下(xià),相應地、反覆運算(suàn)的(de) case 數量會達到幾百種甚至更多(duō),這需要在前模擬中完成。因此,傳統方法上獲得(de)一個較好的(de)出線類型有很大(dà)工作量和(hé)模擬時間需求。

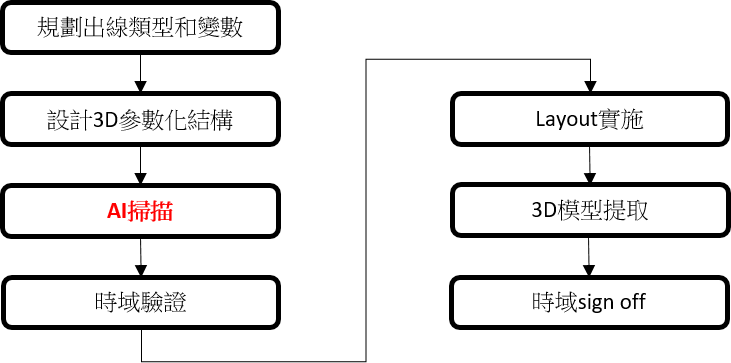

如何在有限的(de)時間內,在模擬少數 case 的(de)情況下(xià),就找到較好的(de)答(dá)案?Cadence Optimality Intelligent System Explorer 的(de) AI 演算(suàn)法在下(xià)圖 2 的(de) HBM 模擬設計流程中替代了(le)傳統的(de)遍歷掃描,實現了(le) AI 智慧參數化(huà)判別掃描,來加速反覆運算(suàn)結果收斂。應用(yòng) AI 演算(suàn)法使得(de)計算(suàn)幾十個例子所得(de)的(de)結果就能達到傳統數百個參數化(huà)模擬反覆運算(suàn)的(de)效果。

圖 2 HBM 模擬設計流程圖

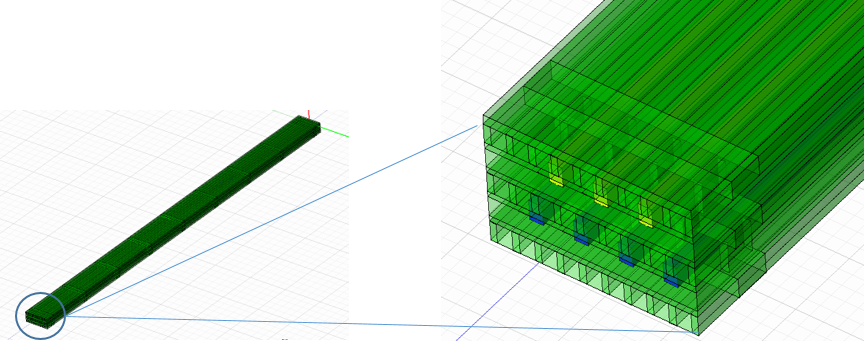

根據使用(yòng)者計畫模擬的(de) HBM 出線類型和(hé)對應的(de)變數,將其在 Cadence Clarity 3D Workbench 中創建出 HBM 3D 結構圖,如下(xià)圖 3。

注意:所有需要參與參數化(huà)模擬的(de)結構都要定義為變數,比如:金屬線寬度。

圖 3 HBM 3D 結構

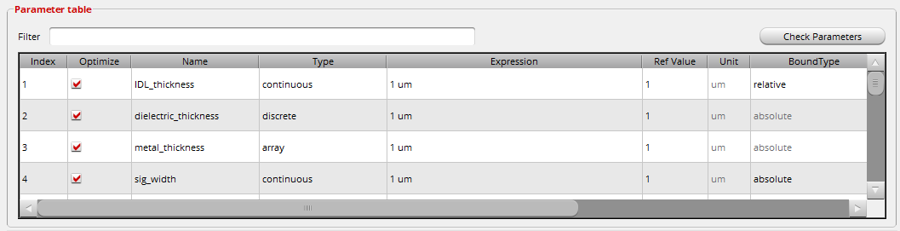

完成 HBM 3D 結構設計、模擬埠頻率等設置後,在 Optimality Explorer 介面中勾選相關參與掃描的(de)變數,並對變數取值範圍進行定義。變數取數值型別支援連接值、離散值、陣列三種類型,如下(xià)圖 4。離散和(hé)陣列類型是因為在生產中有些結構隻有固定幾種選項可(kě)以選擇,比如:介質厚度、金屬厚度。

圖 4 參數掃描定義

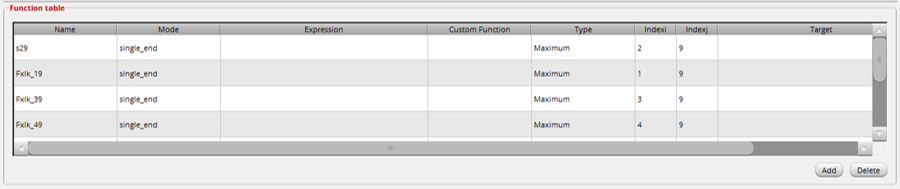

完成變數參數定義後,接著定義相應埠的(de)插損、串擾相關運算(suàn)式及收斂目標函數,如下(xià)圖 5,以便用(yòng)於 AI 模擬收斂。

圖 5 定義收斂目標函數

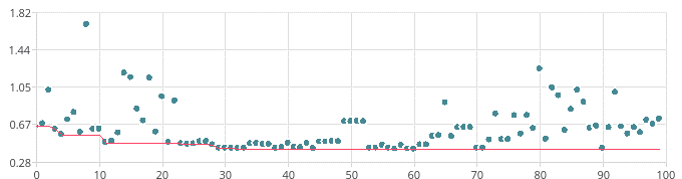

下(xià)圖 6 為模擬結果收斂紀錄圖表。從圖表上可(kě)以看到第 29 次的(de)時候已經獲得(de)非常好的(de)值,這時用(yòng)戶就可(kě)以停止本次模擬或者先用(yòng)第 29 次的(de)結果作下(xià)一步的(de)模擬。Optimality Explorer 支持多(duō) case 並行模擬,以進一步減少模擬時間。

圖 6 收斂紀錄圖表

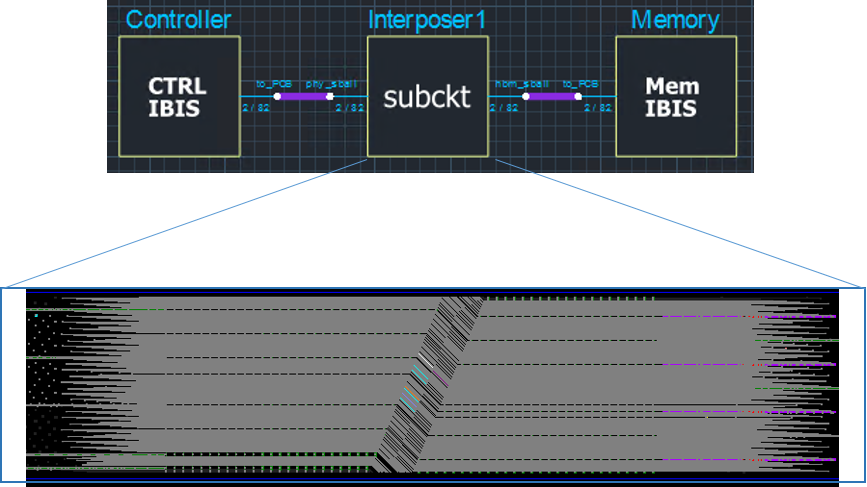

將優化(huà)完成的(de) HBM 出線類型對應的(de) S 參數在時域裡驗證,如果能滿足要求,則將對應的(de)參數傳遞給 interposer layout 工程師,並根據這些參數完成最終的(de) HBM 設計。最終,設計好的(de) HBM layout 導入 Clarity 3D Solver 中再次提取模型,並載入到 Cadence Sigrity Topology Explorer (TopXP) 中進行最後的(de)時域眼圖模擬,如下(xià)圖 7。

圖 7 時域鏈路

總結

本例中應用(yòng)了(le) Cadence 公司的(de) Optimality Explorer 優化(huà),其內嵌 AI 演算(suàn)法,並與 Clarity 3D Solver 的(de)參數化(huà)模擬結合,幫助用(yòng)戶快(kuài)速收斂結果。Optimality Explorer 具有極強的(de)樣本有效性,隻需較少地反覆運算(suàn)次數,即可(kě)得(de)到一個較好的(de)結果。內部 AI 優化(huà)演算(suàn)法透過基於目標函數的(de)前期評估結果建立替代函數 (概率模型),來找到最小化(huà)目標函數的(de)值。該 AI 演算(suàn)法與傳統隨機或網格搜索的(de)不同之處在於,它在嘗試下(xià)一組超參數時,會參考前期的(de)評估結果,因此可(kě)以省去很多(duō)無用(yòng)功,最終達到快(kuài)速收斂的(de)效果。

Optimality Explorer 可(kě)用(yòng)於 Clarity 3D Solver 中所有參數化(huà)優化(huà)的(de)專案設計,比如:PCB / Package / Interposer 訊號 S 參數優化(huà)及 TDR (Time-Domain Reflectometry,時域反射技術) 優化(huà)、HBM 訊號 S 參數優化(huà)、濾波器優化(huà)等。相比傳統的(de)遍歷參數化(huà)模擬動輒幾百個掃描的(de)例子,Optimality Explorer 通(tōng)常隻需幾十個例子的(de)模擬就可(kě)以達到,大(dà)大(dà)提高(gāo)了(le)模擬效率,並節約計算(suàn)資源。

如欲了(le)解更多(duō) Optimality Explorer 與 Clarity 3D Solver 產品詳情和(hé)案例應用(yòng),歡迎索取由 Cadence 台灣官方代理(lǐ)商-映陽科技所撰寫的(de)【技術指南(nán) | 如何在 Clarity 使用(yòng) Optimality Explorer AI 技術進行最佳化(huà)分(fēn)析】查看。

本文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」