By Vincent Wu, Graser

【 電路可(kě)靠度設計 】系列專題 主要探討電路設計上常見的(de)可(kě)靠度問題和(hé)如何在設計創建初期應用(yòng)一些自動驗證分(fēn)析工具,幫助設計開發團隊降低在可(kě)靠度需求上所花費的(de)時間與人(rén)力,確保最終產品能供提供符合市場所需性能和(hé)產品壽命。

該系列共兩篇,上一篇 [ 自動檢測潛藏電路設計錯誤 ] 內容主要在闡明(míng)電路設計可(kě)靠度的(de)重要性,以及如何運用(yòng)電路邏輯檢測功能自動快(kuài)篩一般難以檢測到的(de)電路設計錯誤。 而本篇重點則會用(yòng)實際範例說明(míng)如何使用(yòng) 電應力分(fēn)析 功能進行零件 Derating 分(fēn)析,快(kuài)速識別修正任何壓力過大(dà)的(de)零組件避免 EOS 發生,快(kuài)速提高(gāo)零件選用(yòng)的(de)可(kě)靠度。

你選用(yòng)的(de)零件「靠」得(de)住嗎?

電路闆上包含數位、類比、RF 和(hé)機構件等各類元件成千上萬且複雜,而對其可(kě)靠度要求也(yě)愈趨嚴格。儘管大(dà)部分(fēn)的(de) ODM / OEM 公司在設計初期就會收集各類零件的(de)模型或故障率規格表進行分(fēn)析,進而減少了(le)因零件可(kě)靠度不足而必須重新設計的(de)機率。 但因零件種類的(de)複雜性、缺乏自動化(huà)分(fēn)析工具以及在難以取得(de)零件模型的(de)情況下(xià),這對一個系統級電子產品的(de)可(kě)靠度評估是極具挑戰性的(de)任務。

而 EOS (Electrical overstress, 過度電性應力) 更是電子設備發生故障的(de)常見原因之一。 因此,在製作 PCB 之前的(de)零件 Derating 分(fēn)析非常重要。

電應力分(fēn)析 - 獨賣特點搶先看

工欲善其事,必先利其器。

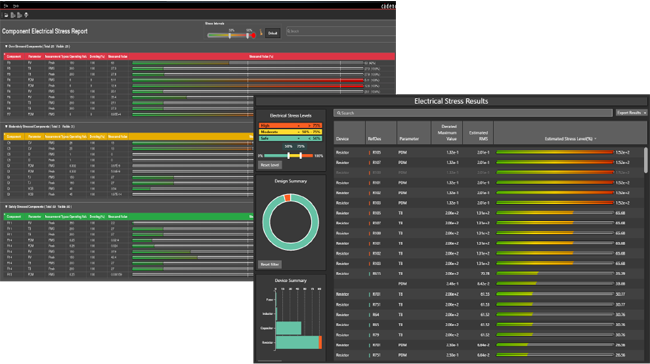

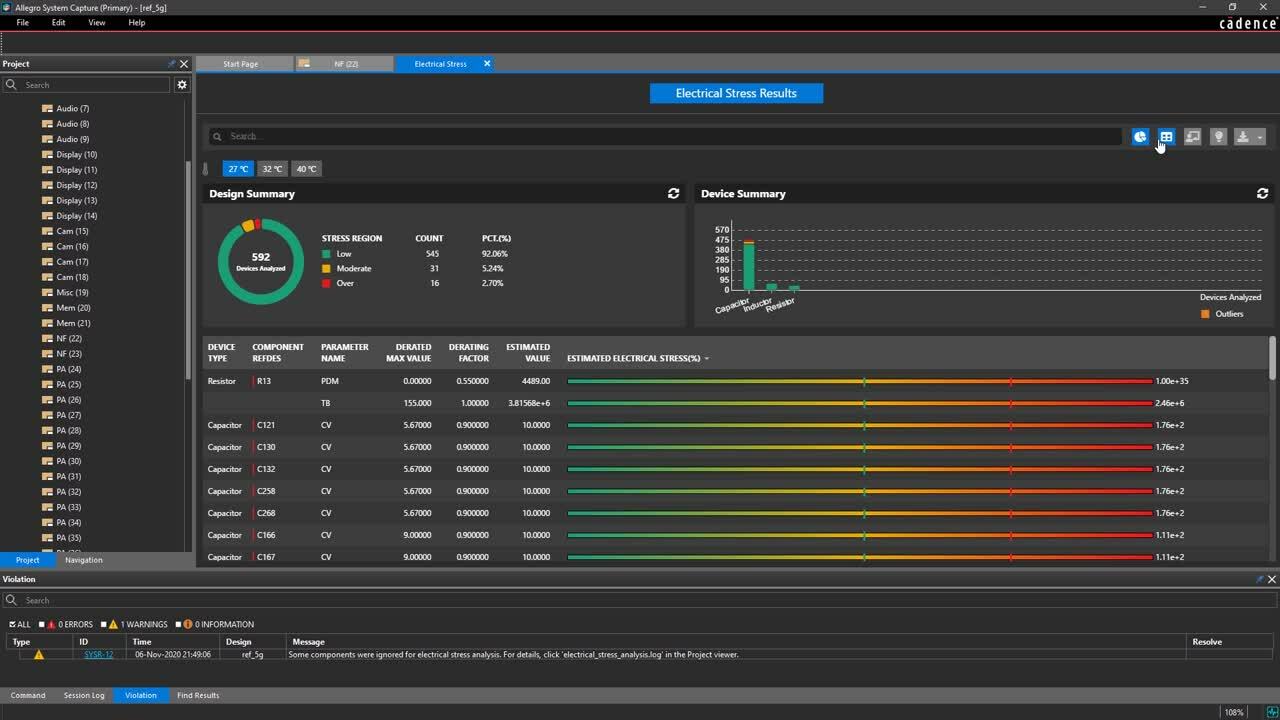

無論你的(de)設計有多(duō)複雜, Cadence Allegro System Capture 17.4 的(de) 電應力分(fēn)析 (Analyze Electrical Stress) 功能,可(kě)毫不費力地模擬整個電路,透過讀取零件屬性中的(de)關鍵欄位以及電路圖中的(de)用(yòng)戶自定義屬性來幫助你快(kuài)速地完成 Component Derating Report,取代目前轉出 BOM 後再將零件分(fēn)類使用(yòng) Excel 或第三方軟體來計算(suàn)各個零件 Derating 的(de)冗長耗時流程,快(kuài)速識別任何壓力過大(dà)的(de)零組件進行替換,提高(gāo)整個零件選用(yòng)的(de)可(kě)靠度,達到減少重新設計和(hé)縮短產品驗證週期。

下(xià)方影(yǐng)片將帶你快(kuài)速透視 Allegro System Capture 的(de)電應力分(fēn)析特點。

( 中文字幕 / 英文配音(yīn) )

溫馨提醒 : 可(kě)點擊影(yǐng)片下(xià)方設定圖示, 在 Captions 中選擇國語, 開啟中文字幕觀看

想進一步知道完整設定及操作密技?

歡迎填寫下(xià)方索取表,索取 「 零件電應力分(fēn)析全攻略 」 技術指南(nán),共 9 頁。

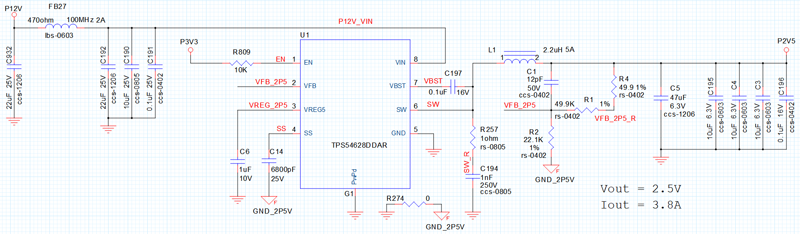

本指南(nán)將以 12V 轉 5V 壓降電路為範例 (圖一),詳解如何運用(yòng) 電應力分(fēn)析 功能,自動檢測快(kuài)速篩查 零件降額 (Derating) 上的(de)潛在問題,以更精確的(de)評估零件規格是否能符合整個系統的(de)可(kě)靠度要求。

更多(duō)電路可(kě)靠度設計相關文章(zhāng)

|

|

|---|---|

|

|

|

|

|