電子工程師尼古拉·特斯拉 (Nikola Tesla) 曾聲稱自己發明(míng)了(le)一種帶電粒子束投影(yǐng)儀——或者用(yòng)科幻術語來說——離子炮 (ion cannon)。這是一種防禦性武器,可(kě)以在一個國家周圍形成一堵力場牆。

儘管,特斯拉從未成功建造起這樣一堵牆,但該結構會激發起一股使人(rén)敬畏的(de)力量。想像一下(xià),高(gāo)高(gāo)的(de)柱子支撐著近球形圓頂。特斯拉的(de)方案表明(míng),柱子將圍繞一股離子流,而球形圓頂在塔的(de)周圍始終保持電荷。如果一架敵機出現在 200 英裏以外,一台像大(dà)炮一樣的(de)光(guāng)束槍就會從頂部探出,以排斥力擊落敵機。

這聽起來很酷,但是卻遜色於 PCB 的(de)漏鬥設計。

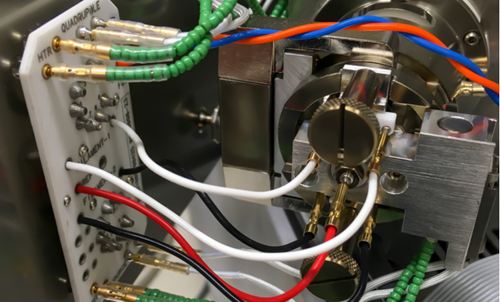

20 世紀 90 年代,首次開發電焊金屬電極堆時,漏鬥就形成了(le)。帶有整合平面電極的(de)標準六層PCB也(yě)被用(yòng)作信號分(fēn)配網路。平面電極由嵌入絕緣平面的(de)非屏蔽電極組成。設計平面電極時,保持電極表面與周圍平面齊平。

新的(de) PCB 技術使現代六層 PCB 漏鬥設計由標準 PCB 設計過渡到可(kě)捲曲漏鬥軟性電路闆。使用(yòng)軟性 PCB 節省部分(fēn)製造成本。

平面漏鬥與推動多(duō)層電路設計

對於平面漏鬥應用(yòng),可(kě)捲曲軟性 PCB 被用(yòng)作信號分(fēn)配電路以及具備漏鬥形狀的(de) 3D 印刷支架。因此,融蝕至軟性 PCB 上的(de)銅平面電極充當漏鬥的(de)環形電極。支架的(de)漏鬥設計將電極置於內徑逐漸減小且聚焦離子雲的(de)序列中,以進行傳輸。此外,漏鬥裝置發揮了(le)1nF電容器的(de)作用(yòng),用(yòng)作諧振 LC 電路的(de)電容性負載。

在容性負載的(de)情況下(xià),漏鬥可(kě)以承受疊加射頻 (RF) 電壓的(de)高(gāo)電場。早期電路中,諧振 LC 電路的(de)頻率隨著儲能線圈電感的(de)變化(huà)而變化(huà)。而 m/z 傳輸視窗(chuāng)的(de)大(dà)小也(yě)隨頻率的(de)變化(huà)而變化(huà)。透過使用(yòng)從現場可(kě)程式邏輯閘陣列 (FPGA) 獲取的(de)邏輯輸入信號引起頻率變化(huà),數位技術的(de)運用(yòng)提高(gāo)了(le)技術準確性。

( 中文字幕 / 英文配音(yīn) )

溫馨提醒 : 可(kě)點擊影(yǐng)片下(xià)方設定圖示, 在 Captions 中選擇國語, 開啟中文字幕觀看

六層 PCB 漏鬥設計和(hé)軟性 PCB 應用(yòng)

借助透過更薄的(de)厚度、更細的(de)線條和(hé)獨特的(de)形狀,軟性 PCB 技術支援應用(yòng)多(duō)層漏鬥的(de)高(gāo)密度電子電路。雖然製造商們還在繼續生產著三層軟性電路 (包含粘膠層),但對高(gāo)階應用(yòng)的(de)需求促進了(le)兩層軟性電路的(de)發展。兩層軟性電路將銅置入聚醯亞胺 (Polyimide) 上,並非粘合劑中,以實現具備極小線間距的(de)極薄 PCB。

為了(le)生產更薄的(de)軟性 PCB,需要設計製造工具,以實現自動接頭彎曲、表面拋光(guāng)、自動覆面和(hé)阻焊層優化(huà)。借助可(kě)支援靈活設計的(de)電子設計自動化(huà) (EDA) 軟體,工程師能夠在加工前、期間和(hé)加工後審查設計,並檢查約束條件。

極薄多(duō)層軟性電路闆的(de)製造過程採用(yòng)了(le)鐳射驅動技術。紫外鐳射鑽孔技術可(kě)以精確地穿過銅和(hé)聚醯亞胺層,鑽出小直徑通(tōng)孔。精確的(de)鐳射製造工藝也(yě)可(kě)實現精確的(de)佈線。鐳射直接成像 (LDI) 可(kě)大(dà)大(dà)提高(gāo)生產均勻細線所需的(de)準確度和(hé)精確度,以及生產過程中矯正聚醯亞胺軟性材料變形的(de)能力。

典型漏鬥設計應用(yòng)

對科學家來說,質譜分(fēn)析法是一種不可(kě)或缺的(de)手段,但是質譜分(fēn)析法的(de)功能依賴于先進的(de) PCB 技術。我們先來談一談這個技術和(hé) PCB 漏鬥設計的(de)作用(yòng)。

失去或獲得(de)一個或多(duō)個電子的(de)原子或分(fēn)子帶有淨電荷,而且是一種離子。磁場可(kě)以使離子的(de)路徑偏轉。偏轉量取決於離子品質和(hé)離子正電荷數量。因此,攜帶更多(duō)正電荷的(de)離子偏轉量更大(dà)。

研究人(rén)員可(kě)以使用(yòng)質譜分(fēn)析法分(fēn)析蛋白質複合物(wù)和(hé)病毒 (共存於同一體系或空間) 相關離子。透過質譜分(fēn)析法測量正離子的(de)質荷比 (m/z)。透過這種測量方式,科學家們能夠識別未知複合物(wù),測量單個複合物(wù)或成分(fēn)的(de)兆道爾頓品質 (MDa),並瞭解分(fēn)子的(de)結構和(hé)化(huà)學性質。

質譜儀電路系統

分(fēn)析第一步:電離源在質譜儀中將分(fēn)子轉化(huà)為氣相離子。離子加速,使每個離子獲得(de)相同的(de)動能。離子偏轉,根據品質對離子進行有效分(fēn)類。

質譜儀的(de)「品質」部分(fēn)是指品質分(fēn)析儀的(de)使用(yòng) (根據質荷比對離子進行分(fēn)類)。離子檢測,檢測穿過光(guāng)譜儀的(de)離子束。將離子檢測與資料系統相結合,透過質荷比分(fēn)析完成測量。將樣品中發現的(de)離子與其強度進行對比,產生質譜圖和(hé)圖形 (顯示透過 m/z 比比較所獲得(de)的(de)不同分(fēn)子量)。質譜圖中的(de)每個峰都表明(míng) m/z 比中存在一種獨特的(de)成分(fēn)。

射頻離子漏鬥可(kě)以提高(gāo)離子傳輸效率,將離子轉移至質譜儀。射頻漏鬥會將空氣中的(de)離子提取至真空中。光(guāng)譜儀電離室中產生的(de)離子需要一條穿過機器的(de)自由路徑。真空操作可(kě)以排除任何阻礙離子自由運動的(de)空氣分(fēn)子。透過常壓離子化(huà)轉移離子,或者離子從環境壓力轉移到高(gāo)真空環境。隨著離子的(de)轉移,科學家們透過常壓離子化(huà)可(kě)以從溶液中取樣離子。

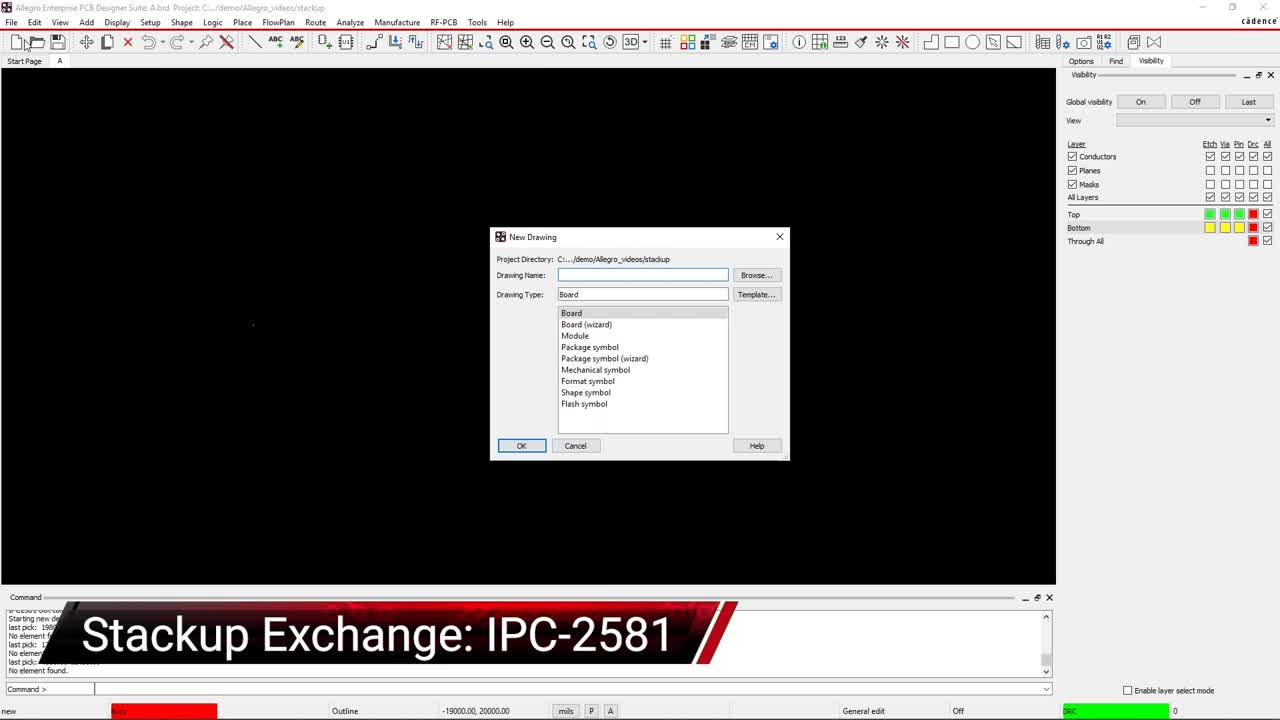

無論是構建先進靈活的(de)PCB設計還是更簡單的(de)電路,Cadence Allegro® 工具都能為您提供最佳的(de) PCB 設計和(hé)分(fēn)析工具。一旦您創建了(le) PCB 佈局,Cadence 會提供一套用(yòng)於佈局後驗證和(hé)類比的(de)信號完整性/電源完整性 (SI/PI) 分(fēn)析工具。

如需了(le)解更多(duō)內容,歡迎聯繫 Cadence 代理(lǐ)商-映陽科技。

譯文 / 視頻授權轉載出處 (映陽科技協同校閱視頻)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」