by Paine Chuang, Graser

全新第三代模擬器 - Xcelium

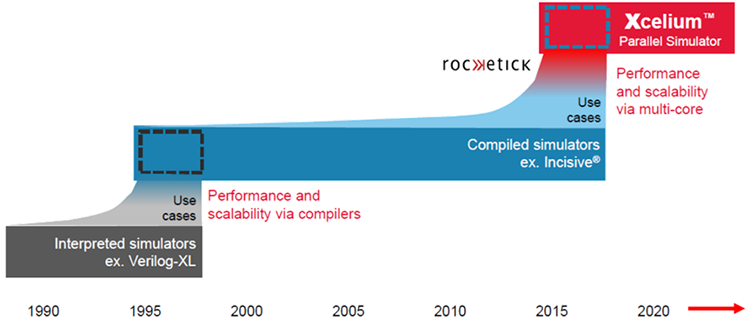

Xcelium 為 Cadence 第三代模擬器。全新模擬器比前一代平均多(duō)出 1.5~2 倍的(de)效能提升,多(duō)核心平行模擬效能平均可(kě)將暫存器傳輸級 (RTL) 設計提升 3 倍、閘層級 (Gate-Level) 模擬提升 5 倍與平行可(kě)測性設計 (DFT) 模擬提升 10 倍。

Cadence Xcelium 模擬器基於創新的(de)多(duō)核心平行運算(suàn)技術,加速系統單晶片 (SoC) 上市時程。相較於前代 Cadence 模擬平台,可(kě)在單核心平均提升 2 倍性能並在多(duō)核心模擬提升 5 倍以上性能。 Xcelium 通(tōng)過生產驗證,已獲得(de)行動、繪圖、伺服器、消費者、物(wù)聯網及汽車領域的(de)客戶所佈署。

針對快(kuài)速 SoC 階層模擬建立多(duō)核心引擎

|

可(kě)自動分(fēn)析設計並選擇最佳的(de)速度配置。 |

|---|---|

|

對暫存器傳輸級 (RTL) 效能平均提升 3 倍、閘層級 (Gate-Level) 模擬平均提升 5 倍、與平行可(kě)測性設計 (DFT) 模擬平均提升 10 倍。 |

針對快(kuài)速 IP 階層模擬重構單核心引擎

|

引擎核心已被廣泛的(de)使用(yòng)案例並通(tōng)過驗證。 |

|---|---|

|

提供比 IES 模擬器更快(kuài)於 2 倍的(de)平均效能。 |

增產功能可(kě)有效提高(gāo)驗證效率

|

創新的(de)引擎核心有效縮短整體專案的(de)時間。 |

|---|---|

|

提供增強智慧型 Exclusion 流程與平行多(duō)核心。 |

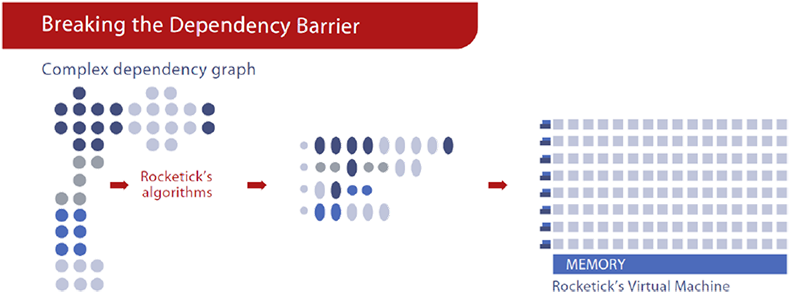

Xcelium 模擬器中提供了(le) Fine-Grained 平行設計,可(kě)加速第二代模擬器進行數天或數周的(de)模擬時間。其獨特的(de)編譯/闡述 (Compile/Elaboration) 過程可(kě)分(fēn)析每個設計的(de)依賴關係圖 (Dependency Graph) 並自動映射 (Mapping) 到最佳核心數,以達到最大(dà)限度地提高(gāo)速度。當然,使用(yòng)者可(kě)以透過命令行調整核心數量。

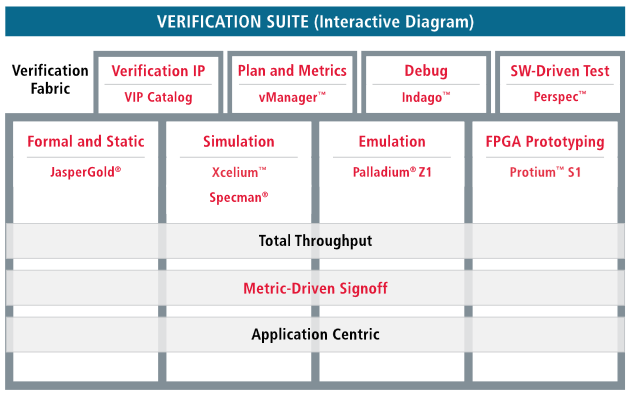

Xcelium 模擬器可(kě)進一步與其他(tā) Cadence 驗證系列 (Verification Suite) 軟體進行整合,該系列軟體由多(duō)個先進的(de)核心引擎技術與驗證架構技術的(de)解決方案結合,從而提升設計品質與生產力,以滿足各種應用(yòng)及垂直市場所需的(de)驗證需求。