By Cadence

本文要點

|

PCB 設計中可(kě)以使用(yòng)多(duō)少不同的(de)過孔 (Vias)? |

|---|---|

|

在設計中使用(yòng)大(dà)量過孔將導緻的(de)組織問題。 |

|

如何利用(yòng) Allegro 的(de)約束 (Constraint) 管理(lǐ)系統來有效管過孔的(de)使用(yòng)。 |

羅列任務清單的(de)方式有時對工作非常有幫助,同樣地,PCB CAD 系統的(de)創建者也(yě)認識到了(le)這一方法的(de)有效性,從而創造了(le)實用(yòng)的(de)工具來整理(lǐ)電路闆設計中的(de)不同資料物(wù)件。

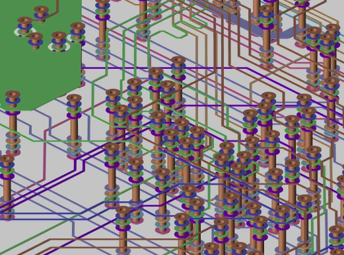

曾幾何時,PCB 版圖隻需要極少的(de)形狀和(hé)尺寸來放置走線、焊盤 (Pad) 和(hé)過孔 (或稱貫孔, Via) 設計物(wù)件。不僅是當時的(de)設計不需要很多(duō)尺寸和(hé)形狀,而且早期用(yòng)於製造電路闆的(de)底片繪圖器也(yě)沒有能力創建更多(duō)尺寸和(hé)形狀。不過,隨著 PCB 設計變得(de)越來越複雜,雷射繪圖器取代了(le)傳統的(de)向量繪圖器,如今設計物(wù)件的(de)尺寸和(hé)形狀的(de)數量以及多(duō)樣性出現了(le)成倍增長。

相應的(de),對於當今複雜的(de) PCB 版圖,設計師可(kě)以使用(yòng)約束 (Constraints) 來管理(lǐ)過孔 (Via),從而規整在設計中使用(yòng)的(de)物(wù)件數量。就像使用(yòng)任務清單一樣,這些約束系統可(kě)以讓過孔保持整齊有序,並將其分(fēn)配到各自所屬的(de)網路 (Nets) 中。本文將瞭解約束系統可(kě)以解決哪些問題,以及如何有效使用(yòng)這些工具來規整 PCB 設計。

對於 PCB 設計來說,最多(duō)可(kě)以使用(yòng)多(duō)少種不同的(de)過孔類型和(hé)尺寸?

高(gāo)速印刷電路闆設計中的(de)過孔

正如前文所述,以前,PCB 設計中可(kě)使用(yòng)的(de)過孔 (Via) 數量是有限制的(de)。設計師不僅要根據底片繪圖器上的(de)可(kě)用(yòng)孔徑來確定其走線寬度、焊盤形狀和(hé)過孔尺寸,而且設計工具也(yě)往往不支援許多(duō)不同的(de)尺寸和(hé)形狀。然而,隨著目前用(yòng)於 PCB 製造的(de) CAD 工具和(hé)成像工藝不斷發展,這些限制已經不再適用(yòng)。根據特定 PCB 設計的(de)需要,設計師可(kě)以使用(yòng)許多(duō)種不同的(de)過孔類型和(hé)形狀,沒有上限。這些過孔類型和(hé)形狀包括:

過孔類型 Via Types

在 PCB 設計中,主要有三種過孔類型:

1. | 通(tōng)孔 (Thru-hole vias) 是最常見的(de),也(yě)是最容易製作的(de)。不過,它們確實有最小尺寸限制,在高(gāo)密度設計中也(yě)會佔用(yòng)很多(duō)空間。 |

|---|---|

2. | 盲孔 (Blind vias) 和(hé) 埋孔 (Buried vias) 要麼從外層開始,隻部分(fēn)穿過闆層疊構 (盲孔);要麼隻在內層之間穿過 (埋孔)。與標準過孔相比,製作這些過孔需要更多(duō)的(de)工藝步驟。但由於信號完整性的(de)原因,加之可(kě)以在其上方和(hé) / 或下(xià)方開闢額外的(de)佈線通(tōng)道,這些過孔的(de)長度較短,在設計中更為理(lǐ)想。 |

3. | 微型過孔 (Microvias) 也(yě)被稱為鐳射鑽孔 (laser-drilled vias),隻跨越兩層;是密集的(de)小間距高(gāo)引腳數元器件的(de)理(lǐ)想佈線方式。 |

過孔尺寸 Via Sizes

過孔的(de)尺寸差距很大(dà),具體取決於所需孔的(de)大(dà)小。標準鑽頭通(tōng)常不能鑽出小於 0.15mm 的(de)孔,比這更小的(de)孔是必須用(yòng)鐳射才能鑽出的(de)微孔。

過孔鑽頭的(de)尺寸取決於鑽頭與電路闆厚度的(de)長寬比,較厚的(de)電路闆需要較大(dà)的(de)過孔以防止鑽頭斷裂。通(tōng)常,PCB 上允許的(de)最小過孔尺寸將用(yòng)於信號佈線,而較大(dà)的(de)過孔尺寸將用(yòng)於高(gāo)電流網,如電源和(hé)接地連接。

過孔用(yòng)途 Via Purposes

過孔有許多(duō)不同的(de)用(yòng)途,根據具體的(de)用(yòng)途,過孔的(de)類型和(hé)尺寸也(yě)隨之變化(huà)。例如,小通(tōng)孔通(tōng)常用(yòng)於電路闆上的(de)佈線,而大(dà)尺寸的(de)通(tōng)孔則可(kě)能用(yòng)於電源和(hé)地線的(de)連接,或者將接地平面拼接成網格狀的(de)圖案。

尺寸更大(dà)的(de)過孔可(kě)用(yòng)於在運行溫度過高(gāo)的(de)元器件下(xià)方進行散熱,從而幫助電路闆散熱。也(yě)可(kě)以將通(tōng)孔或盲孔標記為 PCB 測試點,有些設計甚至可(kě)以將標記為測試點的(de)過孔形狀從圓形改為方形。

因此,PCB 設計中可(kě)能會使用(yòng)很多(duō)不同尺寸和(hé)形狀的(de)過孔。那麼問題是,在設計中管理(lǐ)這麼多(duō)過孔可(kě)能會造成一片混亂。

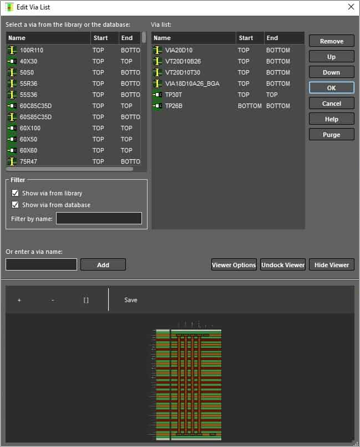

使用(yòng) PCB 設計工具的(de)過孔列表功能,將多(duō)個過孔分(fēn)配給一個網路 (net)

PCB 版圖中過孔的(de)組織問題

上圖顯示的(de)是 CAD 系統中一個網路 (net) 中可(kě)使用(yòng)的(de)過孔清單 (Via list),而其餘的(de)網路可(kě)能在使用(yòng)完全不同的(de)過孔。此外,在 PCB 設計中,還有許多(duō)其他(tā)智慧設計物(wù)件必須與過孔一起管理(lǐ),這進一步增加了(le)設計的(de)複雜程度。而走線寬度、佈線拓撲結構和(hé)間距要求隻是其中的(de)幾項,設計師必須根據對版圖最有利的(de)方式仔細設置使用(yòng)規則。

除此之外,為了(le)使電路闆達到預期性能,通(tōng)常必須要符合一些與特定網路 (nets) 相關的(de)要求,這進一步增加了(le)設計的(de)複雜性。例如,一些高(gāo)速網路可(kě)能被限制在某些層,意味著這些網路需要一個特定的(de)盲孔或埋孔,來確保它們位於所需的(de)層。

雖然設計師也(yě)能在腦海中追蹤這些限制,並為網路 (nets) 使用(yòng)合適的(de)過孔,但當設計中有數百條這樣的(de)規則需要管理(lǐ)時,僅憑大(dà)腦記憶是遠遠不夠的(de)。諸如此類的(de)情況是導緻設計失誤的(de)主要原因,這些錯誤會造成電路闆在運行過程中性能不良或徹底報廢。因此,設計師需要設計工具中具有實用(yòng)程式,來管理(lǐ)電路闆上的(de)大(dà)量過孔及其網路分(fēn)配。

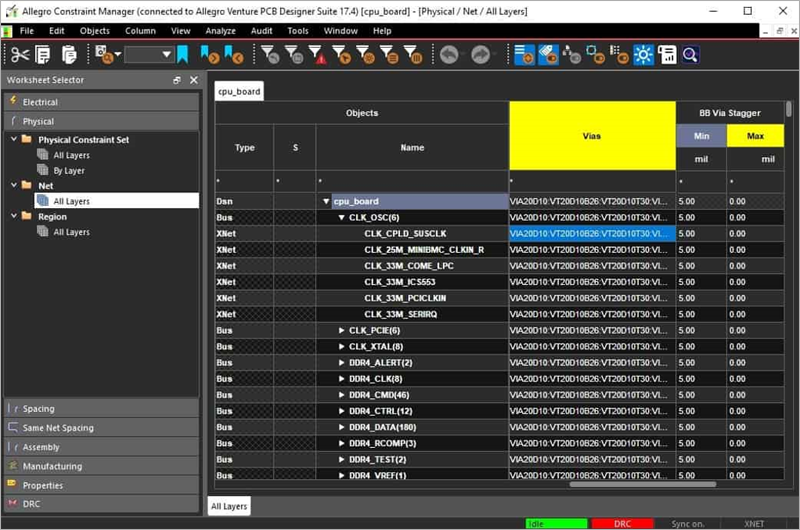

使用(yòng)約束管理(lǐ)系統將過孔 (vias) 分(fēn)配給 PCB 版圖中的(de)各個網路 (nets)

在 PCB 設計使用(yòng)約束 (Constraints) 來管理(lǐ)過孔

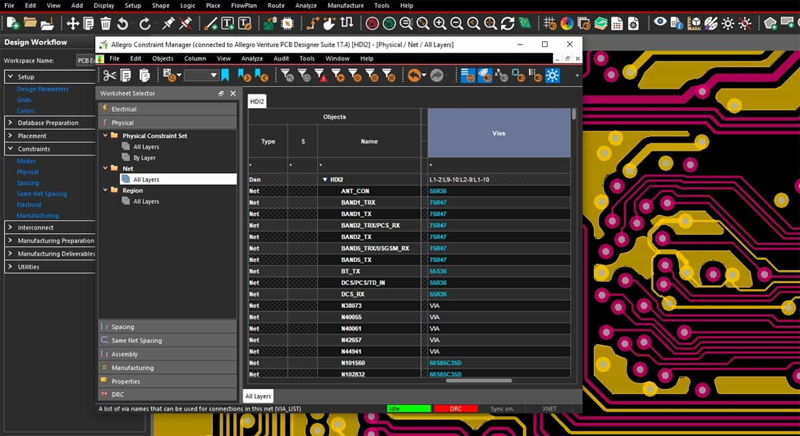

在 PCB 版圖中管理(lǐ)過孔和(hé)其他(tā)智慧設計資料的(de)最佳應用(yòng)之一是設計約束管理(lǐ)系統。上圖是 Cadence PCB 設計工具中的(de)約束管理(lǐ)器 (Constraints Manager)。該系統具有進階的(de)試算(suàn)表式使用(yòng)者介面,可(kě)以方便地輸入並編輯試算(suàn)表單元中的(de)資料。透過試算(suàn)表中的(de)各種功能表,無需打字輸入,就可(kě)以從列表中快(kuài)速挑選特定的(de)項目,如過孔 (Vias) 或網路名稱 (Net name)。

利用(yòng)這種約束管理(lǐ)系統可(kě)以輕鬆創建專案的(de)規則,如單個網路 (nets) 的(de)走線寬度和(hé)間隙。還可(kě)以用(yòng)網路分(fēn)類功能將不同的(de)網路組合成群組,然後為這些類別分(fēn)配規則。除了(le)佈線,約束管理(lǐ)系統還可(kě)以設置電氣、器件和(hé)可(kě)製造性設計 (DFM) 規則,以檢測有可(kě)能影(yǐng)響電路闆可(kě)製造性的(de)問題。

這種試算(suàn)表式的(de)約束系統有助於整理(lǐ)和(hé)設計版圖,以便確保將電路闆送去製造和(hé)組裝之前,版圖中不存在任何問題。下(xià)面仔細瞭解一下(xià)如何在此類約束管理(lǐ)系統中使用(yòng)過孔。

在 Allegro 的(de) Constraint Manager 中為 PCB 設計設置過孔

設計工具示例:過孔約束管理(lǐ)系統

以 Cadence Allegro® PCB Editor 工具為例,使用(yòng) 約束管理(lǐ)器 (Constraint Manager) 的(de)操作非常簡單直接,甚至可(kě)以在版圖或電路圖中執行。如上圖所示,不同的(de)過孔 (vias) 已經被添加到 Constraint Manager 中顯示的(de)網路 (nets) 上。

我們可(kě)以選擇單個 nets 來添加 vias,也(yě)可(kě)以在管理(lǐ)器中一次選擇多(duō)個 nets 來為所有 nets 添加相同的(de) vias。這些 vias 可(kě)以從設計中可(kě)用(yòng)的(de) vias 列表中獲取,而 vias 列表既可(kě)以由設計師創建,也(yě)可(kě)以從資料庫中導入。在 nets 規則中設置好 vias 後,設計師就可(kě)以進行佈線,並且能確認已為電路闆的(de)每個 nets 使用(yòng)正確的(de) vias。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」