本文要點

|

什(shén)麼是垂直導電結構 (Vertical Conductive Structures,VeCS)及其工作原理(lǐ)。 |

|---|---|

|

利用(yòng) VeCS 進行PCB設計的(de)優勢。 |

|

使用(yòng) VeCS 技術設計電路闆的(de)後續步驟。 |

一塊高(gāo)速高(gāo)密印刷電路闆

長久以來,我們不斷努力改進設計和(hé)構建電路闆的(de)方式——已從通(tōng)孔發展到表面貼焊元件,從雙層電路闆發展到多(duō)層電路闆,從普通(tōng)導線走線發展到高(gāo)密佈線。似乎如今已沒有什(shén)麼可(kě)以嘗試的(de)新鮮技術,然而這種想法是錯誤的(de)。

為了(le)盡可(kě)能有效地利用(yòng)可(kě)用(yòng)的(de)電路闆空間,目前業內正在引入一種新的(de)走線佈線方法。這種方法使用(yòng) 垂直導電結構 (Vertical Conductive Structures,VeCS),允許在闆層疊構中垂直佈線,而不是使用(yòng)傳統的(de)過孔 (Vias)。顯然,這樣做(zuò)可(kě)以節省不少空間,還額外帶來許多(duō)其他(tā)好處。下(xià)面我們來具體瞭解一下(xià)。

什(shén)麼是垂直導電結構 (VeCS) 及其工作原理(lǐ)

在擁有大(dà)量引腳、遍佈細間距元件的(de)高(gāo)密電路闆上進行佈線,挑戰之一是為所有的(de)走線找到足夠的(de)佈線通(tōng)道。即便使用(yòng)微孔 (microvias) 和(hé) BGA 盤中孔 (via-in-pad) 技術進行逃逸佈線 (escape routing),用(yòng)於佈線的(de)可(kě)用(yòng)空間也(yě)會很快(kuài)用(yòng)完。另一個問題是,為了(le)在更多(duō)的(de)層上打更深的(de)孔,必須增加鑽孔直徑,這也(yě)佔用(yòng)了(le)更多(duō)的(de)空間。此時,垂直導電結構 (VeCS) 就有了(le)用(yòng)武之地。

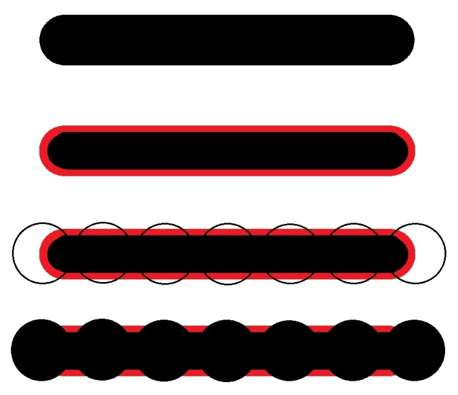

VeCS 技術允許走線垂直穿過電路闆的(de)堆疊,從而取代了(le)鑽孔。除了(le)傳統的(de)製造通(tōng)孔電路所需的(de)設備外,該技術不需要使用(yòng)任何專門的(de)設備,但它會將 PCB 的(de)佈線密度提高(gāo)到接近高(gāo)密互連 (HDI) 的(de)水(shuǐ)準。以下(xià)是在電路闆上製造 VeCS 的(de)基本步驟,如下(xià)圖所示:

1. |

從頂部看,藉由在電路闆材料上鑽孔和(hé) / 或佈線來創建一個插槽。 |

|---|---|

2. |

根據標準的(de) PCB 製造技術,對該插槽進行金屬化(huà)和(hé)電鍍處理(lǐ)。 |

3. |

較大(dà)的(de)鑽孔相鄰放置,以鑽出不需要的(de)金屬。 |

4. |

剩下(xià)的(de)是小的(de)、垂直的(de)走線,貫穿電路闆的(de)疊構。 |

VeCS 的(de)基本製造過程

當然,這隻是一個非常基本的(de)例子,實際製造過程取決於每個應用(yòng)的(de)具體要求。如上圖底部所示,紅色的(de)小區域是垂直穿過電路闆的(de)金屬。然後,這些垂直的(de)導體可(kě)以觸及電路闆內層的(de)普通(tōng)水(shuǐ)準走線。

可(kě)以在垂直導電結構中使用(yòng)兩種插槽技術:VeCS-1 和(hé) VeCS-2。第一種類型的(de)插槽穿過整個電路闆疊構,而第二種類型則用(yòng)於多(duō)層盲孔連接。由於 VeCS 是使用(yòng)標準工藝製造的(de),它們也(yě)可(kě)以與通(tōng)孔、盲孔和(hé)埋孔以及微孔技術結合使用(yòng)。這提供了(le)諸多(duō)優勢,詳見下(xià)文討論。

利用(yòng)垂直導電結構進行 PCB 設計的(de)優勢

從上圖可(kě)以看到,垂直導體的(de)橫截面更小,比鑽孔的(de)橫截面更接近於標準走線。與通(tōng)孔相比,這種導體輪廓最終導緻網格 (net) 的(de)電感量更小。同時,更有利於垂直走線將訊號傳遞到參考平面,所有這些都有助於改善電路闆的(de)整體訊號完整性。

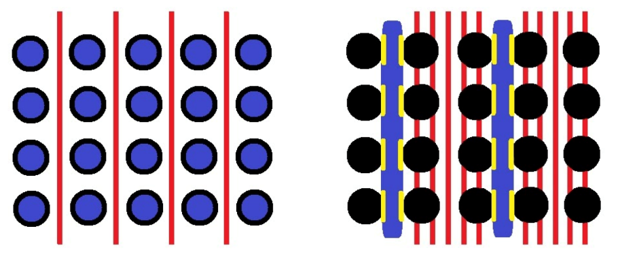

不過,最主要的(de)優勢可(kě)能是 VeCS 為走線佈線增加了(le)佈線通(tōng)道。對於一個具有 0.5 毫米間距引腳的(de) BGA 元件,使用(yòng)盤中孔 (via-in-pads) 進行逃逸佈線時,在內層佈線通(tōng)道上的(de)孔之間的(de)空間僅夠佈設一條走線。然而,透過使用(yòng) VeCS,佈線通(tōng)道的(de)數量增加到了(le)五個。在下(xià)圖中,可(kě)以看到兩者之間的(de)區別,左邊是標準的(de)盤中孔逃逸佈線模式,右邊是 VeCS。

藍色代表鑽孔或佈線的(de)區域,而紅色是可(kě)以經由內層的(de)通(tōng)道進行佈線的(de)走線。可(kě)以看到,黃色的(de)垂直走線連接到黑(hēi)色的(de) BGA 焊盤,然後向下(xià)延伸通(tōng)過電路闆層疊構。同樣,這隻是一個基本的(de)例子,但它可(kě)以讓我們瞭解 VeCS 所能提供的(de)一些空間優勢。

盤中孔和(hé) VeCS 佈線比較

有了(le)增加佈線密度的(de)能力,電路闆的(de)尺寸和(hé) / 或層數就可(kě)以減少;這也(yě)會降低製造成本。那麼下(xià)一個問題是,如何才能在 PCB 上設計 VeCS?

使用(yòng) VeCS 技術設計電路闆的(de)後續步驟

製造和(hé)設計垂直導電結構 (VeCS) 的(de)技術早已問世。PCB 設計 CAD 工具經過恰當設置後可(kě)以與這種技術配合使用(yòng);此外,一些先進的(de)設計系統,如 Cadence Allegro PCB Designer,無需額外配置即可(kě)設計 VeCS。同時,也(yě)要確保合作的(de) PCB 製造廠經過許可(kě),能夠生產這種技術。一旦確認了(le)這一點,就可(kě)以開始探索這項新技術了(le)。

在我們的(de)行業中,還會出現更多(duō)新的(de)電路闆設計和(hé)製造技術,為了(le)保持領先,我們應該做(zuò)好準備,在這些新的(de)技術出現時進行大(dà)膽探索。要實現這一點,需要擁有一個能夠支援這些新技術的(de) PCB 設計系統作為設計過程的(de)基礎。事實證明(míng),Allegro PCB Designer 經過妥當設置,可(kě)以很好地支援 VeCS 和(hé)許多(duō)其他(tā)新興技術。

如欲進一步瞭解更多(duō) Allegro 高(gāo)速工具應用(yòng),歡迎聯繫 Cadence 台灣授權代理(lǐ)商 - 映陽科技團隊。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」