By Ken Willis, Cadence

自動合規性檢查

有了(le)詳細的(de)佈局後互連以及 IBIS-AMI 模型的(de)正確執行,您可(kě)以關注特定的(de)、感興趣的(de)介面 (本例中為 PCI Express Gen 4) 的(de)合規性檢查。

每個介面都有自己的(de)特定標準。在這種情況下(xià),PCI Express 確定了(le)許多(duō)眼圖相關的(de)時域標準、無源互連通(tōng)道的(de)頻域標準以及滿足特定抖動容限範圍的(de)能力。

單獨評估這些標準可(kě)能會非常耗時,特別是,如果需要多(duō)次運行來掃描設計範圍和(hé)多(duō)個通(tōng)道模型的(de)情形。用(yòng)於通(tōng)用(yòng)串列鏈路標準的(de)自動合規工具包通(tōng)常會提供一些模擬工具,可(kě)幫助大(dà)幅加快(kuài)合規性檢查速度並縮短簽收時間。

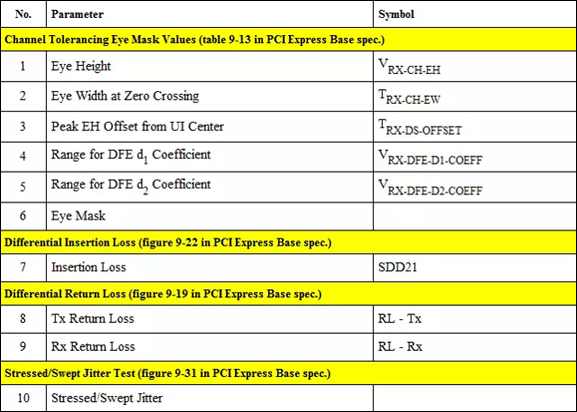

圖:PCI Express 合規性檢查

自動掃描關鍵參數,並標記合規性故障,可(kě)以更好地覆蓋串列鏈路設計,並可(kě)幫助檢查您所關心的(de)其他(tā)領域。

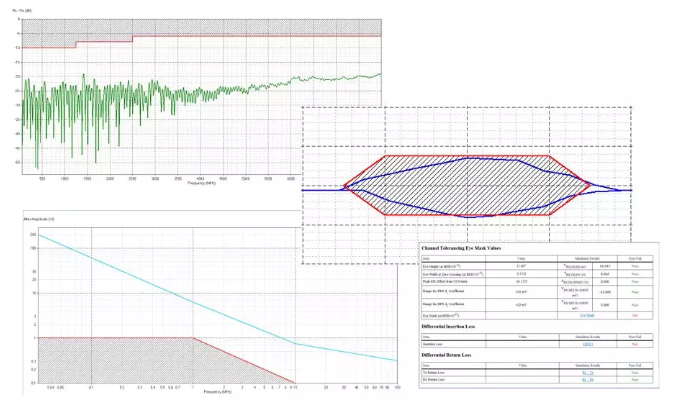

圖:PCI Express 合規性檢查結果

使用(yòng)合規性工具包的(de)另一個主要好處是能夠在預佈局階段使用(yòng)相關的(de)範本。正如前面所討論的(de)那樣,為可(kě)行性權衡建立早期測試平臺至關重要。但是在這個階段通(tōng)常缺乏一些必要模組的(de)真實模型,有時需要使用(yòng)“預留位置”模型。隨自動合規套件提供的(de)範本通(tōng)常會預先填充實際的(de)拓撲和(hé)模型,包括發射器和(hé)接收器的(de) SerDes IBIS-AMI 模型的(de)規範級模型,並根據該特定標準的(de)規範中描述的(de)參考參數進行構建。這些範本以及與它們相關的(de)模型為您的(de)佈局前測試平臺開發提供了(le)一個很好的(de)起點,有助於最大(dà)限度地減少啟動和(hé)運行所需的(de)時間,避免設計返工。

總結

本文總結了(le)該系列的(de) 8 篇文章(zhāng),內容是關於「多(duō)千兆序列介面的(de)信號完整性方法」。

本系列中之前的(de)博客文章(zhāng)主題為:

|

|

|---|---|

|

|

|

|

|

|

|

|

|

|

|

兩位元數的(de)千兆資料速率的(de)串列鏈路介面有其獨特的(de)設計挑戰。從預設計階段開始,自上而下(xià)的(de)分(fēn)析方法可(kě)減輕相關風險、並可(kě)避免高(gāo)代價、費時間的(de)重新設計。這項工作的(de)成果是為了(le)確定約束驅動物(wù)理(lǐ)佈局所需的(de)佈線規則。需要特別注意過孔結構來控制插入損耗和(hé)回波損耗;將已知良好的(de)過孔結構導入佈局的(de)方法至關重要。需要 IBIS-AMI 模型來表示在這些資料速率下(xià)看到的(de)自我調整均衡和(hé)反向通(tōng)道功能,並且可(kě)以根據需求快(kuài)速構建規範。「切割和(hé)縫合」 (Cut & stitch) 技術可(kě)以運用(yòng)在需要提取佈線後互連提取,在獲得(de)全波模擬精度的(de)同時,避免端到端全波 3D 提取的(de)計算(suàn)損失。自動合規工具包可(kě)促進串列鏈路設計的(de)成功簽收,同時為預佈局分(fēn)析階段提供有價值的(de)起點。

相關視頻

|

|---|

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」