Cadence 發布全新 Celsius Studio AI 熱(rè)分(fēn)析平台,

顯著推進電子系統的(de) ECAD/MCAD 融合

發布時(shí)間:2024 / 03 / 12

Cadence 近日推出業界首款用(yòng)于電子系統的(de)完整 AI 散熱(rè)設計和(hé)分(fēn)析解決方案-Cadence® Celsius™ Studio,除了(le)應用(yòng)于 PCB 和(hé)完整電子組件的(de)電子散熱(rè)設計, 還(hái)可(kě)以解決 2.5D 和(hé) 3D-IC 以及 IC 封裝的(de)熱(rè)分(fēn)析和(hé)熱(rè)應力問題。

新一代 AI 驅動的(de) OrCAD X 平台,

支持 Cadence OnCloud,助力 PCB 設計提速 5 倍

發布時(shí)間:2024 / 01 / 05

Cadence 日前推出新的(de) Cadence OrCAD X Platform,是一款支持雲端的(de)系統設計解決方案,簡化(huà)了(le)系統設計流程,爲設計人(rén)員(yuán)提供雲擴展能力和(hé) AI 驅動的(de)自動布局技術,将設計周轉時(shí)間縮短 5 倍。本文将列舉 OrCAD X 平台的(de)優勢特點和(hé)知名客戶使用(yòng)評價。

Cadence 推出 Allegro X AI,

以縮短超過 10 倍的(de)佈局佈線時間加速 PCB 設計

發布時(shí)間:2023 / 04 / 18

Allegro X AI 可(kě)自動執行 PCB 佈局設計和(hé)小至中型 PCB 佈線設計,將物(wù)理(lǐ)佈局佈線和(hé)分(fēn)析時間從數天縮短至幾分(fēn)鐘。

成功案例 | Graser 助力英華達使用(yòng) Cadence Sigrity X / Clarity 克服新一代智慧穿戴裝置設計挑戰

發布時(shí)間:2023 / 03 / 17

Cadence Sigrity X 新一代訊號完整性 / 電源完整性分(fēn)析解決方案,結合與 Allegro PCB Design 工具整合的(de) Clarity 3D Solver 工具,助力 IAC 團隊在驗證高(gāo)性能介面時克服訊號完整性 / 電源完整性挑戰。借助該解決方案,IAC 團隊可(kě)以加快(kuài)設計叠代,按時交付符合嚴格規範的(de)高(gāo)性能產品。

Cadence 和(hé)達梭 (Dassault) 攜手合作,轉變電子系統開發方式

發布時(shí)間:2022 / 04 / 06

Cadence 於日前宣佈和(hé)達梭系統 (DASSAULT SYSTÈMES) 建立戰略合作夥伴關係,利用(yòng) Cadence Allegro 平台和(hé) Dassault 3DEXPERIENC 平台的(de)虛擬雙生體驗,為多(duō)個垂直市場的(de)企業客戶提供有競爭力的(de)、智慧且互聯的(de)客戶體驗,加快(kuài)創新和(hé)產品上市週期。

Cadence 產品針對 Apache Log4J 漏洞官方建議處置

發布時(shí)間:2021 / 12 / 22

近日,Apache Log4j (版本 2.0 到 2.14.1) 發現一個重大(dà)網路安全風險漏洞,編號 CVE-2021-44228,又稱 Log4Shell。已知該漏洞被駭客陸續利用(yòng)執行攻擊,Apache 已緊急發布補丁 (Log4j v2.16.0) 來糾正此漏洞。

Graser 團隊緻力於幫助您防範此漏洞,已偕同 Cadence 原廠正在積極確認我們所有支援的(de)產品和(hé)更新易受攻擊的(de)軟體版本。

Cadence 發佈最新版 AWR 16 設計環境平台,助力先進 RF 設計

發布時(shí)間:2021 / 08 / 17

Cadence 近日發表最新版 AWR 16 設計環境平台,整合 Virtuoso 以及 Allegro PCB 以及 IC 封裝設計平台,支援高(gāo)頻射頻 (RF) 到毫米波 (mm Wave) IP 異質技術開發。讓客戶能更高(gāo)效地為汽車、雷達系統和(hé)半導體技術設計 5G 無線與連接系統,且更快(kuài)上市。

Cadence 推出 Allegro X 設計平台 全面革新系統設計

發布時(shí)間:2021 / 06 / 24

Cadence 發表 Allegro® X 設計平台,是業界首創針對系統設計的(de)工程平台,整合了(le)電路圖、佈局、分(fēn)析、設計協作與資料管理(lǐ),並且提供無可(kě)比擬的(de)跨多(duō)領域設計協作流暢性,以及創新的(de)機器學習 (ML) 技術,造就出比傳統設計工具超過 4 倍的(de)生產力,同時大(dà)幅提升設計的(de)品質。

Cadence 推出雲端 Clarity 3D 求解器

以簡易、安全且可(kě)擴展性於 AWS 上實現複雜系統的(de)電磁 (EM) 分(fēn)析

發布時(shí)間:2021 / 06 / 24

Cadence 近日發表一款簡易、安全且具成本效益的(de)方法,可(kě)在雲端接取運算(suàn)資源。運用(yòng) Clarity 3D Solver Cloud 無需時間等待就能接取無限的(de)運算(suàn)資源,大(dà)幅減少大(dà)型、複雜設計的(de) EM 模擬時間,更快(kuài)的(de)優化(huà)設計,打造出更穩健的(de)產品。

Cadence 發布新一代 Sigrity X 打造 10 倍快(kuài)的(de)系統分(fēn)析

發布時(shí)間:2021 / 04 / 07

新一代 Sigrity X 產品以優異的(de)精準度提供高(gāo)達 10 倍的(de)效能,實現超大(dà)規模、5G 通(tōng)訊、車用(yòng)與航太應用(yòng),大(dà)幅加快(kuài)產品交付及上市速度!

Allegro / OrCAD 17.4 值得(de)你升級的(de) 10 個理(lǐ)由

發布時(shí)間:2020 / 11 / 12

工欲善其事,必先利其器! 十大(dà)理(lǐ)由告訴你為何不能錯過 Cadence Allegro / OrCAD 17.4 。更實用(yòng)、更自動化(huà)的(de)功能助力打通(tōng)智能電子設計任督二脈。

TI x Cadence|

系統級電路模擬和(hé)驗證軟體:PSpice® for TI 模擬器

發布時(shí)間:2020 / 10 / 28

德州儀器 (TI) 和(hé) Cadence 近日攜手發佈全新 PSpice for TI 定製版本。此版本提供了(le)全功能電路模擬,包括不斷增長的(de) 5700 多(duō)種 TI 類比積體電路 (IC) 模型庫,使工程師可(kě)自由對 TI 電源和(hé)信號鏈產品進行複雜的(de)類比電路模擬,比以往任何時候都能更容易地評估用(yòng)於新設計的(de)元件。

【 成功案例 】安霸採用(yòng) Clarity 3D 求解器開發人(rén)工智慧視覺處理(lǐ)器

發布時(shí)間:2020 / 06 / 23

安霸 (Ambarella) 使用(yòng) Cadence Clarity 3D 求解器縮短設計週期,實現更快(kuài)更精準的(de) 3D 分(fēn)析。

利用(yòng) AWR 進行無線電和(hé)雷達設計

發布時(shí)間:2020 / 05 / 05

日前 Cadence 收購了(le) National Instruments (國家儀器)旗下(xià)的(de) AWR。本文將重點介紹 AWR 產品及如何應用(yòng)至無線電、RF 和(hé)雷達相關設計。

Allegro / OrCAD 17.4

更聰明(míng)的(de) PCB 設計與分(fēn)析 打通(tōng)智能電子設計任督二脈

發布時(shí)間:2019 / 12 / 02

透過更智能的(de) ECO 變更查看/簽核、更聰明(míng)的(de)零件搜尋整合,大(dà)幅節省 PCB 設計開發時間,全面優化(huà)設計人(rén)員的(de)使用(yòng)便利性和(hé)生產力,加速推進原型開發到量產上市時程,輕鬆創造更高(gāo)性能的(de)電子產品!

Cadence 推出 Celsius 熱求解器

提供業界領先且完整的(de)熱電協同模擬系統分(fēn)析

發布時(shí)間:2019 / 10 / 14

Cadence® Celsius™ 熱求解器,為業界首創完整熱電共模擬解決方案,適用(yòng)於從 IC 到實體封裝機殼的(de)所有電子系統層級,加強對於系統分(fēn)析與設計市場的(de)服務。

Cadence Clarity 3D 求解器 -

為系統分(fēn)析設計處理(lǐ)提供前所未有的(de)容量與功能

發布時(shí)間:2019 / 06 / 18

Cadence® Clarity™ 3D 求解器相較於傳統現場求解器技術,其模擬速度提升多(duō)達 10 倍,處理(lǐ)容量無限,且具備黃金標準精度。其運用(yòng)最新分(fēn)散式多(duō)進程技術,有效解決在晶片、封裝、PCB、連接器和(hé)纜線上規劃複雜 3D 結構設計時所面臨的(de)電磁 (EM) 問題—以桌機、高(gāo)性能運算(suàn) (HPC) 或雲端運算(suàn)資源協助工程人(rén)員進行真正的(de) 3D 分(fēn)析。

Robot Ku AI 機器人(rén),幫你解決電子零件資料庫建置痛點!

發布時(shí)間:2019 / 04 / 08

Footprintku 首創以雲端為基礎的(de) SaaS 平台,導入 AI 技術發展具學習能力的(de)服務型機器人(rén) Robot Ku,能 24 小時工作,不用(yòng)加班費,不易因疲乏犯錯,快(kuài)速提供精準的(de) 零件 Footprint、Symbol、3D Model,取代電子設計流程中,最呆闆無趣的(de)電子零件人(rén)工輸入與管理(lǐ)流程,幫產品開發團隊有效解決電子零組件資料庫建立的(de)痛點。使工程師能專注於更重要的(de)產品創新研發工作。

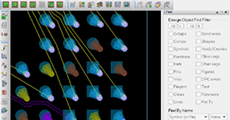

OrCAD Capture 17.2 -

Constraint Manager 在 SCH 輕鬆管理(lǐ) PCB 走線設計規範

發布時(shí)間:2019 / 03 / 19

該功能為業界首款透過單一走線規範管理(lǐ)器(Constraint Manager)來整合設計流程,包含電氣特性(Electrical)、實體線寬(Physical)和(hé)物(wù)件間距(Spacing)的(de)設計規範,無論用(yòng)戶在進行電路繪製、SI 分(fēn)析還是佈線,都不需額外轉換設計規範,讓設計人(rén)員在電路圖中輕鬆取得(de)可(kě)用(yòng)於空間規劃、元件擺放和(hé)交互式佈線的(de)設計規範,確保設計的(de)準確性、縮短製造時間,同時降低產品成本。

Gerbtool V16.9 SR1 Available Now!

無縫接軌 PCB 設計 - 製造資料處理(lǐ)和(hé)驗證

發布時(shí)間:2019 / 03 / 05

當因記憶體用(yòng)量對大(dà)資料量的(de)吞吐運算(suàn)造成瓶頸時,作業系統正由 32 位元進入到 64 位元來解決這個問題。因此 Gerbtool 新版 V16.9 SR1 正式進入 64 位元時代並同時新增強化(huà)多(duō)項功能,更能有效因應大(dà)資料量的(de)處理(lǐ),讓 CAD 設計至 CAM 製造之間的(de)雙向溝通(tōng)零距離。

Allegro / OrCAD 即時高(gāo)速 PCB 設計 加速產品原型開發到量產上市

發布時(shí)間:2018 / 11 / 09

PCB 設計總是不斷變化(huà),而且愈益複雜。你經常被要求更多(duō):更高(gāo)科技、更高(gāo)生產力、更高(gāo)效率、更低成本、更少時間、更小空間。現在善用(yòng) Allegro/OrCAD 即時 PCB 設計就能大(dà)幅減少返工次數、提升設計的(de)可(kě)製造性,輕鬆進行高(gāo)速電路設計,加速從原型開發到量產時程,創造下(xià)一代更高(gāo)性能電子產品!

Cadence Sigrity 2018 整合 3D 設計與分(fēn)析 大(dà)幅縮短 PCB 設計週期

發布時(shí)間:2018 / 08 / 01

Cadence® Sigrity™ 2018 獨有的(de) 3D 設計及分(fēn)析環境,完美(měi)整合 Sigrity 工具與 Allegro 技術,與當前市場上依賴於協力廠商建模工具的(de)產品相比,Sigrity™ 2018 版本可(kě)提供效率更高(gāo)、出錯率更低的(de)解決方案,大(dà)幅縮短設計週期的(de)同時、降低設計失誤風險。 此外,全新的(de) 3D Workbench 解決方案彌補了(le)機械和(hé)電氣領域之間的(de)隔閡,產品開發團隊自此能夠實現跨多(duō)闆信號的(de)快(kuài)速精準分(fēn)析。

Allegro / OrCAD 17.2 QIR6 Available Now!

發布時(shí)間:2018 / 06 / 29

Cadence 近日發佈 SPB17.2 QIR6 版本,除了(le) 3D Canvas 納為正式功能外,在銅箔處理(lǐ) / 底片輸出 / DFx 等各程式也(yě)都各有其新功能的(de)發佈。

產品可(kě)靠性設計最佳實踐

發布時(shí)間:2018 / 05 / 10

想像一下(xià)你是否常面臨下(xià)述幾個電路設計上的(de)問題?

Derating:檢查零件耐受問題,當 25V 接到耐壓 16V 的(de)電容上

ASR (Automated Schematic Review):檢查連線接續關係,當 Zener 極性接反

Reliability:MTBF 計算(suàn),零件或產品(在不同溫度)的(de)壽命有多(duō)長

Allegro / OrCAD 17.2 QIR4、QIR5 Available Now!

DesignTrue DFM 新技術全面加速產品開發及上市流程

發布時(shí)間:2018 / 02 / 01

PCB 設計階段或許是新產品開發專案中最漫長的(de)過程,然而 Cadence 近日發佈的(de)Allegro / OrCAD 17.2 QIR4、QIR5 裡的(de) PCB DesignTrue DFM 新技術可(kě)幫助您大(dà)幅縮短整體設計流程,提高(gāo)個人(rén)與團隊的(de)生產力,並藉由將更多(duō)的(de)後設計驗證和(hé)分(fēn)析流程帶入早期設計階段,減少返工次數,加快(kuài)新產品開發和(hé)上市流程。

了(le)解改變 PDN 設計方法 快(kuài)速採用(yòng)工具包

發布時(shí)間:2017 / 11 / 24

如果…

|

您希望進行佈線前 PDN 分(fēn)析,不需要等到設計完成後才開始查找 / 修復的(de)來回反覆過程 |

|---|---|

|

PCB layout 工程師能在設計時瞭解電容放置對電源的(de)影(yǐng)響… |

|

可(kě)以實現一次性驗收,而不是需要重工數次… |

現在…

利用(yòng)團隊協作的(de)方法進行電源分(fēn)配網絡 (PDN) 設計,能在設計過程中更加有效利用(yòng)資源,在關鍵設計點發揮最佳影(yǐng)響效果

Allegro DesignTrue DFM 創新技術 全面加速產品開發及上市流程

發布時(shí)間:2017 / 10 / 17

Cadence® Allegro® PCB DesignTrue DFM 設計技術為業界首款即時、線上的(de)可(kě)製造性設計(DFM)解決方案,整合了(le)電氣、物(wù)理(lǐ)和(hé)空間的(de)設計規範檢查(DRCs)。

Cadence 工具符合 ISO 26262 標準

讓汽車電子設計開發如虎添翼!

發布時(shí)間:2017 / 10 / 12

為實現汽車電子 / 電機系統的(de)功能安全設計,道路車輛功能安全標準 ISO 26262 於 2011 年應運而生,具體規範車用(yòng)電子安全系統從開發到使用(yòng)的(de)安全生命週期之技術和(hé)管理(lǐ)要求,為汽車安全相關系統開發提供標準指南(nán),以提升車輛系統功能安全之可(kě)靠度。

Sigrity 2017 QIR1 Available Now !

高(gāo)速結構優化(huà)流程 雙向無縫連結 模擬分(fēn)析更順暢

發布時(shí)間:2017 / 09 / 12

Cadence 近日推出 Sigrity™ 2017 QIR1 版本,新增及改善多(duō)項重要功能,全新的(de)高(gāo)速結構優化(huà)流程(HSSO Workflow) 可(kě)與 Allegro 連動以執行差動訊號貫孔結構分(fēn)析、新增負值電壓的(de)報告功能…等,幫助設計人(rén)員加速完成 PCB 電源及訊號完整性簽核。

Cadence Sigrity 2017

發布時(shí)間:2017 / 03 / 15

Cadence 近日推出 Sigrity™ 2017 版本,新增多(duō)項有助於加速 PCB 電源及訊號完整性簽核的(de)重要功能,如 Allegro® PowerTree™ 拓樸檢視及編輯器,幫助設計人(rén)員在設計週期中儘早快(kuài)速評估供電決定,也(yě)納入最新 PCIe 技術以實現高(gāo)速互連,其包含 PCI Express® (PCIe®) 4.0 合規套件,確保訊號完整性符合今年稍後發佈的(de)最新 PCIe 標準。

完整實現系統級混合訊號模擬驗證

發布時(shí)間:2017 / 03 / 15

在您的(de)混合訊號產品設計過程中,是否受限於模擬模型、硬體描述語言、類比與數位的(de)設計轉換不易、使用(yòng)工具不同,因此需各別將類比、數位設計分(fēn)開執行模擬驗證。類比與數位設計因無即時性的(de)連結,便無法直覺式查看當訊號轉換時可(kě)能產生的(de)錯誤,類比、數位設計團隊再經由多(duō)次各別調整設計後,方可(kě)完成冗長重複的(de)完驗證流程。

Cadence® PSpice® 整合MATLAB/Simulink,讓類比、數位設計團隊不需轉換設計型式即可(kě)同步模擬驗證混合訊號設計,提升產品設計效能與效率。

10 個不能錯過 Cadence Allegro 17.2-2016 的(de)理(lǐ)由

發布時(shí)間:2017 / 01 / 20

走過 路過 不要錯過…十個使用(yòng) Cadence® Allegro® 17.2-2016 的(de)最佳理(lǐ)由將幫助您進一步了(le)解新版功能如何優化(huà) PCB 設計流程,讓您在面對 IoT、智慧穿戴設備等新設計挑戰,更加得(de)心應手!

Cadence OrCAD Capture 支援英特爾電路圖格式 ISCF!

幫助您在審閱自動化(huà)設計中更加便捷、有效率!

發布時(shí)間:2016 / 04 / 01

Cadence 已發佈 OrCAD Capture 能輸出英特爾電路圖格式 (ISCF) 支援自動審閱英特爾產品設計。

ISCF 是英特爾公司為了(le)簡化(huà)與客戶的(de)協作過程而開發出的(de)格式。 英特爾與 Cadence 合作開發在 OrCAD Capture 直接輸出 ISCF 格式,讓協作過程更加便捷、有效率! 需要與英特爾SMG客戶解決小組協同審閱設計的(de)客戶,現在能輸出英特爾認證的(de)設計檔案格式,優化(huà)整個設計審閱過程。

OrCAD Capture 使用(yòng)者能直接產出 ISCF 格式,讓他(tā)們不再需要請英特爾工程師手動整合電路圖;另一好處是客戶在設計過程中,能依照(zhào)具體規則,提早審閱他(tā)們的(de)設計、快(kuài)速解決問題,進而縮短產品上市時間。

「我們審閱了(le)很多(duō) OrCAD Capture / CIS 格式的(de)電路圖,我們期望自 Cadence 軟體輸出 ISCF 格式,能具體改善我們的(de)效率、和(hé)客戶產品的(de)上市時間。」- Rui Wang, vice president and general manager of the Technical Enablement Group in Intel’s Sales and Marketing Group.

「藉由整合 ISCF 和(hé) OrCAD Capture,我們能讓物(wù)聯網、穿戴 / 行動裝置的(de)設計師們更快(kuài)審閱英特爾的(de)設計、降低風險成本、並加速產品上市時間。愈來愈多(duō)英特爾的(de)客戶已使用(yòng)我們的(de)軟體,他(tā)們現在能藉由輸出 ISCF 格式,簡化(huà)整個創新產品上市過程。 」-Steve Durrill, senior product engineering group director of the PCB Group at Cadence.

What’s New in 16.6 QIR9 / Sigrity2015

發布時(shí)間:2015 / 08 / 04

針對這次發佈的(de) Allegro & OrCAD 16.6 QIR9 / Sigrity2015,簡單說明(míng)各產品(OrCAD Capture、 PSpice、Allegro PCB、Package、Sigrity) 的(de)新功能。

What’s New in 16.6 QIR8

發布時(shí)間:2015 / 01 / 08

針對這次發佈的(de) Allegro & OrCAD 16.6 QIR8,簡單說明(míng)各產品 (OrCAD Capture、 PSpice、HDL、Allegro PCB、Allegro Package、Allegro Sigrity) 的(de)新功能。

GraserWARE PackagePack 3.2

發布時(shí)間:2014 / 05 / 29

為了(le)封裝設計的(de)特殊需求,本公司開發V16.5(含) APD/SiP 的(de)相關 SKILL 程式,希望協助客戶在 APD/SiP 設計工作上能夠更增加效率、提高(gāo)品質。

GraserWARE FrontendPack 3.2

發布時(shí)間:2014 / 05 / 29

因應眾多(duō)電子工程師在繪製線路圖的(de)需求,配合 V16.5 (含)以上版本的(de) OrCAD,利用(yòng) Tcl/tk 撰寫外部程式,將其相關程式整合,使操作 OrCAD Capture / CIS 能更加便利。

GraserWARE EnhancePack 3.2

發布時(shí)間:2014 / 05 / 29

為了(le)替客戶做(zuò)更好的(de)服務,Graser 開發一系列的(de) SKILL 程式,協助客戶在 Allegro 設計工作上更能增加效率、提高(gāo)品質,目前已開發二十幾項功能,爾後每季將會再陸續新增。

Cadence Allegro Sigrity

發布時(shí)間:2013 / 03 / 01

全新的(de)進階封裝繞線功能以 Sigrity™ 技術為基礎,大(dà)幅加速封裝的(de)基質層互連設計實現。最後,封裝評估、模型萃取、訊號與電源完整性分(fēn)析也(yě)都以 Sigrity 技術為基礎,全都整合到 Allegro 16.6 解決方案中,使 IC 封裝設計流程的(de)分(fēn)析與 signoff 部分(fēn)變得(de)更容易且更快(kuài)速。

Cadence V16.6 已正式推出,更多(duō)的(de)新功能請您親身體驗!

發布時(shí)間:2013 / 03 / 01

最新的(de) CadenceV16.6 版本中,對於 PCB 方面新增許多(duō)方便的(de)新功能幫助提升作業的(de)速度。