三維平面電磁分(fēn)析軟件

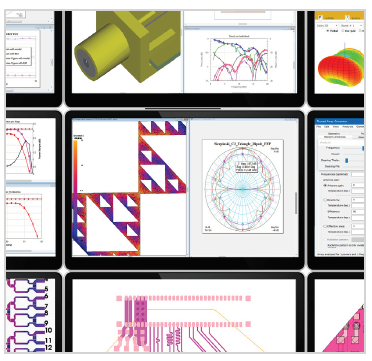

Cadence® AWR® AXIEM® 是 Cadence AWR Design Environment® 平台内的(de)三維平面電磁 (EM) 分(fēn)析軟件,其快(kuài)速求解器技術可(kě)輕松實現被動結構、傳輸線、大(dà)型平面天線和(hé)貼片數組的(de)設計。無論是對(duì) PCB、模塊、低溫共燒陶瓷 (LTCC)、毫米波集成電路 (MMIC)、RFIC 還(hái)是天線上的(de)被動組件進行特征分(fēn)析和(hé)優化(huà),AWR AXIEM 軟件均可(kě)提供一次設計成功所需的(de)準确度、性能和(hé)速度。

快(kuài)速、準确的(de)自我調整混合網格技術支持厚金屬平面結構和(hé)過孔,自動将結構分(fēn)解爲三角形和(hé)矩形單元,在任何的(de)頻(pín)段均可(kě)得(de)到最準确和(hé)穩健的(de)寬帶結果。

AXIEM 無縫整合電路和(hé)系統設計,支持直接對(duì)被動組件和(hé)互連結構等平面結構進行電磁協同仿真。專有的(de) AWR 統一數據模型支持電磁提取和(hé)設計驗證,将結果直接整合入電路和(hé) / 或系統仿真中,無需執行明(míng)确的(de)布局定義、電磁仿真設置步驟或數據導入。

多(duō)功能、種類廣泛的(de)源 / 埠 (包括經過自動校準的(de)内部端口和(hé) de-embedding 選項) 可(kě)提供更大(dà)的(de)靈活性,同時(shí)保持基于嵌入式電路的(de)集總組件和(hé)主動組件 (如晶體管) 的(de)結構精度。

特點

|

布局 / 繪圖編輯器 – 二維和(hé)三維視圖 |

|---|---|

|

專有矩量法 (MoM) 技術 |

|

混合網格劃分(fēn)技術 – 自動進行自适應網格劃分(fēn) (混合矩形 / 三角形網格) |

|

多(duō)個(gè)源和(hé)激勵 |

|

可(kě)視化(huà)和(hé)結果後處理(lǐ) |

|

參數研究 – 優化(huà)、調諧和(hé)良率分(fēn)析 |

|

HPC – 多(duō)核配置和(hé)異步仿真 |

網格劃分(fēn)

AWR AXIEM 軟件經過專門優化(huà),可(kě)使用(yòng)先進的(de)混合網格劃分(fēn)技術将結構自動分(fēn)解爲三角形和(hé)矩形單元,從而最大(dà)程度地提高(gāo)準确性并降低未知風險。這(zhè)種啓發法擴展了(le)工具的(de)功能範圍,使之遠(yuǎn)遠(yuǎn)超越傳統的(de)同類網格類型。

矩量法

該軟件采用(yòng)了(le)一種獨特專有技術,與快(kuài)速的(de)多(duō)極方法相似,但也(yě)适用(yòng)于全波分(fēn)析。因此,與大(dà)多(duō)數現有的(de)矩量法 (MoM) 産品所使用(yòng)的(de) N3 相比, AWR AXIEM 求解算(suàn)法對(duì) N*log(N) 中的(de)階次進行了(le)縮放。

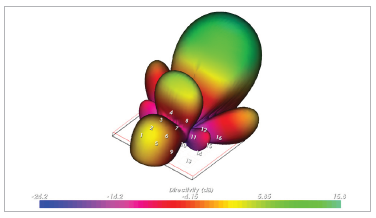

天線分(fēn)析

該軟件可(kě)以執行平面天線和(hé)平面數組的(de)分(fēn)析和(hé)後處理(lǐ)。快(kuài)速的(de) N*Log(N) 求解器技術可(kě)解決以前無法進行整體仿真的(de)大(dà)型複雜(zá)數組。新的(de)峰值天線測量功能支持性能指針,如總輻射功率或輻射模式“切口”上特定極化(huà)方向的(de)功率,該功率是掃頻(pín)的(de)函數或其他(tā)用(yòng)戶定義的(de)掃頻(pín)參數。

設計流程

支持從企業級布局工具 (如 Cadence、Mentor Graphics、Zuken 等) 導入數據庫,并支持諸多(duō)設計自動化(huà)功能,例如将端口自動添加到電磁子電路中,以便大(dà)大(dà)簡化(huà)整個(gè)設計過程中電磁仿真的(de)使用(yòng)。

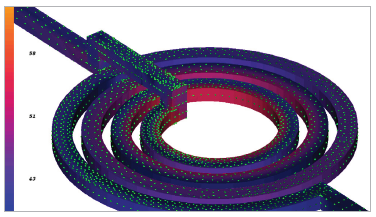

被動建模

使用(yòng)矩量法 (MoM) 技術和(hé)先進的(de)網格劃分(fēn)功能,在單層和(hé)多(duō)層電路上對(duì)傳輸線和(hé)任意結構進行三維平面電磁仿真,進而精确計算(suàn) S、Y 和(hé) Z 參數以及多(duō)層 RFIC、MMIC、PCB、混合電路和(hé)多(duō)芯片模塊 (MCM) 的(de)電流密度。

優化(huà)和(hé)良率

對(duì)被動組件和(hé)複雜(zá)互連結構進行準确的(de)設計診斷,例如良率分(fēn)析和(hé)優化(huà),撷取電路拓撲的(de)真實耦合和(hé)寄生效應,這(zhè)些電路拓撲通(tōng)過基于規則的(de)形狀修改器 / 特征清除功能進行參數化(huà)和(hé) / 或定義。

可(kě)視化(huà)

直接在經過分(fēn)析的(de)結構上将電流和(hé)電場(chǎng)強度用(yòng)顔色标注,以深入了(le)解組件行爲以及潛在的(de)設計失效原因。

應用(yòng)和(hé)技術

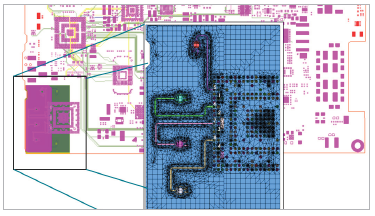

芯片系統

AWR AXIEM 軟件可(kě)以輕松分(fēn)析芯片上被動結構、傳輸線、互連結構、過孔和(hé) MMIC 封裝。爲厚金屬提供支持時(shí),需要創建擠壓平面幾何形狀的(de)三維網格,同時(shí)準确計算(suàn)所有表面上的(de)所有 x、y 和(hé) z 定向電流,這(zhè)是 III-V 和(hé)矽 MMIC / RFIC 設計的(de)先決條件,此類設計依賴于電路 / 電磁協同仿真,以實現嵌入式寄生參數提取和(hé)設計驗證。藉助分(fēn)層電磁 / 電路協同仿真,設計人(rén)員(yuán)可(kě)以進行原位電磁分(fēn)析,在下(xià)線前撷取并糾正有害的(de)寄生耦合和(hé)諧振。

封裝與電路闆

AWR AXIEM 軟件中基于布局的(de) PCB 設計流程支持對(duì)整個(gè)射頻(pín)信号路徑進行精确仿真。電路 / 系統和(hé)電磁協同仿真可(kě)對(duì)表面貼裝元件、互連傳輸線以及嵌入式和(hé)分(fēn)布式被動組件進行完整的(de) PCB 分(fēn)析以及電磁驗證,确保一次設計成功率。通(tōng)過 PCB 導入向導将 PCB 布局工具 (例如 Cadence Allegro® 技術) 中的(de) IPC-2581 (Gerber 或 ODB++) 文件導入 AWR 軟件,即可(kě)實現電磁驗證。藉助強大(dà)的(de)編輯功能,可(kě)以進行快(kuài)速、準确和(hé)高(gāo)效的(de)電磁分(fēn)析。

天線

現如今,5G 和(hé) IoT 智能設備的(de)射頻(pín)設計人(rén)員(yuán)需要使用(yòng)專業的(de)仿真和(hé)優化(huà)技術來(lái)開發具有高(gāo)增益、單頻(pín)帶或多(duō)頻(pín)帶以及寬帶頻(pín)率範圍的(de)小型嵌入式天線。AWR AXIEM 軟件可(kě)助力工程師設計、優化(huà)和(hé)整合天線 / 數組,同時(shí)提供強大(dà)的(de)電磁技術來(lái)仿真天線指針參數,例如增益、回波損耗、輻射效率和(hé)電流,并實現二維 / 三維遠(yuǎn)場(chǎng)天線方向圖的(de)可(kě)視化(huà)。