By Ken Willis, Cadence

高(gāo)效的(de)互連提取

一旦物(wù)理(lǐ) layout 完成(或者至少串列鏈路差分(fēn)對的(de)佈線完成),就可(kě)以進行佈局後驗證。需要決定使用(yòng)多(duō)大(dà)的(de)頻寬進行模型提取。為了(le)評估這一點,需要考慮通(tōng)過鏈路傳遞的(de)信號。 PCI Express Gen 4 的(de)規格是指上升時間約為 22ps,測量值為 10% 至 90%。將上升時間與信號頻寬相關聯的(de)經典運算(suàn)式是:

BW (GHz) =350 / Trise (ps)

對於 PCI Express Gen 4 來說,我們首先考慮的(de)是至少 16 GHz 的(de)信號頻寬,並且如果考慮均衡因素可(kě)能會更高(gāo)。大(dà)多(duō)數工程師會堅持數倍於資料速率的(de)最小頻寬,這樣就處於 30 至 50 GHz 的(de)範圍內。因此,為了(le)精確,需要全波3D電磁場求解器,特別是針對複雜的(de)非平面結構(如耦合過孔)。所以最初的(de)傾向是為這些類型的(de)串列鏈路部署全波三維提取技術。

問題在於計算(suàn)的(de)時間。正如前面所討論的(de)那樣,在設計過程中,詳細的(de)互連提取的(de)關鍵在佈線後。而設計週期的(de)最後通(tōng)常是最具時間挑戰性的(de),因為需要長時間的(de)計算(suàn)。儘管從精確的(de)角度來看複雜過孔結構需要 3D 全波方法,但是對於長而均勻的(de)傳輸線,如 PCB 中的(de)走線,就計算(suàn)得(de)太慢(màn)了(le)。對於這些結構來說,快(kuài)速 2D 方法運行效果還可(kě)以,所以在提取引擎方面存在一個基本衝突。

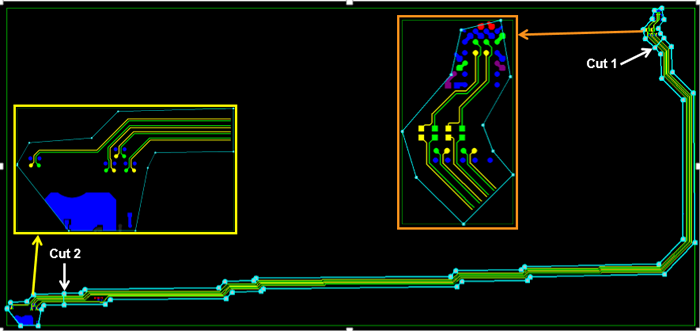

最有效的(de)技術是將兩種方法結合起來,為您提供「全方位的(de)需求」,同時將更快(kuài)、更簡單的(de)方法部署到長而均勻的(de)傳輸線結構中。這通(tōng)常被稱為「切割和(hé)縫合」方法,其中根據所發現的(de)特定互連結構,將要提取的(de)整個互連結構分(fēn)解成不同的(de)區域。具有 3D 結構的(de)區域,如過孔,被標記為全波引擎解決方案,而具有長而均勻傳輸線的(de)區域用(yòng) 2D 技術解決。

將互連分(fēn)成多(duō)個區域進行切割和(hé)縫合

最終的(de)結果組合成一個最終的(de)S參數,就像整個網路都是由全波引擎提取的(de)。這種技術的(de)優點是提供了(le)全波精度,同時,提供的(de)解決方案時間比單用(yòng) 3D 全波求解器提取整個網路的(de)時間要快(kuài)一個數量級(或更多(duō))。

此時,可(kě)將詳細的(de)互連模型插回模擬測試平臺進行佈局後驗證,取代預佈局階段開發的(de) PCB 走線和(hé)過孔模型。

相關視頻

|

|---|

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」