在 PCB 設計界有種說法:高(gāo)速設計已成為部分(fēn) PCB 設計工程師的(de)關注點,並且即將成為所有 PCB 工程師的(de)關注點。自 TTL 以及更快(kuài)的(de)邏輯系列問世,工程師發現簡單的(de) PCB layout 佈局不足以保持訊號完整性。佈局不當時,這些高(gāo)速系統會出現特殊的(de)訊號完整性問題。

對於資料速率適中、開關時間達奈秒量級或更快(kuài)的(de)系統,進行高(gāo)速設計時,每一位工程師均應認真考慮訊號完整性設計。這些高(gāo)速設計技術旨在確保不會出現能導緻高(gāo)誤碼率的(de)偽缺陷訊號,整個電路闆上的(de)時脈流和(hé)串列或平行資料保持同步,並且 PCB 長走線中的(de)傳輸線效應得(de)到抑制。

由於許多(duō)高(gāo)速系統都整合了(le)無線功能或連接了(le)外部類比系統,接地設計和(hé)疊層設計同樣很重要。高(gāo)速設計的(de)這些方面會影(yǐng)響電磁相容性要求和(hé)接地要求,因此工程師應精心設計其疊層。正確的(de)疊層和(hé)接地策略將有助於系統透過電磁相容性檢查、抑制電磁幹擾,並確保這些混合訊號系統中的(de)訊號完整性。

高(gāo)速 PCB 設計的(de)關鍵

考慮高(gāo)速設計時,大(dà)多(duō)數工程師都會想到為系統的(de)資料速率設置一個臨界值。實際上,資料傳輸速率並不能決定特定電路闆的(de)運行速度。相反,在特定系統中,訊號上升時間才是決定其運行速度的(de)首要因素。這就意味著,即使電路闆的(de)資料速率較低(低於 1 Mbps),但如果電路闆的(de)訊號上升時間很短,則仍需要高(gāo)速設計技術。

訊號上升時間對訊號完整性有三個方面的(de)影(yǐng)響:串擾、傳輸線效應 以及輻射電磁幹擾。這些訊號完整性問題與相鄰訊號線之間的(de)寄生電容和(hé)電感以及走線的(de)特性阻抗有關。資料速率非常高(gāo)的(de)系統對邏輯器件在導通(tōng)和(hé)截止狀態之間轉換的(de)速率要求高(gāo)很多(duō)。上升時間愈短,串擾和(hé)振鈴效應便更強,互連線也(yě)更有可(kě)能成為傳輸線。

這就導緻,對於確保走線能夠不受串擾和(hé)電磁幹擾的(de)影(yǐng)響,並抑制傳輸線效應,佈線策略、阻抗受控設計以及合理(lǐ)的(de)疊層設計十分(fēn)重要。在更複雜的(de)系統中,朝向高(gāo)速設計的(de)互連設計策略能確保訊號完整性,並抑制外部輻射產生的(de)電磁幹擾。

高(gāo)速互連設計

電路闆中的(de)互連線在電路闆上傳輸高(gāo)速訊號,其設計應能抑制或消除常見的(de)訊號完整性問題。訊號完整性設計考慮,尤其是互連設計,涉及高(gāo)速 layout 期間有關阻抗匹配的(de)阻抗受控佈線、合理(lǐ)的(de)疊層設計、長度匹配容差以及終端網路設計。

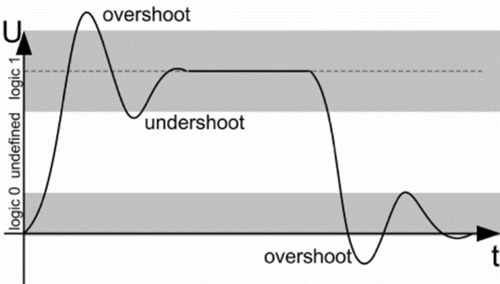

過衝和(hé)下(xià)衝是高(gāo)速設計中可(kě)能出現的(de)訊號完整性問題。

互連設計也(yě)與疊層設計有關,因為疊層可(kě)以實現電磁幹擾屏蔽、確定走線的(de)特性阻抗、影(yǐng)響走線之間的(de)串擾,並提高(gāo)系統通(tōng)過電磁相容性測試的(de)機率。所有這些問題都會影(yǐng)響整個電路闆的(de)訊號完整性,以及是否能夠在電路闆中實現阻抗受控佈線。

高(gāo)速設計中的(de)訊號完整性考量

鑒於高(gāo)速電路闆中可(kě)能出現的(de)所有訊號完整性問題,在 PCB 的(de) layout 階段需要考慮一些重要的(de)設計技術。不良的(de) layout 甚至讓人(rén)無法找到問題的(de)根源。因此,在進行高(gāo)速 PCB 設計時,可(kě)考量以下(xià)幾點。

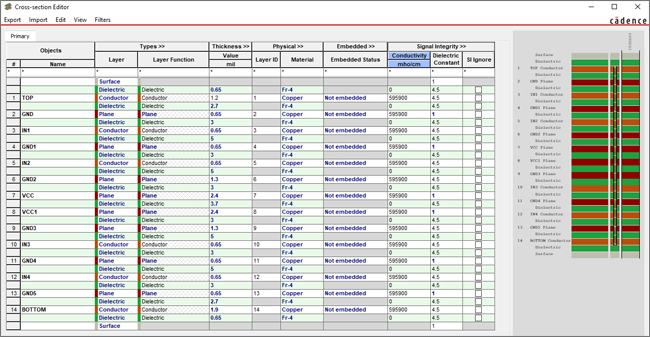

高(gāo)速設計中的(de) PCB 疊層

在高(gāo)速設計中,疊層有許多(duō)功能,因此是訊號完整性設計中需要考慮的(de)一個重要因素。迄今為止,設計具有單端走線的(de)多(duō)層闆時,確保訊號完整性的(de)最常用(yòng)方法是直接將訊號線佈置在接地平面上。走線可(kě)以穿過內層,但最好將內部訊號層佈置在實心的(de)鋪銅平面之間,以防止串擾並保護這些走線免受外部電磁幹擾。利用(yòng)接地平面提供的(de)屏蔽作用(yòng)也(yě)有助於通(tōng)過電磁相容性檢查。

如果除高(gāo)速數位系統外,電路闆還具有一些類比功能,則需要仔細劃分(fēn)電路闆的(de)數位和(hé)類比部分(fēn),避免類比訊號幹擾數位系統,反之亦然。類比部分(fēn)內的(de)類比走線也(yě)必須仔細佈置,防止出現同樣的(de)訊號完整性問題,這些問題可(kě)能會影(yǐng)響數位訊號。

高(gāo)速設計的(de)疊層示例

高(gāo)速設計中的(de)傳輸線效應

真正決定電路闆中的(de)某些走線是否應設計成阻抗匹配傳輸線的(de)因素是電源和(hé)負載之間互連線的(de)長度。當訊號沿某條走線傳輸所需的(de)時間大(dà)約超過訊號上升時間的(de)四分(fēn)之一時,這條走線可(kě)以設計成傳輸線。電源和(hé)走線之間,或負載和(hé)走線之間的(de)阻抗不匹配會導緻訊號反射。

電源處的(de)訊號反射將訊號回傳到積體電路封裝,但高(gāo)速設計中通(tōng)常忽略了(le)這點,因為驅動器中的(de)電晶體結構阻斷了(le)反射回積體電路的(de)訊號。因其會導緻欠阻尼走線 (underdamped trace) 中產生振鈴,負載上的(de)訊號反射更為重要。振鈴 (Ringing) 是指走線中暫態訊號以其固有頻率振盪時產生的(de)暫態振盪。在這種情況下(xià),負載上的(de)串聯端接電阻對於走線減振和(hé)振鈴抑制的(de)作用(yòng)非常重要。

防止高(gāo)速走線中出現時脈偏移 (Clock Skew) 和(hé)訊號偏移 (Signal Skew)

高(gāo)速時脈和(hé)訊號設計需要在一定的(de)允許偏差範圍內對一組訊號的(de)走線進行精確的(de)長度匹配。將訊號發送到負載部件時,在導通(tōng)和(hé)截止狀態之間切換需要特定的(de)時間。平行傳輸資料的(de)走線需要精確匹配長度,以確保所有訊號同時到達負載。同理(lǐ),傳輸串列和(hé)平行資料流程的(de)走線必須與時脈訊號線的(de)長度匹配,以確保負載的(de)積體電路能夠適時切換。由於長度不匹配而造成的(de)任何時序偏差都會增加系統中的(de)誤碼。

高(gāo)速設計的(de)長度匹配

寄生電容 (Parasitic Capacitance) 和(hé)電感 (Inductance) 對訊號完整性的(de)影(yǐng)響

PCB 上的(de)每一個導電元件都有一些寄生電感,而多(duō)根導線之間有一些寄生電容。寄生效應無法避免,但可(kě)以透過創造性的(de)設計技術降低其對串擾的(de)影(yǐng)響。透過寄生耦合降低串擾這一主要方法是將走線佈置到非常靠近其參考平面的(de)位置,或者將走線佈置成差動對 (differential pairs)。

對於上升速率非常快(kuài)(即 10 Gbps 或更高(gāo))的(de)系統,寄生電容和(hé)電感可(kě)能會成為主要問題,即使在設計為阻抗匹配傳輸線的(de)走線上也(yě)是如此。由於寄生效應,走線幾何形狀的(de)變化(huà)或不對稱會在整個走線中造成阻抗不連續,這可(kě)能會在沿走線各點處造成反射。這個問題的(de)解決方案與上述佈線策略有關。應精確匹配走線的(de)長度並安排其佈線,從而使整個走線上的(de)寄生效應保持一緻,這要求整條互連線上的(de)走線間距和(hé)環路面積保持一緻。

終端阻抗匹配網路

匹配負載走線的(de)整體阻抗時,有多(duō)種終端網路可(kě)選用(yòng)。阻抗匹配能消除負載上的(de)訊號反射,而最好的(de)策略便是同時使用(yòng)這兩種策略。在負載上放置一個適當的(de)串聯端接電阻便可(kě)以透過有效降低走線的(de)振幅來抑制振鈴,但這同時也(yě)會改變阻抗的(de)不匹配值。而放置終端網路能確保負載處的(de)走線和(hé)串聯電阻組合的(de)阻抗匹配。

整合 PCB 設計與分(fēn)析

高(gāo)速設計中,防止出現訊號完整性問題的(de)關鍵在於 PCB 設計軟體中要具有正確的(de) layout、佈線和(hé)疊層管理(lǐ)功能。結合了(le)訊號完整性和(hé)電路分(fēn)析工具,便具備了(le)高(gāo)速設計中解決訊號完整性問題所需的(de)一切。

使用(yòng) Allegro® PCB Designer 軟體完成的(de)其中一個高(gāo)速設計

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」