By Vincent Wu, Graser

【 電路可(kě)靠度設計 】系列專題 主要探討電路設計上常見的(de)可(kě)靠度問題和(hé)如何在設計創建初期應用(yòng)一些自動驗證分(fēn)析工具,幫助設計開發團隊降低在可(kě)靠度需求上所花費的(de)時間與人(rén)力,確保最終產品能供提供符合市場所需性能和(hé)產品壽命。 該系列共兩篇,第一篇聚焦於電路邏輯檢測,第二篇內容則著重在電應力分(fēn)析。

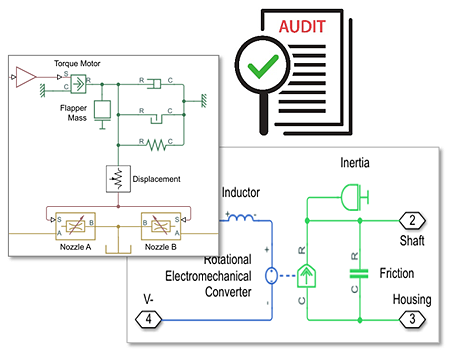

首篇內容將詳解如何設定和(hé)運用(yòng)電路邏輯檢測 (Audit Schematic) 功能自動識別一般難檢測到的(de)電路設計錯誤,並針對 52 電路檢查規則提供圖解範例,以期用(yòng)最直觀的(de)方式帶給使用(yòng)者印象深刻的(de)操作體驗。

電路可(kě)靠度面面觀

當電子設計日益複雜,對產品可(kě)靠度的(de)要求也(yě)越來越高(gāo),而產品可(kě)靠度的(de)好與壞絕對是消費者考慮是否購買該產品的(de)先決考量。除了(le)消費型商品,工業 / 汽車 / 航空 / 軍事 --- 這些領域相關產品對可(kě)靠度 (Reliability) 的(de)要求更高(gāo),規範更嚴謹。 為了(le)達到這樣的(de)要求,投入的(de)時間與人(rén)力資源相對的(de)是數倍乃至數十倍之多(duō)。

然而產品設計的(de)整體可(kě)靠性取決於多(duō)個因素,例如 元件公差、溫度、靈敏度 等等。那在什(shén)麼情況下(xià),我們會定義一個產品設計的(de)可(kě)靠度不足。舉幾個簡單的(de)例子來說:

1. |

將 1/4 Watt 的(de)電阻器配置在 1/2 Watt 的(de)電路節點上工作 |

|---|---|

2. |

讓一個耐壓規格為 50 V 的(de)電容器工作在 100 V 的(de)電壓下(xià) |

3. |

一個 100 ohm 的(de)電阻器在 60 度的(de)溫度下(xià),電阻值變為 115 ohm |

4. |

當在較高(gāo)溫度下(xià)工作時,1 Watt 規格的(de) BJT 功率處理(lǐ)能力下(xià)降至 0.75W |

當然還有其他(tā)許多(duō)可(kě)靠度不足的(de)情況,但就以上述這幾個簡單的(de)例子為情境,在線路複雜且零件數量龐大(dà)的(de)設計上要找出這些錯誤也(yě)並不容易,特別是在人(rén)工手動完成的(de)情況下(xià),不僅需耗費大(dà)量的(de)工時且正確性往往也(yě)不如預期。 若您正在進行包含數千、數萬個零組件的(de)大(dà)型設計專案時,逐頁手動識別和(hé)解決設計問題更會是一場可(kě)怕的(de)噩夢。 而 電路圖繪製 是整個電子系統設計架構的(de)地基,既便是一個簡單錯誤都會因修改讓整個設計週期延長,費時耗力,更遑論若在生產階段才發現而須返工修正設計,造成整個專案延遲。

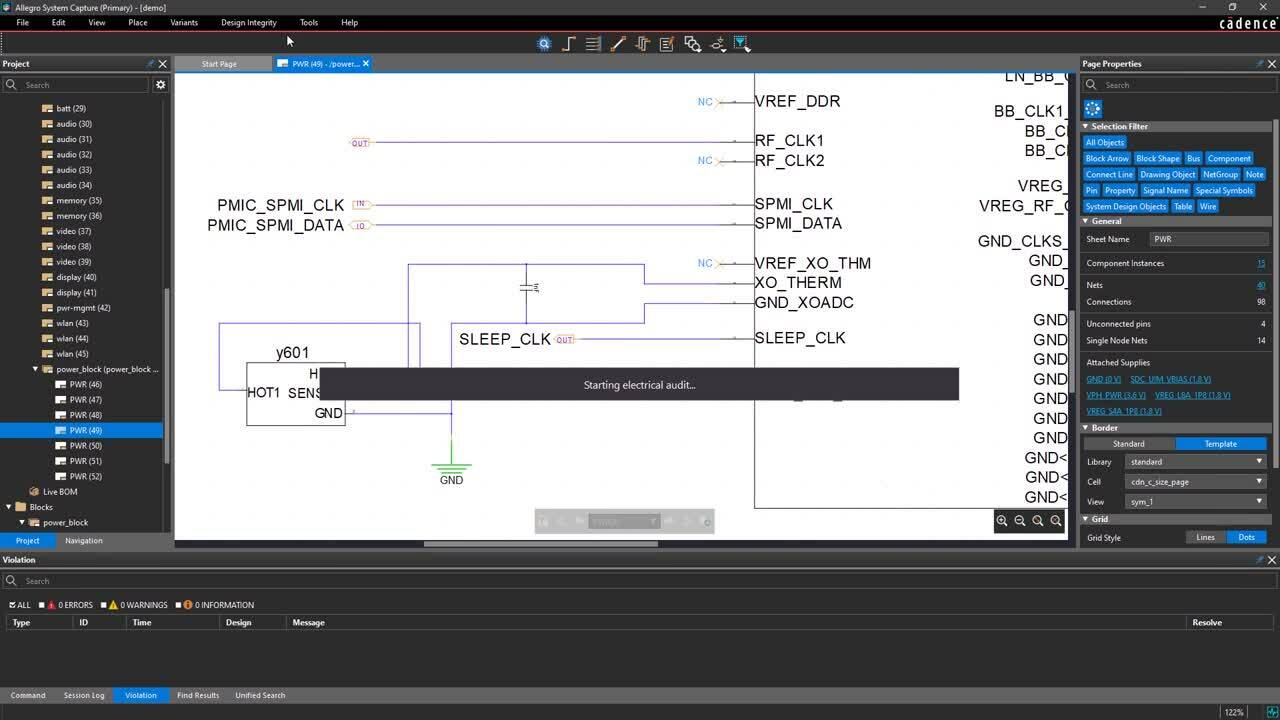

Cadence Allegro System Capture 17.4 的(de) 電路邏輯檢測 (Audit Schematic) 功能,運用(yòng)進階的(de)電路邏輯檢查規則,幫助使用(yòng)者找出當前 DRC (Design Rule Check) 設計規則檢查工具無法查出的(de)電路設計錯誤,例如: 電解電容極性連接錯誤、將耐壓 6.3V 的(de)陶瓷電容接到 12V 的(de) Power Rail 上…等錯誤,這也(yě)是 Audit Schematic 功能的(de)獨到之處。 Allegro System Capture 17.4 在 2021 年 1 月(yuè)發佈了(le) QIR2 版本,此版本新增了(le) 20 條電路檢查規則在 Audit Schematic 功能當中,加上 QIR1 版本的(de) 32 條電路檢查規則,你可(kě)以輕鬆配置規則、參數或電源和(hé)接地部分(fēn)的(de)設置,無需任何 SPICE 或專有模型即可(kě)輕鬆進行設計審核。不論你處於設計週期的(de)哪個階段,都可(kě)以簡單地為任何規則調整報告級別並保存更改,且隻需單擊一下(xià)就可(kě)以開始電路檢測。 讓 Audit Schematic 自動化(huà)檢查電路設計的(de)守備範圍更全面,協助你毫不費力地找出潛藏的(de)設計風險。

Audit Schematic 獨賣特點搶先看

( 中文字幕 / 英文配音(yīn) )

溫馨提醒 : 可(kě)點擊影(yǐng)片下(xià)方設定圖示, 在 Captions 中選擇國語, 開啟中文字幕觀看

實例 DEMO -常見電路檢測問題

差動對訊號缺失、電容 / 電感短路、SCL / SDA 未連接等問題,你是否常遇到但卻很難立即發現修正呢(ne)?

下(xià)方影(yǐng)片先帶你快(kuài)速瞭解如何用(yòng) Allegro 的(de) 電路邏輯檢測 (Audit Schematic) 功能,快(kuài)篩修正這些常見但又難以立即發現的(de)電路問題!

1. 差動對 (Differential Pair) 相關問題檢測看點

可(kě)檢測項目:

|

差動對缺少 TX 或 RX 訊號 |

|---|---|

|

差動對 Net 隻有單端連接至零件 Pin 腳 |

|

差動對的(de) Net 未連接到其它 Net 或零件 Pin 腳 |

|

差動對的(de) Net 其極性與連接到的(de)零件 Pin 腳不匹配 |

|

差動對的(de)零件 Pin 腳其極性與連接到的(de)零件 Pin 腳不匹配 |

|

二顆或多(duō)顆 IC 的(de) TX pin 連接到相同名稱的(de)差動對 Net |

|

兩個訊號 Net 被定義為 Differential pair,但這兩個訊號 Net 不在同一顆 IC 上 |

範例影(yǐng)音(yīn) -〈 差動對缺少 TX 或 RX 訊號 〉檢測:

溫馨提醒:播放前可(kě)按下(xià)方設定圖示調整畫質至 1080p HD,以獲得(de)最佳觀看體驗。

2. 短路相關問題檢測看點

可(kě)檢測項目:

|

電容兩端短路至相同 Net |

|---|---|

|

二極體兩端短路至相同 Net |

|

電感兩端短路至相同 Net |

|

電阻兩端短路至相同的(de) Net |

範例影(yǐng)音(yīn) -〈 電容兩端短路至相同 Net 〉檢測:

溫馨提醒:播放前可(kě)按下(xià)方設定圖示調整畫質至 1080p HD,以獲得(de)最佳觀看體驗。

3. SCL / SDA 等未連接問題檢測看點

可(kě)檢測項目:

|

IC 上的(de) SCL Pin 腳未連接上拉電阻 |

|---|---|

|

IC 上的(de) SDA Pin 腳未連接上拉電阻 |

|

輸入屬性的(de) IC Pin 腳未連接到其它 Net 或零件 Pin 腳 |

|

電源 / 接地屬性的(de) IC Pin 腳未連接到電源 / 接地 Net |

|

Net 兩端未連接到其它 Net 或零件 Pin 腳 |

範例影(yǐng)音(yīn) -〈 IC 上的(de) SCL Pin 腳未連接上拉電阻 〉檢測:

溫馨提醒:播放前可(kě)按下(xià)方設定圖示調整畫質至 1080p HD,以獲得(de)最佳觀看體驗。

※ 【 電路可(kě)靠度設計 】下(xià)一期預告:零件電應力分(fēn)析全攻略